Reports in Electron Physics 2000/24 Espoo, September 2000

## Ultrahigh Vacuum Plasma Oxidation in the Fabrication of Ultrathin Silicon Dioxide Films

Tero Majamaa

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission for public examination and debate in Auditorium S4 at Helsinki University of Technology (Espoo, Finland) on the 20th of October, 2000, at 12 o'clock noon.

Helsinki University of Technology Department of Electrical and Communications Engineering Electron Physics Laboratory

Teknillinen korkeakoulu Sähkö- ja tietoliikennetekniikan osasto Elektronifysiikan laboratorio Distribution: Helsinki University of Technology Electron Physics Laboratory P.O. Box 3000 FIN-02015 HUT Finland Tel. +358-9-451 2322 Fax. +358-9-451 5008

ISBN 951-22-5146-9 ISSN 0781-4984

Otamedia Oy Espoo 2000

#### Abstract

This thesis discusses the fabrication and characterization of ultrathin insulator films. These are essential for nanoscale semiconductor device fabrication. When the insulator layer thickness is only a few times the molecule diameter, it is crucial that both film homogeneity and the insulator/semiconductor interface quality are as high as possible. The small dimensions must also be taken into account in characterization, because the established measurement techniques and analyses used in more traditional MOS characterization are not necessarily valid any more.

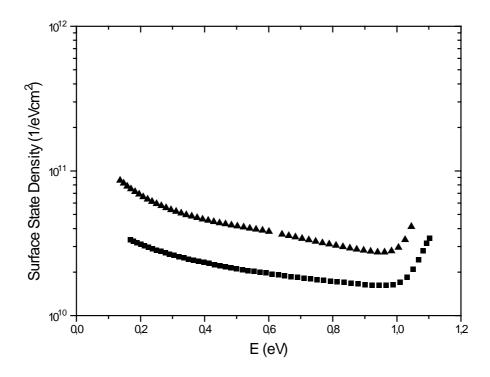

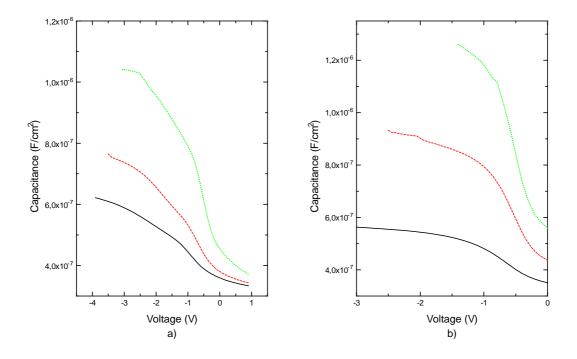

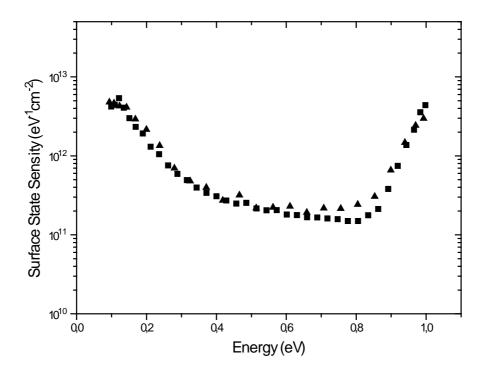

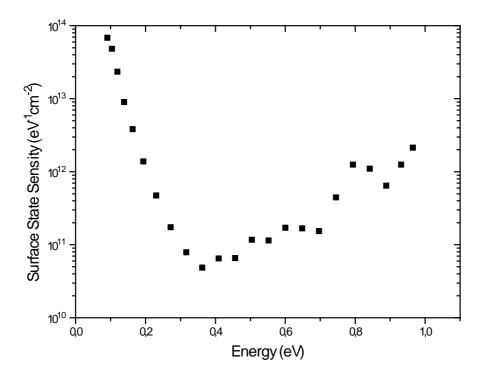

In this work, the metal/silicon dioxide/silicon structure (especially oxide and oxide/semiconductor interface quality) and various silicon dioxide fabrication methods are discussed. The focus in the experimental work is on the studying the plasma assisted oxidation of silicon in an ultra high vacuum chamber and on characterizing the fabricated films. Some of the film properties are found to be excellent: interface smoothness is of a very high quality and interface state densities are low (10<sup>11</sup> eV<sup>-1</sup>cm<sup>-2</sup> or lower in the mid-gap) even without any annealing. Process control also seems to be good, as is the breakdown field. The oxide charge, however, is quite high. This may cause considerable harm. One of the consequences is an increased leakage current. This also significantly decreases the device life time by increasing current generated defects. In the annealing experiments carried out, the oxide charge was seen to decrease, indicating that the quality of the silicon dioxide films can be significantly improved by optimization of the thermal treatments.

The molecular beam epitaxy system used in processing is designed mainly for research purposes, offering possibility to gain much information about the oxidation process itself. Other, and cheaper, thermal oxidation procedures have in recent years already been developed to a very high level, which means that the process developed is not necessarily the best choice for conventional IC manufacturing purposes. It offers, however, useful applications for research into silicon-based nanostructures, such as silicon/silicon dioxide heterostructures.

Keywords: Ultrathin silicon dioxide, ultrahigh vacuum, plasma oxidation

## Preface

This thesis for the degree of Doctor of Science in Technology was mainly researched at the Helsinki University of Technology Electron Physics Laboratory during the years 1995 - 1999. I would specially like to thank Professor Juha Sinkkonen who has supervised my work. I also thank the other personnel of the Electron Physics Laboratory, where I had the great privilege of working from 1990 to 1998. I owe a special debt of gratitude to the personnel of the Microelectronics Centre at the Helsinki University of Technology and VTT Electronics for the use of their clean room facilities and equipment as well as for many helpful conversations and invaluable advise.

I am also grateful to the Academy of Finland for the generous financial support they granted to the research project during my years at the Electron Physics Laboratory as well as for the encouragement of my co-workers and superiors since I started at the Academy.

Tero Majamaa

# List of Symbols

### $a, A, a_0, B, G_0, k, l_0, r, \tau$

|              | constants                                                 |

|--------------|-----------------------------------------------------------|

| Α            | area                                                      |

| Ai           | Airy function                                             |

| В            | susceptance                                               |

| С            | capacitance                                               |

| $C_0$        | oxygen concentration on sample surface                    |

| $C_1$        | concentration of oxidizing molecules                      |

| $C_{ m gr}$  | growth site concentration                                 |

| $C_{HF}$     | high frequency capacitance                                |

| $C_{it}$     | interface trap state capacitance                          |

| $C_{LF}$     | low frequency capacitance                                 |

| $C_{\rm OX}$ | oxygen concentration on silicon dioxide surface           |

| $C_{\rm S}$  | oxygen concentration at silicon/silicon dioxide interface |

| $C_{ox,s}$   | saturated oxide capacitance                               |

| $C_{mos}$    | MOS capacitance                                           |

| $C_{\rm SI}$ | oxygen concentration on silicon surface                   |

| D            | diffusion coefficient                                     |

| $D_{it}$     | surface state density                                     |

| $d_0$        | initial thickness of the silicon dioxide layer            |

| $d_{cr}$     | critical thickness of a silicon dioxide layer             |

| $d_{ox}$     | oxide thickness                                           |

| $d_{sc}$     | depletion region length                                   |

| Ε            | energy, electric field                                    |

| $E_A$        | activation energy                                         |

| $E_c$        | conduction band energy                                    |

| $E_{f}$      | Fermi energy                                              |

| $E_g$        | energy bandgap                                            |

| $E_{n0}$     | electron ground state energy in potential well            |

| $E_{ox}$     | electric field in the silicon dioxide                     |

| $E_{p0}$     | hole ground state energy in potential well                |

| $E_s$        | electric field at the silicon/silicon dioxide interface   |

| $E_{v}$      | valence band energy                                       |

|--------------|-----------------------------------------------------------|

| F            | flux, modulation factor                                   |

| f            | frequency                                                 |

| (g)          | gas                                                       |

| G            | conductance                                               |

| $G_{mos}$    | leakage conductance through MOS structure                 |

| h            | Planck constant                                           |

| i            | imaginary unit                                            |

| J            | current density                                           |

| $J_{\rm DT}$ | current density in direct tunneling                       |

| $J_{ m FN}$  | current density in Fowler-Nordheim tunneling              |

| k            | wave number                                               |

| $k_B$        | Boltzmann coefficient                                     |

| т            | mass                                                      |

| $m^*$        | effective mass                                            |

| $n_i$        | intrinsic carrier concentration                           |

| $n_s$        | electron density at the silicon/silicon dioxide interface |

| $N_A$        | acceptor density                                          |

| $N_A^-$      | density of ionized acceptors                              |

| $N_D$        | donor density                                             |

| $N_D^+$      | density of ionized donors                                 |

| Nox          | oxide charge density                                      |

| $N_s$        | silicon/silicon dioxide interface charge density          |

| р            | hole density                                              |

| $p_s$        | hole density at the silicon/silicon dioxide interface     |

| Р            | pressure                                                  |

| $P_0$        | reference pressure                                        |

| q            | unit charge                                               |

| Q            | charge                                                    |

| r            | relative sticking coefficient                             |

| R            | resistance                                                |

| $R_{it}$     | interface trap state resistance                           |

| $R_s$        | series resistance                                         |

| (s)          | solid                                                     |

| t                   | time                                               |

|---------------------|----------------------------------------------------|

| Т                   | temperature                                        |

| V                   | potential, voltage                                 |

| $V_{bi}$            | built in voltage                                   |

| $V_{fb}$            | flat band voltage                                  |

| $\Delta V_{fb}$     | flat band voltage shift                            |

| $V_g$               | gate voltage                                       |

| V <sub>ox</sub>     | voltage across the oxide                           |

| $V_s$               | potential at the silicon/silicon dioxide interface |

| $V_{trap}$          | potential of a interface trap level                |

| X                   | reactance                                          |

| Y                   | admittance                                         |

| $Y_m$               | measured admittance                                |

| Ζ                   | impedance                                          |

| $Z_m$               | measured impedance                                 |

|                     |                                                    |

| δ                   | Dirac delta function                               |

| ε                   | dielectric constant                                |

| $\epsilon_{Si}$     | dielectric constant of silicon                     |

| $\epsilon_{Ox}$     | dielectric constant of silicon dioxide             |

| $\Phi_{\mathrm{M}}$ | barrier height at metal/oxide interface            |

| $\Phi_{Si}$         | barrier height at silicon/oxide interface          |

| ρ                   | charge density                                     |

| ω                   | angular frequency                                  |

|                     |                                                    |

## Abbreviations

| ALCVD | Atomic Layer CVD          |

|-------|---------------------------|

| ALD   | Atomic Layer Deposition   |

| ALE   | Atomic Layer Epitaxy      |

| CMOS  | Complementary MOS         |

| CV    | Capacitance - Voltage     |

| CVD   | Chemical Vapor Deposition |

| FET    | Field Effect Transistor                           |

|--------|---------------------------------------------------|

| FN     | Fowler-Nordheim (tunneling)                       |

| IC     | Integrated Circuit                                |

| Imag   | imaginary part                                    |

| LF     | Low Frequency                                     |

| LPCVD  | Low Pressure CVD                                  |

| MBD    | Molecular Beam Deposition                         |

| MBE    | Molecular Beam Epitaxy                            |

| MOS    | Metal Oxide Semiconductor                         |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| NMOS   | n-channel MOS                                     |

| NTP    | Normal Temperature and Pressure                   |

| PECVD  | Plasma Enhanced CVD                               |

| PEE    | Plasma Enhanced Evaporation                       |

| PMOS   | p-channel MOS                                     |

| Real   | real part                                         |

| RF     | Radio Frequency                                   |

| RHEED  | Reflection High Energy Electron Diffraction       |

| RPECVD | Remote Plasma Enhanced CVD                        |

| RTD    | Resonance Tunneling Diode                         |

| RTA    | Rapid Thermal Annealing                           |

| RTO    | Rapid Thermal Oxidation                           |

| SILC   | Stress Induced Leakage Current                    |

| SOI    | Silicon on Insulator                              |

| TEM    | Transmission Electron Microscopy                  |

| UHV    | Ultra High Vacuum                                 |

| UPO    | Ultrahigh vacuum Plasma Oxidation                 |

| XPS    | X-ray Photo emission Spectroscopy                 |

|        |                                                   |

## Contents

| 1 | Int | troduction                                                     |      |  |

|---|-----|----------------------------------------------------------------|------|--|

| 2 | MO  | DS Structure                                                   | 5    |  |

|   | 2.1 | Silicon/Silicon Dioxide Interface                              | 6    |  |

|   | 2.2 | Tunneling, Leakage, Breakdown and Defect Generation            | . 10 |  |

| 3 | Fał | prication of Thin Silicon Dioxide Films                        | . 16 |  |

|   | 3.1 | Cleaning of the Substrate Surface                              | . 16 |  |

|   | 3.2 | Thermal Oxidation                                              | . 19 |  |

|   | 3.2 | .1 Deal-Grove Model                                            | . 24 |  |

|   | 3.3 | Other Fabrication Methods                                      | . 26 |  |

|   | 3.4 | Annealing                                                      | . 29 |  |

| 4 | Ele | ectrical Characterization of Ultrathin Insulators              | . 34 |  |

|   | 4.1 | Oxide Charge                                                   | . 36 |  |

|   | 4.2 | Impedance of Thin Oxide MOS Structure                          | . 37 |  |

|   | 4.3 | Oxide Thickness                                                | . 42 |  |

|   | 4.4 | Surface State Density                                          | . 45 |  |

| 5 | Ult | rahigh Vacuum Plasma Oxidation (UPO)                           | . 49 |  |

|   | 5.1 | Equipment                                                      | . 50 |  |

|   | 5.2 | Electrical Characterization                                    | . 51 |  |

|   | 5.3 | Oxidation Rate                                                 | . 51 |  |

|   | 5.3 | .1 Experiment                                                  | . 52 |  |

|   | 5.4 | Room Temperature Oxidation                                     | . 58 |  |

|   | 5.4 | .1 Experiment                                                  | . 59 |  |

|   | 5.5 | Effect of Oxidation Temperature on the Silicon Dioxide Quality | . 63 |  |

|   | 5.5 | .1 Experiment                                                  | . 63 |  |

|   | 5.6 | The Effect of Post Oxidation Annealing                         | . 68 |  |

|   | 5.6 | .1 Experiment                                                  | . 69 |  |

|   | 5.7 | Evaporation Technique                                          | . 72 |  |

|   | 5.7 | .1 Experiment                                                  | . 73 |  |

| 6 | Co  | nclusions                                                      | . 78 |  |

### **1** Introduction

During 1994 research interests at the Helsinki University of Technology Electron Physics Laboratory started to shift increasingly from III-V compounds towards silicon based devices. With the growing interest to use our molecular beam epitaxy (MBE) system to fabricate silicon devices, it became obvious that, in addition to epitaxial semiconductor layers, it was also necessary to have some thin insulator films. This paved the way to our research on plasma oxidation in ultra high vacuum (UHV)<sup>1,2,3,4</sup>.

Molecular beam epitaxy systems have been used in submicron MOSFET fabrication <sup>5,6</sup>, but these processes usually do not include oxidation in the MBE. There has, however, been some work on cyclotron resonance plasma oxidation in UHV <sup>7</sup> or some other oxidation/evaporation methods <sup>8</sup>, for instance. In our research the aim was to maximize the process purity and the quality of the materials produced by performing the oxidation in an ultra high vacuum MBE system. The use of an MBE system allows for highly accurate growth and there are almost no impurities at all. Our processing equipment also provides the possibility for *in situ* native oxide removal and device processing, which further improves process purity. This process not only allows us to fabricate high quality films, but also makes it possible to get a more reliable picture on the oxidation process on an atomic level.

The main impetus for our research was provided by the growing interest worldwide in silicon/silicon dioxide based nanodevices. The aim has been to fabricate ever smaller and faster devices and circuits. The decrease in the chip area, and by the same token in the processing linewidths, means that the vertical dimensions of the devices also have to decrease. This requires a fabrication method that produces very homogeneous and high quality Si/SiO<sub>2</sub> interfaces and SiO<sub>2</sub> layers with accurately defined thickness. A 50-nm channel length bulk MOSFET would have a 2-nm thick gate oxide for high performance applications. That would give a maximum electric field of 5 MV/cm in the oxide, about half of the breakdown field of good quality bulk oxide <sup>9</sup>. Normal operation of a MOSFET with an ultra-thin direct-tunneling gate oxide was first achieved in November 1995. In an n-MOSFET, with 1.5 nm gate oxide and 100 nm gate length, transconductance above 10 S/cm and current drive above 1 mA/µm was measured at

room temperature <sup>16</sup>. By decreasing the channel length of MOSFET to 80 nm and the oxide thickness to 3.5 nm, cut-off frequencies of about 100 GHz have been reached <sup>9</sup>. Other silicon based devices in which ultrathin oxides are needed include, for instance, memory structures based on silicon nanocrystals <sup>10</sup>.

The tightening of process tolerances in order to satisfy more stringent defect density and reliability requirements poses many difficult challenges. For purposes of fabricating faster sub-micrometer MOSFETs and quantum devices, the thickness of the silicon dioxide layer may be no more than a couple of nanometers. This greatly enhances the impact of surface roughness scattering on drain current and carrier mobility <sup>11</sup>. The surface and the interface have to be flat on an atomic scale. Roughness may also enhance tunneling currents. Furthermore, roughness increases the amount of traps and charge at the interface, creates extra energy states, and leads to local variations in the electric field and in the channel charge. It is widely accepted that low frequency 1/f noise in MOS transistors is due to mobility or charge fluctuations arising from dynamic trapping and detrapping of channel carriers by interface traps.

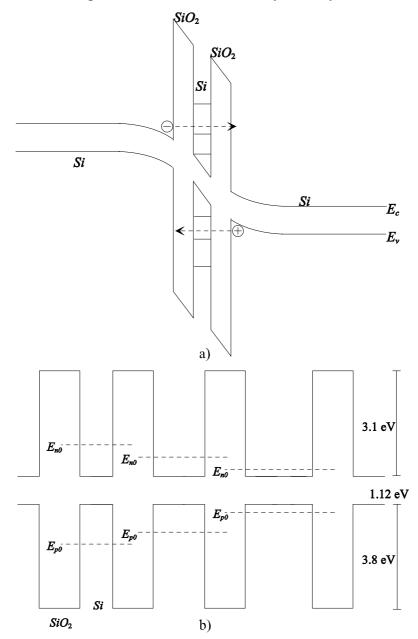

As the dimensions are reduced to the level where quantum effects begin to appear, it also becomes possible to use silicon to fabricate versatile new devices, which could earlier only be made from compound semiconductors. This would mean increased process compatibility and reduced circuit prices. Research so far has produced such innovations as luminescent silicon/silicon dioxide heterostructures, for instance <sup>12</sup>. Because the energy gap in silicon dioxide is above 8 eV and in silicon 1.1 eV and the affinity of silicon is over 3 eV higher than in silicon dioxide (Figure 1.1), the barriers can be much higher and quantum wells much deeper than in III-V heterostructures. This means there can exist more quantum states at the same time, and quantum phenomena can be utilized in room temperature. The state energies can be adjusted by changing the quantum well dimensions.

Research on silicon-based nanodevices has also involved some trials to fabricate resonant tunneling diodes (RTDs), but the resonant effect achieved has not been very strong <sup>13</sup>. The quality of the interface between these two materials is not as good as when using crystalline materials with low lattice mismatch, such as GaAs and AlGaAs. This means that there always exist interface states and consequently there are several

possible states from which and to which the carriers can tunnel. For this reason it is hard to see clear quantum effects. The strongest silicon based photon emission, also, has been reached by using porous or multicrystalline silicon: not silicon/silicon dioxide heterostructures. The origin of this luminescence is not clear, but it might be due to some three dimensional quantum structures, formed by nanocrystals.

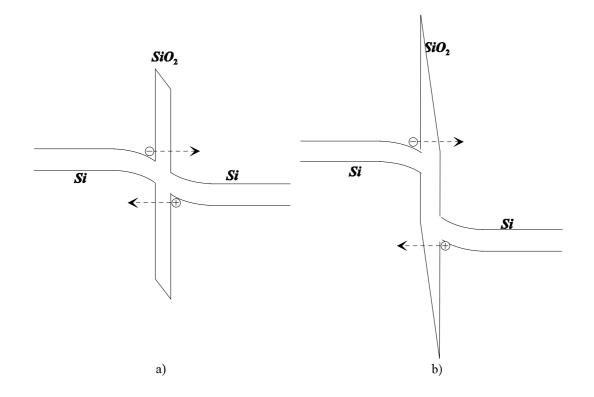

**Figure 1.1** Schematic illustration of energy band structure of a a) RTD b) silicon/silicon dioxide heterostructure.  $E_{p0}$  and  $E_{n0}$  represent the ground state energies in the potential wells.

Another major problem has to do with the fact that silicon dioxide is an amorphous material, and the average distances between silicon atoms in silicon lattice and in silicon dioxide are different. Because of the 'lattice mismatch' it is difficult to grow single

crystalline silicon on top of the oxide without holes through the oxide or in some other way so that the epitaxial layer can come into direct contact with the substrate. After that high temperature treatment is also usually needed to transform multicrystalline material into single crystal. Some experiments have, however, succeeded in growing single crystal silicon on SiO<sub>x</sub>, where the oxygen content is about 20 at.% or less (x < 0.25)<sup>14</sup>. This, of course, means that the oxide properties are changed.

There has been intensive research on the outermost limit of the downscaling of silicon dioxide films. A decrease in device size, and the oxide thickness leads to an increase in the tunneling current. Tunneling can have a significant effect on the transistor operation. The stress induced leakage current (SILC) is considered to be the major limiting factor for the downscaling of tunnel oxides. If the devices operate at elevated temperatures, SILC increases. Present estimates are that the film thickness can not go much below 2.2 nm (1 V supply voltage)<sup>15</sup>. After that the reliability decreases too much. Various fabrication procedures and the set-ups for experimentation result, however, slightly different properties. Device structures can also be modified to improve performance without extended downscaling. One of the ways of tackling the problems occurring in the ultrathin region has, in fact, been to change the MOSFET structure rather than just scale down the dimensions <sup>16</sup>. The drain and source wells can be made deeper, which decreases sheet resistance. Smaller gate decreases leakage current and increases drain current. Nonuniform channel doping in both vertical and lateral directions can be used to minimize the short channel effects, while low temperature CMOS and double gate MOSFETs can potentially lead to the outermost limit of silicon scaling<sup>9</sup>. SOI and SiGe devices offer performance and power advantages over bulk CMOS without channel length scaling. The demands of the rapidly developing semiconductor industry will, however, still require even smaller dimensions and thinner silicon dioxide films.

### **2 MOS Structure**

The fabrication of good quality insulator layers requires a good molecular structure and the complete absence of impurities: there may be no free bonds, traps or other defects that might affect the oxide charge or conductivity. The interface between silicon and silicon dioxide should also be as abrupt as possible, and there should be no interface states. Electron mobility, for instance, has been shown to correlate directly with oxide/channel interface roughness <sup>17</sup>.

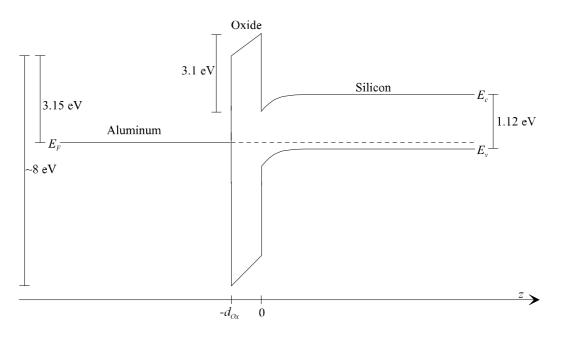

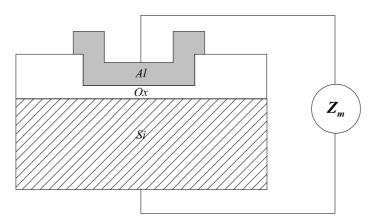

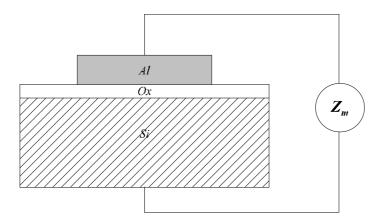

The basic MOS structure (Figure 2.1) consists of a metal (often aluminum) or heavily doped polysilicon layer, insulator (silicon dioxide or silicon dioxide and silicon nitride layers) and doped silicon.

**Figure 2.1** Energy band structure of an aluminum/silicon dioxide/p-type silicon structure with zero bias.

Oxide defects are traditionally divided into four general classes <sup>18</sup>:

- fixed oxide charge

- mobile ionic charge

- interface-trapped charge

- oxide trapped charge

Interface traps communicate directly with the underlying silicon, whereas oxide traps and fixed charge do not. There are also so-called 'border traps' <sup>19</sup>, a term applied to traps lying within about 3 nm of the silicon/silicon dioxide interface and in communication with the silicon. These are near-interfacial oxide traps that can either rapidly or slowly exchange charge with the silicon. They play an important role in determining low frequency (1/*f*) noise levels in MOS transistors. Border traps can act like either interface traps or bulk oxide traps, depending on the bias and the time scale. They include so-called 'slow states' <sup>20</sup>, 'anomalous positive charge' <sup>21</sup> and rechargeable E' centers <sup>22</sup>. It must be noted that all defects in ultrathin oxides may act as border traps, since the film thickness is on the 3-nm scale, or even lower.

Impurities also have an impact on energy band discontinuity at the silicon/silicon dioxide interface  $^{23}$ . They induce changes in the band structure and have been found to bring about a decrease in conduction band off-set and an increase in valence band off-set. The evidence suggests these changes are almost identical in thermal oxide  $^{23}$ . The magnitude of the energy gap is thus not changed, but the bands are bended. The variations in the energy band structure between the bulk oxide and the interface region depend of course on the impurity concentration and the oxide quality. In some conventional dry oxidation experiments (below 800 °C) a typical value for the off-set shift has found to be about 0.2 eV, on both silicon (100) as on silicon (111) surfaces  $^{24,25}$ . This value can be reduced, however, by using ultra clean processes  $^{23}$ .

#### 2.1 Silicon/Silicon Dioxide Interface

Almost all silicon wafers that are used in microelectronics are single crystalline. Silicon dioxide, on the other hand, is amorphous. The average distances between atoms also differ from one another. Once the silicon surface is oxidized, the interface between these two materials can no longer be perfect. The volume per silicon atom in silicon dioxide is about twice that in silicon crystal, which means that silicon atoms are inevitably emitted from the interface to release stress during oxidation <sup>26</sup>. The atomic scale structure of the interface between crystalline silicon and its amorphous oxide

remains controversial <sup>27</sup>. However, a very high degree of perfection has been achieved in practice, which is evidenced by the very low density of defects observed at the interface.

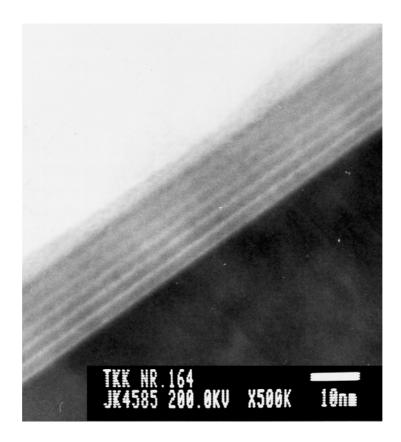

Depending on the oxidation procedure interface roughness between silicon and silicon dioxide layer has been reported to be up to  $1 - 1.6 \text{ nm}^{28,29}$ . Roughness is also affected by surface orientation and film thickness. On (100) surfaces there is less roughness than on (111) surfaces, but it increases with increasing thickness (film thickness 1 nm, roughness about 0.06 nm; film thickness 2 nm, roughness 0.14 nm<sup>30</sup>). On (111) surfaces, however, the range of roughness depends hardly at all on thickness (about 0.3 nm<sup>30</sup>), but the horizontal size of the protrusions increases with film thickness.

Several assumptions have been made about the possible interfacial structure of the silicon/silicon dioxide interface. Non-reacted silicon - silicon bonds have been observed at the interface by means of Auger spectroscopy. On this basis it can be assumed that there is at least one monolayer of silicon dioxide into which some amorphous silicon is mixed <sup>31</sup>. Auger analysis has also shown that there is an interface layer in which there is less oxygen and usually some silicon clusters <sup>32</sup>. The same effect has been reported on the basis of ellipsometric measurements <sup>33</sup>, where the change in the refractive index shows lower oxygen contents. There have also been made some measurements of the structural nature of silicon/silicon dioxide interface (oxide thickness 5 - 27 nm) by using infrared absorption associated with oxygen vibrational modes <sup>29</sup>. These measurements indicated that the interface difference is mainly due to stoichiometric changes, not to stress or densification.

The interface region width depends not only on the substrate and oxide layer fabrication procedure, but also on the measurement techniques used. This is because there are in fact two kinds of distinct regions near the interface: compositional and structural transition layers <sup>34</sup>. The compositional transition occurs abruptly within one silicon atomic layer, which due to cross linking consists of intermediate oxidation states <sup>35</sup>, such as Si<sup>1+</sup>, Si<sup>2+</sup> and Si<sup>3+</sup>. The structural transition, by contrast, takes a much greater extent from the bulk silicon to bulk silicon dioxide. On the silicon side it consists of one or two silicon monolayers in which the atomic arrangement differs from the bulk <sup>36</sup>. Computer simulations of oxygen transport into silicon and the formation of bonds

indicate that within the first monolayer there are extra silicon atoms due to stress, before oxygen diffuses into the silicon network <sup>27,37</sup>. The same simulations provide a partial explanation for the low interface defect densities <sup>27</sup>: during oxidation the oxygen atoms can momentarily be bonded to three silicon atoms, which allows the interface to evolve without leaving dangling bonds.

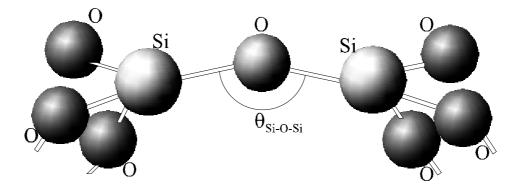

On the silicon dioxide side the transition layer can be as wide as 1 nm, but there remains some uncertainty about its structure. This may have to do with the difficulty of preparing uniform ultrathin oxide layers <sup>34</sup>. It has been proposed that the main structural difference between the bulk and interfacial region is the difference in the intertetrahedral Si-O-Si bond angle (Figure 2.2), otherwise the structure is the same corner-sharing tetrahedron network (i.e. continuous random network of 4-, 6-, 7- and 8- member rings of SiO<sub>4</sub> tetrahedra, joined by bridging oxygens <sup>38</sup>). In calculations where experimental XPS data have been compared with the calculated energy levels of the structure as in Figure 2.2, the calculated value for the reduced Si-O-Si bond angle has been about  $135^{\circ} - 140^{\circ}$ ; the intratetrahedral bond angle used was  $109.47^{\circ}$  <sup>34</sup>. In the oxygen interface region, within about 3 nm of the interface, the distribution changes so that oxide consists of Si<sub>2</sub>O<sub>3</sub>, SiO and Si<sub>2</sub>O <sup>38</sup>. Another possibility is that the coordination for the corner-sharing tetrahedron network is changed, and the intratetrahedral bond angle is not reduced. Then there are overcoordinated oxygen centers (O<sub>3</sub><sup>+</sup>, probably associated with O<sup>-</sup>) <sup>39</sup>.

Figure 2.2 Schematic illustration of SiO<sub>4</sub> tetrahedras joined by bridging oxygen.

The energy band transition from silicon to silicon dioxide cannot either occur without some transition region. Calculated values for the valence and conduction bands indicate that it takes about 0.4 - 0.5 nm before the energy gap corresponds to the bulk values, even for an ideal interface between silicon and crystalline silicon dioxide <sup>42</sup>. This is consistent with simulations <sup>27</sup> indicating that the stoichiometry of the first 0.5 nm of oxide is close to SiO.

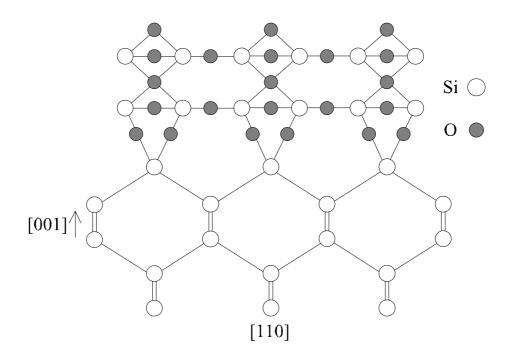

Results have been published according to which there might be some crystalline silicon dioxide near the interface, maintaining an epitaxial relation with the substrate <sup>40</sup>. However, it is estimated that the concentration of these crystallites is low (possibly a few percent) and they are probably unstable <sup>41</sup>. Thus, the possibility to form a totally crystalline transition layer is highly dependent on the oxidation process. One very prominent suggestion is that in an optimal case, the transition layer between crystalline silicon and amorphous silicon dioxide could be an ordered, about 0.5 nm-thick crystalline oxide, tridymite (Figure 2.3), a stable bulk form of SiO<sub>2</sub>. This stability is assumed to decrease, however, when the layer thickness exceeds 1.5 nm <sup>42</sup>. There is also some evidence from transmission electron microscopy (TEM) studies which supports this suggestion <sup>43</sup>.

**Figure 2.3** Schematic illustration of silicon/silicon dioxide tridymite structure <sup>43</sup>.

First-principle calculations <sup>44,45</sup> have proven that in ideal structures the interfaces between silicon and tridymite can be fully relaxed, so that there will be no electron

states in the silicon gap. In these calculations it has been assumed that a tridymite is attached to the silicon (100) surface and the strain is localized to a transition region at the interface and does not persist in the bulk oxide <sup>45</sup>. The width of the transition region, 0.5 nm, accommodates the required change in silicon density. The amount of suboxide of 1.5 monolayers is compatible with the best experimental results. The structure corresponds to a local energy minima, but there might also be other minimas that are even lower <sup>45</sup>. Therefore in order to fabricate such crystals, the process has to be very accurately controlled.

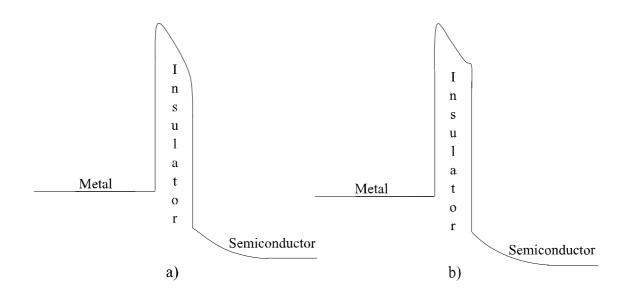

#### 2.2 Tunneling, Leakage, Breakdown and Defect Generation

As was mentioned earlier, tunneling through the oxide becomes significant when the film thickness decreases to about 3 nm. This may cause problems in device operation and also during characterization. In the ultrathin region the direct tunneling current increases by about one order of magnitude when the thickness of the silicon dioxide layer decreases by one nanometer. For the direct tunneling (Figure 2.4a) the current density can be evaluated from the approximate formula  $^{46}$

$$J_{\rm DT} = \frac{q^2 (2\Phi_{\rm M} - V_{ox})}{4\pi h d_{ox}^2} \exp\left[-\frac{4\pi d_{ox}}{h} \sqrt{qm^* (2\Phi_{\rm M} - V_{ox})}\right],$$

(2.1)

where q is unit charge, h Planc constant,  $m^*$  electron effective mass,  $\Phi_M$  the barrier height at the metal/oxide interface,  $V_{ox}$  the voltage across the oxide and  $d_{ox}$  is the oxide thickness.

The so-called Fowler-Nordheim (FN) current might cause more trouble (Figure 2.4b). The magnitude of it can be evaluated by using the following approximate formula <sup>47</sup>

$$J_{FN} = \frac{q^3 V_{ox}^2}{8\pi h \Phi_{\rm M} d_{ox}^2} \exp\left[-\frac{8\pi \Phi_{\rm M} d_{ox}}{3hq V_{ox}} \sqrt{2m^* \Phi_{\rm M}}\right],\tag{2.2}$$

In addition, this tunneling current oscillates to some extent as a function of voltage. This could, in theory, affect the measured impedance. However, the risk is not very great as the oscillation is quite modest and starts at relatively high voltages. Often the oxide field in ultrathin oxides exceeds the breakdown limit even before the Fowler-Nordheim oscillation has started. It has been estimated <sup>48</sup> that direct tunneling dominates for oxides thinner than 4.2 nm and FN-tunneling for oxides over 5.1 nm. This phenomenon, however, has been used to determine the oxide thickness as the oscillation period is dependent on the tunneling barrier thickness <sup>49</sup>. FN-current causes also some stress on the oxide, producing an oxide charge that becomes unstable upon continuing electrical measurements <sup>50</sup>. This further causes instability, possibly making it more difficult to define the material parameters.

Figure 2.4 Tunneling in an MOS structure: a) direct tunneling b) Fowler-Nordheim tunneling.

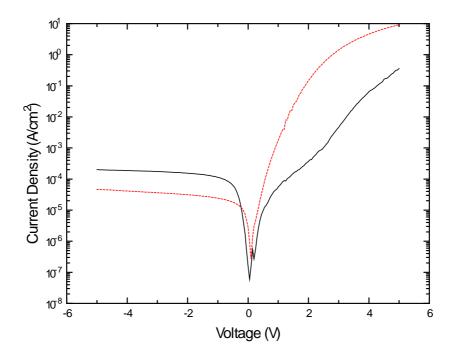

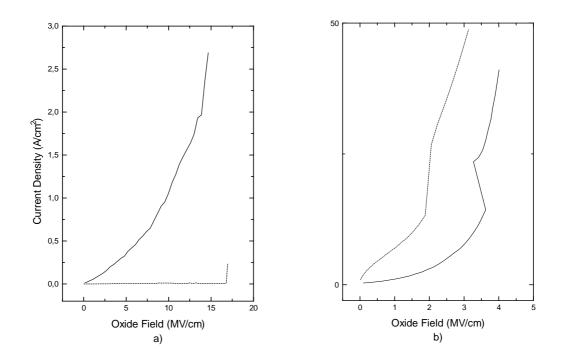

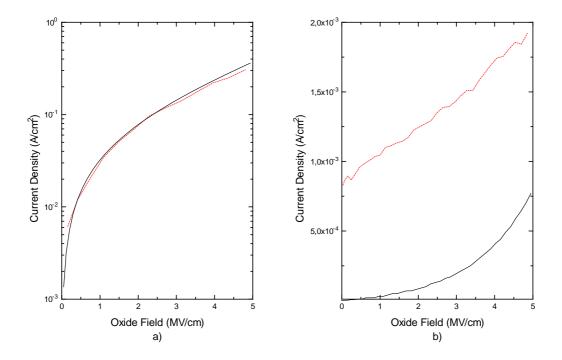

In real devices tunneling is not the only mechanism that allows current passing through the oxide films. If the difference between the theoretical tunneling current and the measured value is significant, this means the structure is non-ideal. Impurities increase the conductivity of the oxide and form extra energy states, increasing the probability of tunneling. Near the interfaces the molecular structure is not as perfect as in bulk material, which also affects the energy band structure. That may significantly reduce the potential barrier height. Various kinds of lattice defects may create conductive channels through the insulator. Because the dimensions are small, any kinds of impurities may diffuse, or spike, through the layers, especially during high temperature processing. The probability of a major defect occurring within the device obviously increases with increasing device area. This means that also the leakage current increases faster than the area. One example of this phenomenon is shown in Figure 2.5. We measured the forward current density in a larger area device to be considerably higher than in a smaller one, even though on reverse bias the situation was the opposite which indicates that the smaller device was not particularly good.

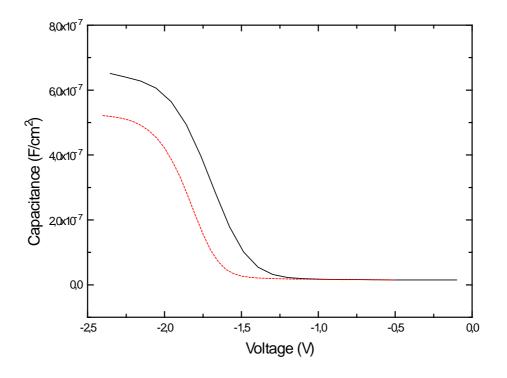

**Figure 2.5** Measured average current density through MOS structures with ultrathin silicon dioxide layer; device area  $(100 \,\mu\text{m})^2$  solid black line,  $(500 \,\mu\text{m})^2$  dashed red line.

The geometry of the device can play quite an important role, particularly when the structures are small. The charge tends to increase and the electric field to get higher towards the edges and in the corners, which means that a significant proportion of the current may in fact be going through the edges of the device rather than evenly through the whole device. At the interfaces the likelihood of impurities occurring is greater, which may also increase conductivity. An example of this can be seen in our measurements presented in the Figure 2.6.

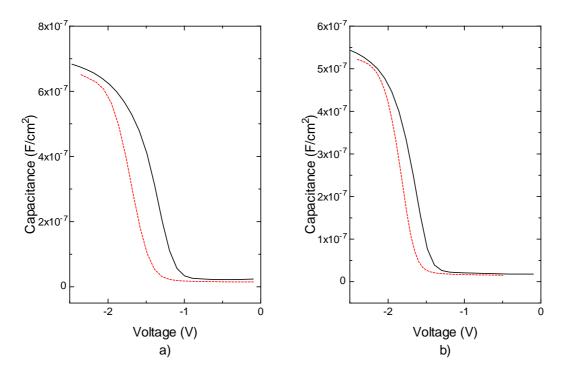

**Figure 2.6** Measured a) average current density b) current divided by the length of device periphery, through two MOS structures. (Solid black line: Device area  $(100 \,\mu\text{m})^2$ . Dashed red line: Device area  $(1 \,\text{mm})^2$ .)

When the tunneling current through ultrathin oxides is measured and compared to simulated ones, it is possible to see indications of trap assisted tunneling components in addition to direct tunneling <sup>51</sup>. It is interesting that even when the number of traps is eliminated as far as possible by careful processing, trap assisted tunneling can still be seen in 'thicker' oxides, but when the film thickness drops below 2 nm, the only mechanism seems to be direct tunneling <sup>51</sup>. Tunneling straight through the film is then therefore energetically more favorable compared to via-traps tunneling. The other possibility, i.e. a sharp decrease in the amount of traps, does not appear very plausible. However, when the film thickness is so small the current level becomes significant anyhow even under normal device operating conditions.

One of the most important material parameters of insulators is the breakdown voltage, or breakdown field. Dielectric breakdown of MOS devices is important both for reliability considerations <sup>52</sup> and in the determination of suitable operation voltages. It is of particularly great significance in the context of ultrathin insulators. Conventional, 'thick' insulator layers made from silicon dioxide have a breakdown field of about

10 MV/cm <sup>46</sup>. This may seem quite high, but expressed in other units it is 1 V/nm. It follows that when the MOS insulator is only 2 - 3 nm, the maximum voltage that can be used across the oxide is no more that a couple of volts. It has also been noted that the strength and stability of these ultrathin oxide films is often not as good as the properties of bulk oxide. This fact must be taken into account in device design.

In ultrathin layers, the breakdown effect differs from the one seen when measuring thicker layers. Because the interface region, for instance, represents a significant portion of ultrathin oxide films, this has an impact on such properties as reliability. It is often possible to see a phenomenon called 'soft breakdown', i.e. a 'smaller' breakdown occurs before the actual breakdown point. It has been suggested that when the bias exceeds the soft breakdown value, electron transport through the film is mainly due to multiple tunneling via generated electron traps <sup>53</sup>. The breakdown effect in general has been related to electron trapping  $^{54}$ , hole trapping  $^{55}$  and interface state generation  $^{56}$ . There are some results according to which interface state generation during voltage stress is quite comparable in thermal oxides and N<sub>2</sub>O oxides, indicating that these state generations are not necessarily the main reason behind the dielectric breakdown <sup>57</sup>. In constant current injection stress measurements, no widening of the breakdown points (as a result of the spreading of thermal faults) has been observed <sup>53</sup>. If, however, the current is not limited, it is possible to see a roughening effect. TEM studies <sup>58</sup> have found that in breakdown spots the silicon melts, deoxidization occurs and the interface is locally shifted. It has been reported that the breakdown is due to a buildup of positive charge at the cathode interface in localized areas<sup>55</sup>. This, it is assumed, consists of holes generated by impact ionization in the oxide and drifted to the cathode. This increases the local field and, through barrier lowering, the current density, and further accelerates the buildup until a very brief runaway process brings the oxide to destructive breakdown.

When holes are trapped near the interface and electrons are subsequently injected, recombination occurs. From the energy released in this process, interface states may be formed <sup>21</sup>. It has been found that the density of these states is dependent on the number of recombination events, but independent of the average oxide field, and therefore the electron energy. Superimposed upon this effect is the generation of interface states due to hot electrons above the heating threshold (about 1.5 MV/cm). Because of this the

defect generation rate also increases sharply <sup>21</sup>.

Thin oxides stressed at high voltages have increased low level pre-tunneling leakage currents <sup>59</sup>. The leakage seems to be localized, not uniform. It is assumed to be due to tunneling through stress-generated positive centers <sup>60</sup>, or local lowering of tunneling barrier due to the generation of local defects <sup>61</sup>. Higher pre-tunneling currents and lower breakdown distributions have been related to oxygen deficiencies at the silicon/silicon dioxide interface <sup>62</sup>. The intrinsic oxide decomposition reaction Si + SiO<sub>2</sub>  $\rightarrow$  2SiO at the interface is supposed to be nucleated at existing defect sites prior to the growth of physical voids. These defects can become electrically active during annealing at temperatures lower (e.g. below 900 °C in UHV) than needed for void formation. Unless sufficient O<sub>2</sub> is available, this can lead to low field dielectric breakdown <sup>62</sup>.

It has been found that an increase in pre-tunneling currents correlates with the number of traps generated within the oxide by high voltage stress <sup>59</sup>. Low field leakage currents introduced in the thin oxide during high field stress are related to defects produced by hot electron transport <sup>63</sup>. The generation of neutral electron traps is assumed to be the dominant cause of this phenomenon. Atomic hydrogen exposure causes similar leakages, supporting the conclusion that currents are related to hydrogen induced defects <sup>63</sup>. Oxide trap distribution is relatively uniform, and trap density increases as the cube root of the fluence of electrons passing through the film <sup>59</sup>. The trapped electrons in stressed oxides seem to be located primarily at border traps: it has been estimated that the centroid of the trapped positive charge lies as close as 1.2 nm to the silicon/silicon dioxide interface <sup>64</sup>. Capacitance-voltage (CV) characteristics analysis of thin oxides stressed at Fowler-Nordheim region have also shown slow traps quite near the interface (charge centroid located up to 2.5 nm from the interface)<sup>65</sup>. The interface trap density increases as the square root of the stress fluence <sup>59</sup>. The high electric fields near the interface and/or reduced barriers to local tunneling, or charge injection caused by hole trapping, may trigger border trap formation as a natural response to increasing local electric fields <sup>64</sup>. It is, however, also possible to see an annealing effect of the defects with increasing temperature <sup>66</sup>.

### **3** Fabrication of Thin Silicon Dioxide Films

#### **3.1 Cleaning of the Substrate Surface**

On the surface of silicon wafers, along with possible contamination, there is a native oxide layer whose thickness is typically a couple of nanometers. This native oxide has to be completely removed in order that a good quality thin oxide film can be produced on silicon surface. It is also required that the sample surface is flat on an atomic scale, because the thin oxide morphology seems to reflect the original surface of the wafer <sup>67</sup>. It is also important that the substrate, its cleaning procedures and other processing stages are carefully selected. It has been shown <sup>68</sup> that oxide defects in thin films can be nearly one order of magnitude larger than that for Float-Zone silicon. However, these defects can be removed by a sacrifice oxidation procedure, in which the oxide thickness is at least 0.4  $\mu$ m. Etching of the substrate surface does not alone seem to suffice <sup>68</sup>.

Usually the wafers are first cleaned by using some chemical cleaning procedure, such as so-called RCA cleaning:

- 5 minute ultrasonic in acetone

- 5 minute isopropyl alcohol

- 10 minutes in  $H_2O:NH_4OH:H_2O_2$  (5:1:1) at 80 °C

- 10 minutes in H<sub>2</sub>O:HCl:H<sub>2</sub>O<sub>2</sub> (5:1:1) at 80 °C

Better results have been achieved by using <sup>77</sup>:

- 10 minutes rinsing in deionized water

- twice 5 minutes in methyl alcohol agitation

- 15 minutes boil in trichloroethylene

- twice 5 minutes in methyl alcohol agitation

- rinsing in water

- 10 minutes in 69%  $HNO_3$  in 130  $^{O}C$

- 10 s dips in 2.5% HF followed by rinsing in water until the surface becomes

hydrophobic

- 10 minutes in 25% NH<sub>4</sub>OH: 30% H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O (1:1:3) in 90 <sup>o</sup>C

- 10 s dip in HF

- rinsing in water

- 10 minutes in 37% HCl:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O (3:1:1) in 90 °C

- 10 minutes rinsing in water

Chemical cleaning procedures are used to remove all unwanted impurities from the surface. The resulting surface is usually of a good enough quality for the fabrication of conventional semiconductor devices. After chemical cleaning, it is possible to passivate the surface by HF treatment, for instance, which will prevent reactions with oxygen in the air or some other oxidizing species in the environment. This passivation, however, is seldom perfect and even at best will not last for long. Recently it has also been demonstrated <sup>69</sup> that the presence of a chemical oxide barely affects growth kinetics or uniformity.

The best way to remove the oxide is to do it *in situ*. This means it is done immediately before the beginning of oxidation and in the same processing equipment, reducing the risk of sample contamination. Excellent results have been reported with this method (e.g. thickness control of the layers fabricated and interface smoothness)<sup>17</sup>. The most common methods of *in situ* native oxide removal are plasma etching or the heating of the sample in an oxygen free environment (in UHV or in inert gas, depending on the process equipment). Since plasma etching is expected to roughen the surface, the heating procedure is often preferred. During heating following reaction will occur<sup>70</sup>

$$2SiO_2(s) \rightarrow 2SiO(g) + O_2(g)$$

and reaction products will desorb form the surface. *In situ* plasma cleaning with hydrogen has also been found to be suitable for silicon MBE processes (e.g. ref.<sup>71</sup>).

Studies of oxygen desorption from silicon surfaces in UHV conditions have found that the desorption starts inhomogenously, mainly at defect sites <sup>72</sup>. Voids are therefore formed at these sites. Low co-ordination number silicon monomers transform to be free

mobile monomers, which diffuse (within the voids) and are incorporated into a reactive oxide complex at the silicon/oxide boundary. The reactive  $SiO_x$  complex and the addition of silicon atoms can then form SiO(g), which desorbs from the surface <sup>72</sup>. This reaction consumes silicon, which means there will form a pit into the silicon surface at the defect site.

An atomically flat silicon surface can be produced by flashing (heating rapidly) the substrate to 1200  $^{\circ}$ C  $^{73}$ . Even though the silicon melting point is around 1400  $^{\circ}$ C, its surface may start (incompletely) to melt at around 1150 – 1200  $^{\circ}$ C in ultrahigh vacuum conditions; there may occur some sublimation of silicon even at lower temperatures (though still above 1000  $^{\circ}$ C)  $^{74}$ . The use of high temperatures seems to smoothen the surface. Interface roughness has been measured both from RCA cleaned and from samples that were RCA cleaned and flashed at 1200  $^{\circ}$ C in UHV before thermal oxidation at 900  $^{\circ}$ C  $^{75}$ . It was found that if only chemical methods are used to clean the substrate, roughness increases as the layer thickness decreases from about 10 nm, reaching its maximum at a layer thickness of 4 nm. In UHV cleaned samples, however, roughness decreases with decreasing layer thickness. It is, however, not always practical or even possible to use such high temperatures. It has been shown that at these temperatures oxygen vacancies and charge traps are formed and there might exist some gettering which roughens the silicon/silicon dioxide interface  $^{76}$ .

In our case the processing equipment is a UHV chamber. Thus the native oxide can be removed simply by heating the sample. We can verify the desorption of the silicon dioxide layer by monitoring the surface by RHEED (Reflection High Energy Electron Diffraction): when the surface turns into a clean, monocrystalline silicon surface, the RHEED pattern becomes clear. Even a thin native oxide layer totally prevents the pattern to be formed. We have used two different native oxide removal procedures. The first consists simply in heating the sample to  $875 \,^{\circ}$ C at  $10^{-10} - 10^{-9}$  mbar<sup>1</sup>. The native oxide is then removed in less than 15 minutes. The second procedure we have used has been shown to produce an excellent surface, entirely clean and flat by removing the native oxide by keeping the sample at  $850 \,^{\circ}$ C and etching the oxide off by a low silicon flux <sup>77</sup>. When some silicon is introduced into the surface in gas form, the reaction Si + SiO<sub>2</sub>(s)  $\rightarrow 2$ SiO(g) happens on the surface, not in the silicon/silicon dioxide interface. For this reason bulk silicon consumption should be lower than in conventional methods.

This probably explains why this method produces quite flat surfaces, even though the temperature is not that high. In fact, it has been suggested that even 780  $^{\circ}$ C may be enough, given the background pressure of 7.10<sup>-11</sup> mbar <sup>73</sup> and the chamber pressure of 1.5.10<sup>-9</sup> mbar during silicon deposition. In our experiments <sup>2-4</sup> we have used this lower temperature and seen that the native oxide is removed quite quickly, within one minute.

#### **3.2 Thermal Oxidation**

Thermal oxidation is the most common, and also the simplest way to produce silicon dioxide layers. In microelectronics device processing the best silicon/silicon dioxide interfaces are fabricated by thermal oxidation of (100) silicon <sup>78</sup>. When the sample is heated in an oxygen-containing atmosphere, its surface becomes oxidized. The oxygen is normally introduced in gas form ('dry oxidation'), but sometimes water vapor ('wet oxidation') is used. It is also possible to use oxygen plasma, which increases the oxidation rate, but in this case the process is more sensitive and it might increase interface roughness and defect density (e.g. <sup>79</sup>). This is because the plasma may also etch the surface.

The main process parameters affecting the oxidation rate, and also the oxide and interface quality, are temperature and oxygen concentration. An increase in either one of these also increases the oxidation rate and the maximum layer thickness that can be achieved. Oxidation temperature is the most important process parameter affecting oxide quality; the hotter the better. Oxidation at high temperatures minimizes interface roughness and produces the best quality material. In practice this is also seen in decreasing interface trap density <sup>80</sup>.

The most usual reactions

$$Si + O_2 \rightarrow SiO_2$$

and  $Si + 2H_2O \rightarrow SiO_2 + 2H_2$

are also reversible. If the desorption rate from the surface is high enough, this may increase surface roughness. The presence of hydrogen during oxidation, or annealing oxides in a hydrogen-containing atmosphere, is usually considered to have beneficial effects on oxide quality. The addition of hydrogen has the beneficial property of rendering charge traps inactive <sup>46</sup>. One must, however, be careful in adjusting the process, because there is evidence that the introduction of extra hydrogen into the oxide may also aid in the creation of interface traps <sup>81</sup>.

During the early stages of thin oxide growth the interface between silicon and its thermal oxide undergoes atomic scale roughening <sup>82</sup>. This reaches its peak and then begins to diminish as growth proceeds. This is also an indication of a nonuniform oxidation process: the growth of about 1 nm protrusions can be explained by a reduction in the interface reaction rate brought about by local stress effects <sup>82</sup>. At temperatures above about 950 - 975 °C, oxide films grow stress-free, which is attributed to the 'viscous flow' of the oxide <sup>83</sup>. The temperature limit above which this is possible is called the 'viscous flow point'. Relaxation of the silicon dioxide layer by this viscous flow and the transition to diffusion controlled growth act to eliminate roughness. This is reported to peak at a layer thickness of about 4 nm<sup>82</sup>. Another defect-density-maximum has also been found in Czohralski silicon wafers<sup>84</sup>, with the oxide defect density increasing with increasing film thickness between 5 and 40 nm, and decreasing above 80 nm. The dependence of defect density on thickness is probably much affected by the substrate, impurity concentrations and oxidation procedure: for instance the '60 nm defect maximum' has not been found when using Float-Zone substrates <sup>84</sup>. It has also been noted that even thick oxides with seemingly low oxide defect densities do in fact contain many small defects. These, too, may have serious adverse effects on oxide reliability. This quality decrease is probably caused by oxygen molecules diffusing through the oxide <sup>82</sup>. With increasing thickness, the diffusion slows down. At the beginning, on the other hand, there is less oxide structure to be damaged in the first place.

First-principle calculations of stresses affecting the process have shown that a uniform oxide layer can be obtained with any thickness by thermal oxidation once a uniform surface oxide layer has been formed <sup>26</sup>. Therefore the preparation of the initial surface oxide is crucial for obtaining a uniform surface oxide layer with atomically controlled thickness.

The 'rapid thermal oxidation' (RTO) process is in widespread use in the fabrication of thin oxide films. Typically this is done by oxidizing silicon with  $O_2$  or by using  $N_2O$ . The results have been excellent, and the processes are now so refined that thickness can be controlled to the accuracy of a few Angstroms. On the thickness scale of 2 - 5 nm, thickness can be controlled within 10% <sup>85</sup>. The temperatures used are typically between 700 - 1200 °C, and the oxidation time is around one minute. After the oxidation of ultrathin layers <sup>85</sup> the surface state densities can be as high as  $10^{12} \text{ eV}^{-1}\text{cm}^{-2}$  but they can be reduced by annealing to the level of  $10^{10} \text{ eV}^{-1}\text{cm}^{-2}$ . In the RTO method, too, increasing temperature decreases leakage current and fixed charge density, but it has also been found to decrease breakdown voltage <sup>86</sup>. This may be due to pinholes or to defects created by the high temperature processing into the oxide.

It is predicted that the interface quality declines when the oxidation temperature is below the viscous flow point of the oxide <sup>82</sup>. Using temperatures above this point helps to avoid mechanical failure effects in IC-processing. High temperatures, which are usually needed to fabricate good quality layers, also increase the oxidation rate and therefore make it harder to adjust the film thickness. However, good results have been achieved by using ultra clean processes and low partial pressures of oxygen in some inert gases like argon <sup>87</sup>, or low pressure oxidation <sup>88</sup>. These not only help to achieve more precise thickness control, but also a thickness uniformity may be improved <sup>17</sup>. This does not, however, mean that oxidation times would not be much shorter than in conventional thermal oxidation. The oxide properties also tend to differ, sometimes quite considerably, when the oxidation parameters are changed <sup>89</sup>.

There has also been some research to study the use of temperatures lower than in RTO (in practice usually above 650  $^{\circ}$ C  $^{90}$ ) in the fabrication of ultrathin silicon dioxide layers. However, at temperatures below 1000  $^{\circ}$ C there may occur stress-induced dislocations and edge cracking. The problems have been tackled by reducing oxidation times to no more than a few seconds <sup>31</sup>. On the other hand, oxidation at lower temperatures can produce layers comparable to high temperature oxides. As well as giving improved thickness control, low temperature processing also prevents degradation of device performance due to the redistribution of impurities and the formation of stress-induced defects in silicon <sup>91</sup>. There still are, however, problems with low temperature oxidation: the oxidation rate is slow, and the oxidation also saturates

too early to form a layer thick enough for microelectronics purposes. To increase the film growth rate, and especially to make it possible to fabricate slightly thicker layers, additional techniques have been developed. It has been demonstrated <sup>92</sup> that by using high pressure oxidation (10 bar), the temperature can be lowered to 650  $^{\circ}$ C and the oxide still shows excellent characteristics. The use of activated oxygen and low pressure also makes it possible to use low temperatures (300 - 500  $^{\circ}$ C) and still produce high quality properties <sup>93</sup>.

A typical way of increasing the growth rate is to use plasma instead of oxygen gas (or  $N_2O$  gas or water vapor). This allows the oxidation temperature to be dropped by a couple of hundred degrees, say to 600 °C <sup>94,95</sup>, or if no more than about two nanometers are needed, even as low as 400 °C <sup>96</sup>. This is due to the smaller size and increased reactivity of oxygen atoms as compared to the 'traditional' oxidizing molecules, molecular oxygen or water. To carry out oxidation at room temperature, one possibility is to use a low energy ion beam <sup>97</sup> or a multipolar electron cyclotron resonance source for plasma generation <sup>98</sup>. One method that has been used to fabricate high quality silicon dioxide films at room temperature (up to 11 nm) is oxidation by O<sub>2</sub> cluster ion beams <sup>91</sup>. In this case less damage will be caused by the beam, since the acceleration energy is divided between the single atoms of the cluster. It follows that the atom interactions occur near the surface. Some annealing is needed after this process, but it has been found that 30 minutes at 400 °C should be enough <sup>91</sup>.

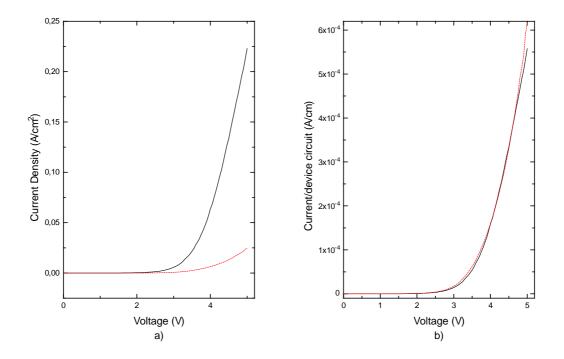

#### Nitrided Oxides

$N_2O$  has recently become an increasingly popular oxidizing gas. The main benefits achieved with  $N_2O$  in oxidation, or post oxidation nitridation of conventionally oxidized layers, are the improved breakdown properties <sup>52,99</sup>. There is less degradation under hot electron stress and resistance to hot carrier induced interface state generation also improves with increasing N concentration <sup>100,101</sup>. It has been reported that increased nitrogen concentration in the silicon/silicon dioxide interface increases interface state densities, but decreases the tunneling current. This current reduction has been estimated to be about one decade at any film thickness from 2.5 to 5 nm <sup>102</sup>. This, it is assumed, is due to the increase in the area of the tunneling barrier (Figure 3.1). The growth rate is also significantly lower, helping with process adjustment <sup>31,100</sup>.

**Figure 3.1** The conduction band structure of MOS structure with a) silicon dioxide b) silicon dioxide with nitrided interfacial layer tunneling barrier.

There are also some results which suggest that interface state generation during voltage stress is more or less comparable in thermal oxides and N<sub>2</sub>O oxides <sup>57</sup>. However, immunity to impurity state generation seems to be better with N<sub>2</sub>O oxides under stress <sup>52</sup>. Improved radiation hardness has also been shown <sup>103</sup>. This is the result of both suppressed electron trapping and enhanced hole detrapping due to interfacial nitrogen incorporation <sup>52</sup>. Impurity diffusion is decreased because the barrier properties to impurity penetration are better <sup>104,100</sup> and the mobility under high normal field in the MOSFET channel is higher <sup>100,101,105</sup>. It has been concluded that this is due to a combination of surface roughness scattering and the buried-channel nature of carrier conduction <sup>105</sup>. Peak mobility, however, decreases with the increase in nitrogen concentration, at least as far as NMOS is concerned <sup>101</sup>. In PMOS even peak mobility has been found to improve <sup>101</sup>. However, the fixed oxide charge and interface state densities also increase with increasing nitrogen, and it is estimated that the optimal nitrogen concentration is about 3% <sup>101</sup>. There is also some evidence that oxynitride film thickness may be more homogenous than in silicon dioxide films <sup>106</sup>.

#### **3.2.1 Deal-Grove Model**

In the conventional, so-called Deal-Grove model used for oxidation rate calculations in thermal oxidation  $^{46,107}$ , an oxygen flux creates an oxygen concentration  $C_0$  on the surface. Oxygen diffuses through the existing silicon dioxide layer (thickness *z*) into the silicon. When the oxygen concentration in the silicon/silicon dioxide interface is  $C_s$ , the flux is defined as

$$F_1 = D \frac{dC}{dz} \approx D \frac{C_0 - C_S}{z}, \qquad (3.1)$$

where D is the diffusion coefficient. The oxygen molecules coming to the silicon/silicon dioxide interface react with silicon at a rate that is proportional to the concentration. This requires the flux

$$F_2 = kC_{\rm S} \,. \tag{3.2}$$

When

$$F = F_1 = F_2,$$

(3.3)

the oxidation rate is

$$\frac{dz}{dt} = \frac{F}{C_1} = \frac{C_0}{C_1} \frac{D}{z + D/k} , \qquad (3.4)$$

where  $C_1$  is the concentration of oxidizing molecules in the silicon dioxide. The time needed to grow a layer of thickness *z* can be calculated from equation (3.4). The result is

$$t = \frac{1}{B} \left[ z^2 - d_0^2 + A(z - d_0) \right] \quad z > d_0,$$

(3.5)

where  $d_0$  is the oxide thickness at the beginning. The parameters  $B/A \equiv 2kC_0/C_1$  and

$B \equiv 2DC_0/C_1$ , which are usually referred to as linear and parabolic rate constants, possess the temperature dependence  $\exp(-E_A/k_BT)^{46}$ .

The Deal-Grove model assumes that there always exists an initial oxide layer through which the oxidizing molecules have to penetrate and that this diffusion process is the main factor limiting the growth (*diffusion limited growth*). The parabolic growth behavior presented in equation (3.5) has been verified down to an oxide thickness of 5 nm <sup>87</sup>. As the thickness of the insulator layer needed for MOS devices decreases below 20 nm, some experiments <sup>108</sup> (thermal oxidation in atmospheric pressure and temperatures around 1000 °C) have, however, indicated that the Deal-Grove model tends to underestimate the initial growth rate. Therefore an extension has been developed to this model <sup>108</sup>. Here the parameter *k* from equation (3.2) assumes the form

$$k \to rC_{\rm gr},$$

(3.6)

where  $C_{\rm gr}$  is the concentration of so-called *growth sites* in the silicon/silicon dioxide interface. These are suggested to be sites formed by silicon suboxides, silicon clusters or interestial atoms that can react with the oxidizing species.

The growth site concentration changes due to a generation mechanism (which is assumed to have an Arrhenius-type temperature dependence) and to recombination, in which the dominating factors are the concentration of these sites and the amount of the silicon atoms. The atom concentration is constant, therefore

$$\frac{dC_{\rm gr}}{dt} = G_0 e^{-E_A/k_B T} - \frac{1}{\tau} C_{\rm gr} , \qquad (3.7)$$

and since we are talking about ultrathin layers, the growth rate is about the same as the linear rate constant

$$\frac{dz}{dt}\Big|_{x=small} \approx \frac{B}{A} = r \frac{C_0}{C_1} C_{\rm gr} \approx e^{-E_A/k_B T} \left( l_0 + a_0 e^{-t/\tau} \right).$$

(3.8)

On this basis the initial growth rate is exponential rather than constant. Deductions made from simulations of quantum molecular dynamics suggest that there might indeed be a very fast oxidation step that precedes the diffusion limited growth. It has been estimated that the oxide layer has to be at least about 0.7 nm thick before the oxidation becomes diffusion limited 109.

### **3.3 Other Fabrication Methods**

One of the most common ways of fabricating thin silicon dioxide layers in microelectronics is by the means of *chemical vapor deposition* (CVD). In this method the oxide, and especially the electrical quality of the silicon/silicon dioxide interface, is not as good as in thermal oxidation, but the use of post oxidation annealing has produced some good results. In fact results have been published according to which the MOSFET transconductance can be even higher than in devices in which the gate oxide is fabricated by thermal oxidation. One possible reason for this is the smoother silicon/silicon dioxide interface, which is defined only by the original high quality silicon surface <sup>110</sup>. It is also possible that the explanation lies in some resultant tensile stress in the oxide <sup>111</sup>. The higher oxide charge may also have some effect, rejecting carriers from the interface and thus decreasing the interfacial roughness scattering.

The *plasma enhanced CVD* (PECVD) method is widely used in microelectronics, not least on account of its low processing temperatures, usually below 350 °C. Using this method, silicon dioxide layers have been fabricated <sup>112</sup> (at 250 °C) in which after annealing the surface state densities are in the range of  $1 - 4 \cdot 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup>. These values are comparable to thermally grown layers. Hydrogenated silicon oxide films have also been fabricated by PECVD at temperatures as low as 15 - 150 °C <sup>113</sup>. However, this tends to produce a low oxygen concentration (SiO<sub>x</sub>:H, x < 2) and a porous film structure. This precludes applications in devices, but it is still possible to take advantage of the fact that the layer will be easily oxidized <sup>113</sup>.

In plasma assisted processes there is the risk that the exited oxidizing species may damage the substrate surface upon impact. For this reason there has been quite a lot of interest in the *low pressure CVD* (LPCVD; e.g. 0.13 mbar<sup>114</sup> or  $\leq$  0.01 mbar<sup>115</sup>) process. This process gives a slower growth rate and thus allows for easier control of the thickness of ultrathin layers. In this process the silane and oxygen are mixed prior to entering the reactor, and deposition is achieved by a pyrolytic process at the substrate surface <sup>114</sup>. In *remote plasma enhanced CVD* (RPECVD) the process temperature can be lower. The activation energy in the process is also much lower, about one order of magnitude, than in thermal oxidation <sup>93</sup>. It must also be noted that if higher temperatures are used in RPECVD, some thermal oxidation will occur and affect film growth <sup>93</sup>.

As-grown chemical oxides are uniform, have a low density, and contain a variety of defects such as Si-H bonds, dangling bonds, voids and OH groups, both in the oxide and at the interface. Therefore in order to reach gate oxide quality, it is necessary to have high temperature ( $800 - 1000 \text{ }^{\circ}\text{C}$ ) process stages <sup>116</sup>. For example absorbed hydrocarbon contaminants dissociate and become chemically incorporated into thin oxides as additional silicon oxide, carbide, hydrid and hydroxyl species. In UHV conditions these persist up to the SiO desorption temperature (up to  $850 - 1000 \text{ }^{\circ}\text{C}$ ) so that once formed, these defects will be present in the final device structure <sup>116</sup>.

Deposited (LPCVD at 420  $^{\circ}$ C, as well as RPECVD at 300  $^{\circ}$ C) thin oxides show enhanced Fowler-Nordheim tunneling currents compared with thermal oxides, even after some high temperature (750  $^{\circ}$ C 40 minutes N<sub>2</sub>-O<sub>2</sub><sup>117</sup>) annealing. They also exhibit very large electron trapping, with the traps reside close to the silicon/silicon dioxide interface <sup>117</sup>. It has also been reported that after annealing layer quality (oxide fixed charge and surface state density) can be comparable to thermal oxides, although the measured electron barrier height is still significantly lower <sup>114</sup>.

To maximize the benefits achieved by the low temperature CVD process and to combine those with the high quality interface properties achieved with thermal oxidation, a two-step process has also been used <sup>118</sup>. Here a low trap-density silicon/silicon dioxide interface has been fabricated by plasma assisted oxidation. After this the 'bulk oxide' is made by RPECVD deposition of silicon dioxide with device quality properties. The first stage, which produces an oxide film about 0.5 nm thick, also removes carbon residuals from the surface and prevents nitrogen incorporation at the interface.

As mentioned earlier in chapter 3.2, nitrogen incorporation into the oxide improves some insulator properties. CVD can also be used to grow these nitrided oxide films. The difference between these silicon dioxide and nitrided films are quite similar to thermal oxides: above 3% the positive oxide charge increases linearly with the nitrogen concentration, and above 4% there is also a sharp decline in mobility <sup>119</sup>.

The silicon surface can also be oxidized *chemically*, for instance simply by keeping it in a hydrogen peroxide solution. This gives a very slow oxidation process, however, and it is only possible to produce very thin layers. This oxidation procedure has been tested by oxidizing monohydride terminated atomically flat silicon (111) wafers in an ultrapure 30% H<sub>2</sub>O<sub>2</sub> solution at room temperature <sup>120</sup>. The first bilayer was oxidized within 30 minutes and then the process saturates; after two months only 60% of the next bilayer has been oxidized. This is obviously not a practical procedure for producing layers for most device applications: the tunneling probability is too high (chapter 2.2). Also, the average composition of the first bilayer is about SiO<sub>1.2</sub>, and hence the layer quality does certainly not correspond to the properties of SiO<sub>2</sub>.

Another way to fabricate thin silicon dioxide layers on silicon is to use the method of *anodic oxidation*. By using  $NH_4OH:H_2O^{-121}$  or 0.1M HCl<sup>-122</sup>, for instance, as electrolyte, it is possible to grow layers 1 - 10 nm thick. The resulting oxide thickness is strongly dependent on the visible illumination intensity<sup>123</sup>, which can be used to adjust the process.

The *atomic layer epitaxy* (ALE, also Atomic Layer Deposition (ALD) or Atomic Layer CVD) method has also been used to fabricate thin silicon dioxide layers. One of the binary reaction sequences used is (asterisks indicate the surface species)<sup>124</sup>

$$SiOH^* + SiCl_4 \rightarrow SiOSiCl_3^* + HCl$$

$$SiCl^* + H_2O \rightarrow SiOH^* + HCl$$

As each of the half-reactions is self-limiting, growth is controlled layer by layer. The resulting surfaces are very flat  $^{125}$ , as flat as the original silicon substrate surfaces. The measured deposition per one processing cycle (at 330 °C and 1 - 13 mbar) is only

0.11 nm. This is quite interesting as one silicon dioxide monolayer should be more than two times that. This might mean that the layer is strongly ordered. The 'growth rate', i.e. the thickness of one deposited layer, decreases with increasing temperature (at least between 330 and 530 °C <sup>125</sup>), which correlates with the thermal stability of the SiOH\* surface functional groups <sup>126</sup>. The other reaction used in ALE <sup>127</sup> is based on the deposition of CH<sub>3</sub>OSi(NCO)<sub>3</sub> and H<sub>2</sub>O<sub>2</sub>. This process can be performed at room temperature with a deposition rate of 0.2 nm/cycle. After 100 cycles surface roughness is only ±1.0 nm, but the measurements indicate that the layers formed are silicon rich (SiO<sub>173</sub>).

Thermal oxidation produces higher quality material than any other method, but all of these other methods are nonetheless usable, if not for MOSFETs or tunneling devices then at least for other purposes. Poor quality oxide may even result in higher intensity light emission for instance. Although the method of sputtering, for example, is quite a 'rough' way of making such fine structures as nanometer scale silicon/silicon dioxide devices, it has been used to fabricate some luminescent structures. The results seem very encouraging, but the usability of these layers in electronic devices remains to be established. In photoluminescent devices the non-homogeneity of the silicon dioxide and the grain boundaries may even serve to improve the luminescence. The main benefits of sputtering are its low costs and low processing temperatures. On the other hand, the interface state densities tend to be high and the breakdown fields too low  $^{128}$ . One of the methods employed in an attempt to improve the layer quality has been to carry out the sputtering in an oxygen-containing atmosphere and to use some post oxidation rapid thermal annealing (RTA). RTA has been found to drop the interface state densities to the level of  $1.8 \cdot 10^{12} \text{ eV}^{-1} \text{cm}^{-2}$  and by post metallization anneal (350 °C) to 3.5·10<sup>11</sup> eV<sup>-1</sup>cm<sup>-2</sup> <sup>129</sup>. A lowering of the sputtering pressure also seems to produce better layers.

## **3.4 Annealing**

Device processing always involves in practice some post oxidation thermal treatments. Annealing after oxidation decreases the amount of oxide charge and the silicon/silicon dioxide interface trap density. There are two basic annealing procedures: low temperature annealing, which typically continues for tens of minutes, and rapid thermal annealing at high temperatures.

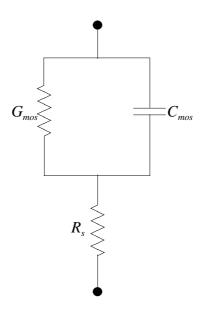

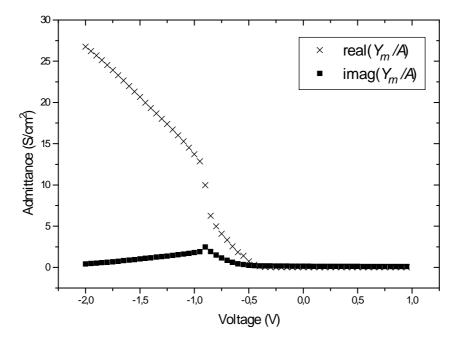

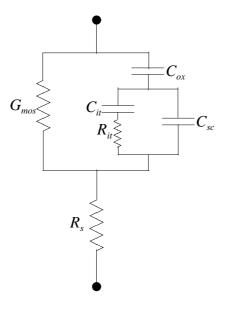

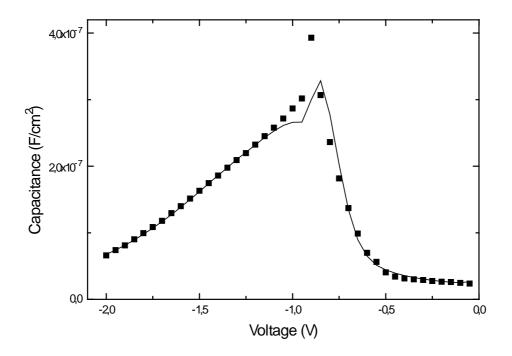

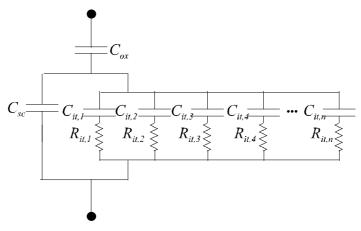

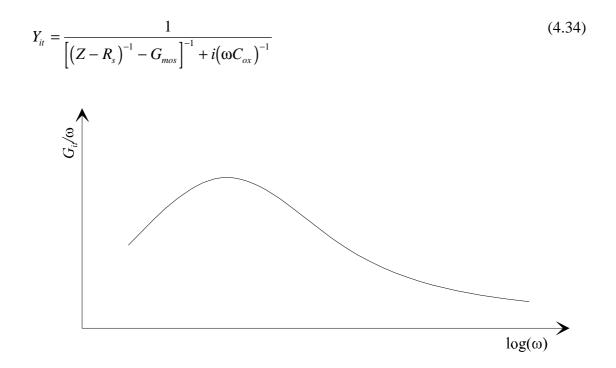

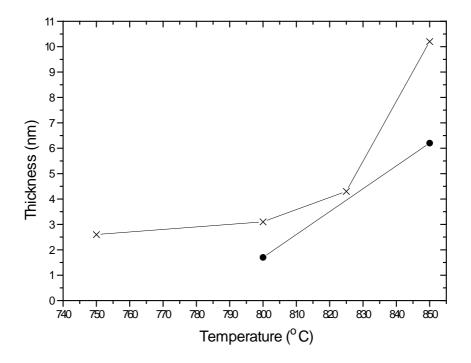

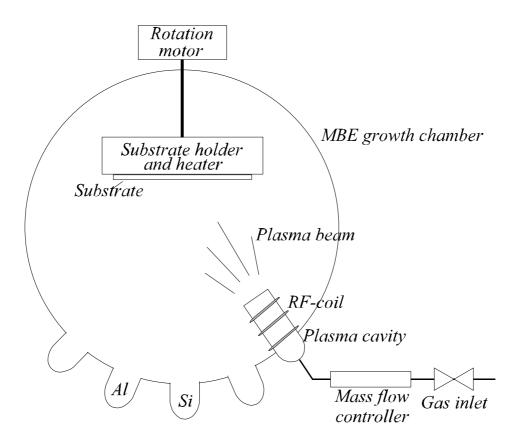

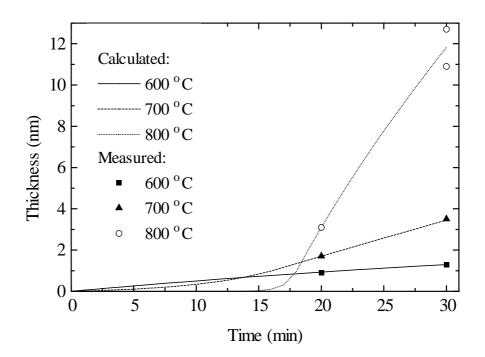

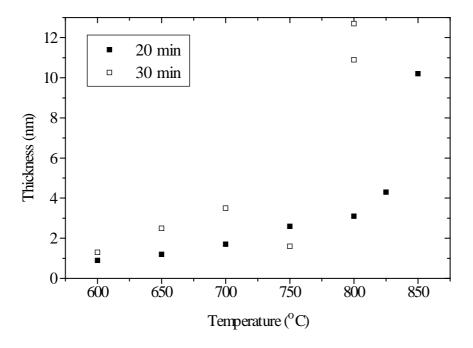

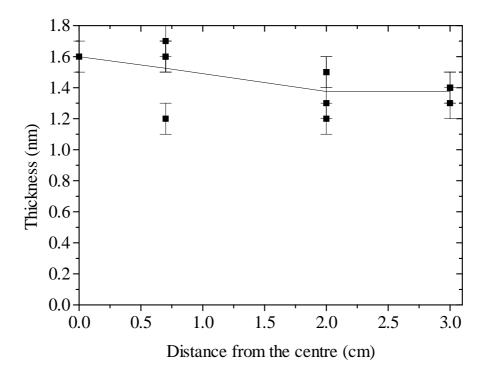

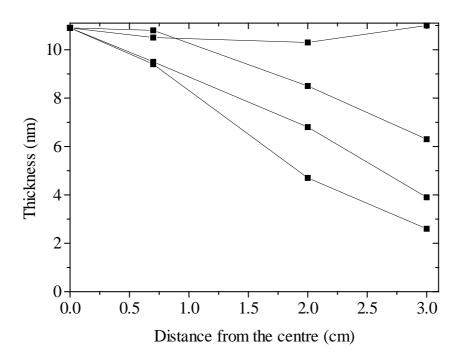

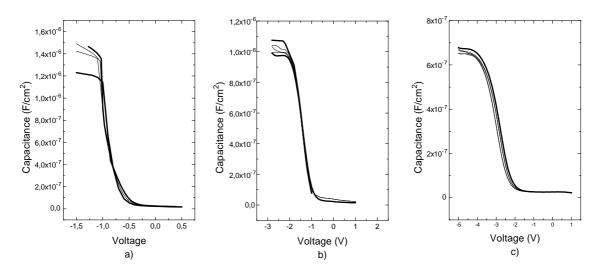

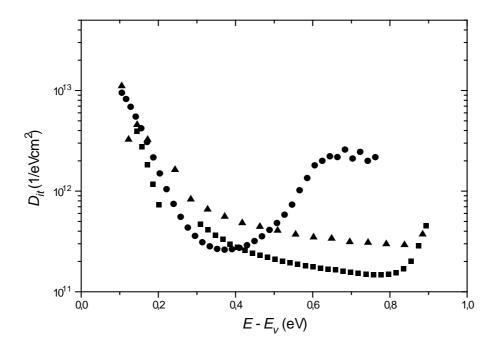

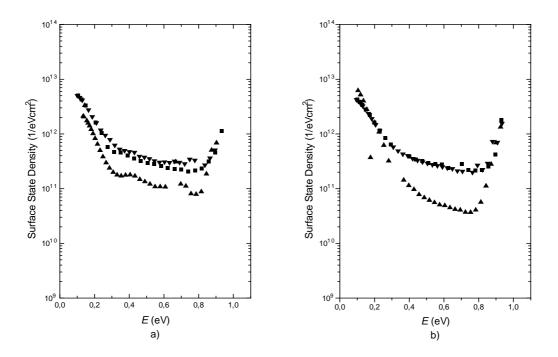

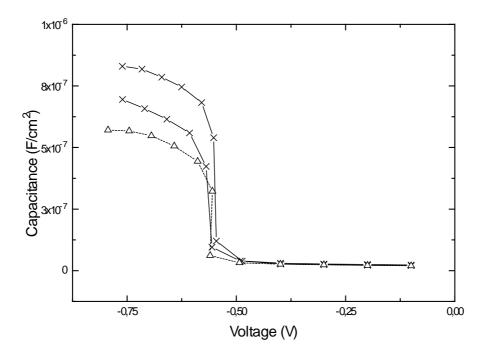

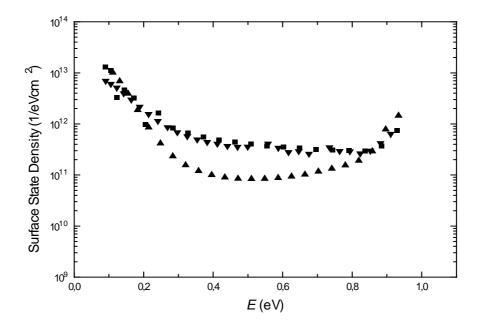

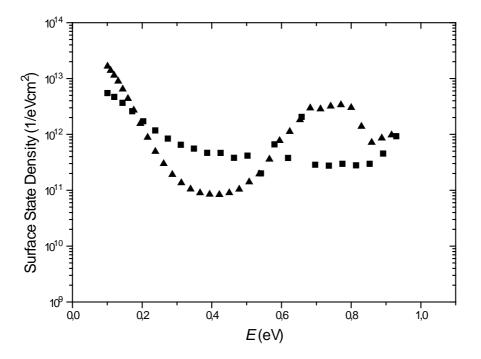

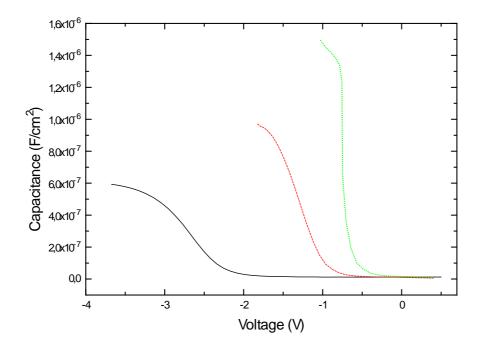

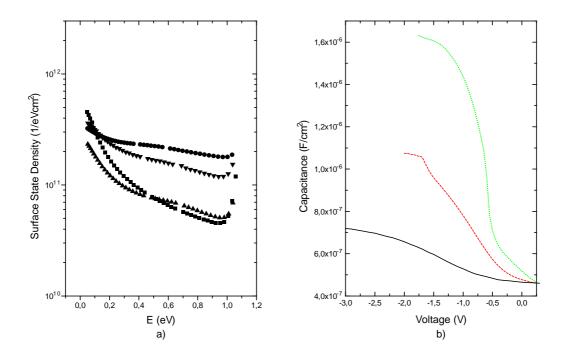

Although the general preference is for high temperatures, it has been shown that temperatures as low as 300 - 400 °C are sufficient to decrease the surface state densities. Values between  $1 \cdot 10^{10}$  and  $5 \cdot 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup> have been measured after annealing from samples fabricated by the PECVD method <sup>112,115</sup>.