Helsinki University of Technology Electronic Circuit Design Laboratory Report 35, Espoo 2002

## Pipeline Analog-to-Digital Converters for Wide-Band Wireless Communications

Lauri Sumanen

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Department of Electrical and Communications Engineering for public examination and debate in Auditorium S1 at Helsinki University of Technology (Espoo, Finland) on the 13th of December, 2002, at 12 o'clock noon.

Helsinki University of Technology Department of Electrical and Communications Engineering Electronic Circuit Design Laboratory

Teknillinen korkeakoulu Sähkö- ja tietoliikennetekniikan osasto Piiritekniikan laboratorio Distribution: Helsinki University of Technology Department of Electrical and Communications Engineering Electronic Circuit Design Laboratory P.O.Box 3000 FIN-02015 HUT Finland Tel. +358 9 4512271 Fax: +358 9 4512269

Copyright © 2002 Lauri Sumanen

ISBN 951-22-6222-3 (printed version) ISSN 1455-8440

Otamedia Oy Espoo 2002

## Abstract

During the last decade, the development of the analog electronics has been dictated by the enormous growth of the wireless communications. Typical for the new communication standards has been an evolution towards higher data rates, which allows more services to be provided. Simultaneously, the boundary between analog and digital signal processing is moving closer to the antenna, thus aiming for a software defined radio. For analog-to-digital converters (ADCs) of radio receivers this indicates higher sample rate, wider bandwidth, higher resolution, and lower power dissipation.

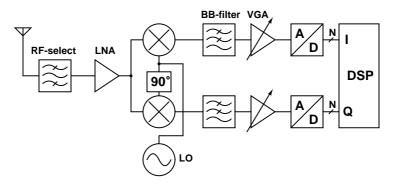

The radio receiver architectures, showing the greatest potential to meet the commercial trends, include the direct conversion receiver and the super heterodyne receiver with an ADC sampling at the intermediate frequency (IF). The pipelined ADC architecture, based on the switched capacitor (SC) technique, has most successfully covered the widely separated resolution and sample rate requirements of these receiver architectures. In this thesis, the requirements of ADCs in both of these receiver architectures are studied using the system specifications of the 3G WCDMA standard. From the standard and from the limited performance of the circuit building blocks, design constraints for pipeline ADCs, at the architectural and circuit level, are drawn.

At the circuit level, novel topologies for all the essential blocks of the pipeline ADC have been developed. These include a dual-mode operational amplifier, low-power voltage reference circuits with buffering, and a floating-bulk bootstrapped switch for highly-linear IF-sampling. The emphasis has been on dynamic comparators: a new mismatch insensitive topology is proposed and measurement results for three different topologies are presented.

At the architectural level, the optimization of the ADCs in the single-chip direct conversion receivers is discussed: the need for small area, low power, suppression of substrate noise, input and output interfaces, etc. Adaptation of the resolution and sample rate of a pipeline ADC, to be used in more flexible multi-mode receivers, is also an important topic included. A 6-bit 15.36-MS/s embedded CMOS pipeline ADC and an 8-bit 1/15.36-MS/s dual-mode CMOS pipeline ADC, optimized for low-power single-

chip direct conversion receivers with single-channel reception, have been designed.

The bandwidth of a pipeline ADC can be extended by employing parallelism to allow multi-channel reception. The errors resulted from mismatch of parallel signal paths are analyzed and their elimination is presented. Particularly, an optimal partitioning of the resolution between the stages, and the number of parallel channels, in time-interleaved ADCs are derived. A low-power 10-bit 200-MS/s CMOS parallel pipeline ADC employing double sampling and a front-end sample-and-hold (S/H) circuit is implemented.

Emphasis of the thesis is on high-resolution pipeline ADCs with IF-sampling capability. The resolution is extended beyond the limits set by device matching by using calibration, while time interleaving is applied to widen the signal bandwidth. A review of calibration and error averaging techniques is presented. A simple digital self-calibration technique to compensate capacitor mismatch within a single-channel pipeline ADC, and the gain and offset mismatch between the channels of a time-interleaved ADC, is developed. The new calibration method is validated with two high-resolution BiCMOS prototypes, a 13-bit 50-MS/s single-channel and a 14-bit 160-MS/s parallel pipeline ADC, both utilizing a highly linear front-end allowing sampling from 200-MHz IF-band.

**Keywords:** analog integrated circuit, analog-to-digital conversion, CMOS, BiCMOS, double sampling, IF-sampling, direct conversion, comparator, pipelined analog-to-digital converter, switched capacitor, time-interleaving, multi-mode, calibra-tion.

## Preface

The research reported in this thesis has been carried out at the Electronic Circuit Design Laboratory, Helsinki University of Technology between years 1998–2002. The work is done within several research projects funded by Finnish National Technology Agency (TEKES), Nokia Networks, and Nokia Mobile Phones. During these years, I had also a privilege of participating the Graduate School in Electronics, Telecommunications, and Automation (GETA), which partially funded the work. I thank Electronic Circuit Design Laboratory and GETA for making the work possible. I am also grateful for the following foundations for the financial support: Eemil Aaltosen Säätiö, Elektroni-ikkainsinöörien Säätiö, Nokia Oyj:n Säätiö, Tekniikan edistämissäätiö.

I would like to express my gratitude to my supervisor Prof. Kari Halonen, who has introduced me into the data converter research and given me the opportunity to work relatively freely under these interesting projects. Without his encouragement, thrust, and way of pushing the design goals this work would not have been completed. I also warmly thank Prof. David A. Johns and Prof. Piero Malcovati for reviewing this thesis and for their valuable comments and suggestions.

I am specially grateful for Dr. Mikko Waltari, who has been my supervisor and partner in the A/D converter research. His inexhaustible storage of innovative ideas, sovereign technical competence, and strong commitment to the projects we have carried out together has been indispensable. The valuable technical contribution of the junior team members in these projects, Tuomas Korhonen, Mikko Aho, and Väinö Hakkarainen, is also gratefully acknowledged.

The other team I have been working with consisted of Dr. Aarno Pärssinen, Jarkko Jussila, Dr. Kalle Kivekäs, and Jussi Ryynänen, who all contributed their own technical specialty in the direct conversion receiver research. I am particularly thankful for the highly motivated, but, friendly and cozy atmosphere the team members created. The close cooperation and humorous spirit within this group have been very essential in completing this work.

I am also very grateful to the whole staff at the Electronic Circuit Design Laboratory.

They have created an exceptional, effective and comfortable, atmosphere and helped in many of the everyday issues related to the work.

Huge thanks to my friends, especially, for remaining me of more important things than this work. The various activities and hobbies of the 'VirNuMiToVi' association have offered excellent contrast for the day's work. And in particular, my fellow students Dr. Kimmo Kalliola and Jani Ollikainen deserve big thanks for keeping up an inspiring, but, entertaining, academic pressure during the whole studies.

Finally, my warmest thanks for the support and love I have received from my family, my mother Anja, my father Markku, and my sister Kaisa. And the biggest thanks to my dear wife, Nadja, who has supported me during the difficult times, as well as shared the good moments. Her love, care, and liveliness have carried me on in this doctoral work.

Lauri Sumanen Espoo, November 2002

# **Symbols and Abbreviations**

| Α           | Amplitude, area, amplifier voltage gain |

|-------------|-----------------------------------------|

| $A_f$       | Voltage gain of feedback amplifier      |

| $A_0$       | Open loop DC-gain                       |

| $b_i$       | Number of output codes                  |

| В           | Bit, effective stage resolution         |

| $B_n$       | Noise bandwidth                         |

| С           | Capacitance, number of uncorrected bits |

| $C_c$       | Compensation capacitance                |

| $C_{f}$     | Feedback capacitance                    |

| $C_L$       | Load capacitance                        |

| $C_{L,H}$   | Effective hold mode load capacitance    |

| $C_{L,tot}$ | Total load capacitance                  |

| Cout        | Parasitic output capacitance            |

| $C_{ox}$    | Gate-oxide capacitance                  |

| $C_{par}$   | Parasitic input capacitance             |

| $C_{s,i}$   | Sampling capacitance                    |

| d           | Scaling parameter of transistor size    |

| $D_i$       | Multiplier of reference voltage         |

| Dout        | Digital output                          |

| DNL        | Differential nonlinearity                             |

|------------|-------------------------------------------------------|

| e          | Noise, error, scaling parameter of transistor current |

| $e_q$      | Quantization error                                    |

| $e^2$      | Noise power                                           |

| Econv      | Energy per conversion step                            |

| ENOB       | Effective number of bits                              |

| f          | Frequency, feedback factor                            |

| fblock     | Frequency of blocker                                  |

| $f_{dig}$  | Digital signal frequency                              |

| fin        | Input frequency                                       |

| flo        | Local oscillator frequency                            |

| fs         | Sampling frequency                                    |

| fsig       | Signal frequency                                      |

| fspur      | Frequency of spurious tone                            |

| $FOM_A$    | Area figure of merit                                  |

| g          | Conductance                                           |

| $G_i$      | Interstage gain                                       |

| $G_{code}$ | Coding gain                                           |

| $G_k$      | Fourier series coefficient of gain mismatch           |

| $g_m$      | Transconductance                                      |

| $G_P$      | Processing gain                                       |

| GBW        | Gain bandwidth product                                |

| HR         | Headroom                                              |

| i          | Stage index                                           |

| Ι          | Current                                               |

| i          | Stage index                                           |

| Iamp                   | Total amplifier current consumption                                                                |

|------------------------|----------------------------------------------------------------------------------------------------|

| $I_D$                  | Drain current                                                                                      |

| I <sub>max</sub>       | Maximal output current of amplifier                                                                |

| Iref                   | Reference current                                                                                  |

| IIP                    | Input intercept point                                                                              |

| INL                    | Integral nonlinearity                                                                              |

| IP                     | Intercept point                                                                                    |

| j                      | Capacitor index                                                                                    |

| k                      | Boltzmann's coefficient, load capacitance relation, number of stages, error correction coefficient |

| Κ                      | Amplifier current gain, gain error correction coefficient                                          |

| L                      | Channel length                                                                                     |

| т                      | Capacitor switching parameter, number of different stage resolutions, in-<br>dex                   |

| М                      | Number of parallel channels                                                                        |

| M <sub>IM</sub>        | Implementation margin                                                                              |

| n                      | Number of sampling capacitors, index                                                               |

| Ν                      | Number of bits, noise power                                                                        |

| Naperture              | Aperture jitter limited resolution                                                                 |

| N <sub>H</sub>         | Number of harmonics                                                                                |

| <i>n<sub>max</sub></i> | Number of capacitors                                                                               |

| N <sub>TH</sub>        | Thermal noise floor                                                                                |

| N <sub>thermal</sub>   | Thermal noise limited resolution                                                                   |

| ND <sub>ADC</sub>      | A/D converter noise distance                                                                       |

| NF                     | Noise figure                                                                                       |

| MDS                     | Minimum detectable signal level       |

|-------------------------|---------------------------------------|

| OSR                     | Oversampling ratio                    |

| $p'_1$                  | Non-dominant pole of amplifier        |

| $P_D$                   | Power dissipation                     |

| P <sub>IMD</sub>        | Power of the intermodulation product  |

| Pout                    | Output power                          |

| PA                      | Peak-to-average signal power ratio    |

| Q                       | Quality factor                        |

| $Q_{ch}$                | Channel charge                        |

| $Q_i$                   | Number of quantization steps          |

| r                       | Redundancy bit, resistance            |

| R                       | Resistance                            |

| r <sub>ds</sub>         | Output resistance of a transistor     |

| $R_{eff}$               | Effective thermal resistance          |

| <i>r</i> <sub>on</sub>  | Switch on-resistance                  |

| <i>r</i> <sub>out</sub> | Amplifier output resistance           |

| <i>R<sub>ref</sub></i>  | Reference value (current or voltage)  |

| S                       | Error correction coefficient          |

| $S_P$                   | Signal rms power                      |

| SNDR                    | Signal-to-noise and distortion ratio  |

| SNR                     | Signal-to-noise ratio                 |

| SR                      | Slew rate                             |

| t                       | Time                                  |

| Т                       | Absolute temperature, sampling period |

| $t_{ox}$                | Oxide thickness                       |

| thd                 | Total harmonic distortion                          |

|---------------------|----------------------------------------------------|

| V                   | Voltage                                            |

| $V_{DD}$            | Positive supply voltage                            |

| $V_{ds}$            | Drain-source voltage                               |

| $V_{ds,sat}$        | Drain-source saturation voltage                    |

| V <sub>FS</sub>     | Full-scale voltage                                 |

| $V_{gs}$            | Gate-source voltage                                |

| Vin                 | Input voltage                                      |

| $V_k$               | Fourier series coefficient of offset mismatch      |

| V <sub>LSB</sub>    | Voltage corresponding to the least significant bit |

| V <sub>margin</sub> | Safety margin of drain-source saturation voltage   |

| Vos                 | Offset voltage                                     |

| $V_{os,c}$          | Comparator offset voltage                          |

| V <sub>SS</sub>     | Negative supply voltage                            |

| $V_T$               | Threshold voltage                                  |

| W                   | Channel width                                      |

| X                   | Input                                              |

| Y                   | Output                                             |

| α                   | Capacitor mismatch                                 |

| β                   | Offset voltage, transistor parameter               |

| γ                   | Gain error                                         |

| δ                   | Relative capacitor mismatch                        |

| ε                   | Error                                              |

| $\epsilon_{A_0}$    | Amplifier gain settling error                      |

| $\epsilon_{\tau}$   | Amplifier GBW settling error                       |

| Carrier mobility                                |

|-------------------------------------------------|

| Corner frequency                                |

| Noise standard deviation, clock jitter          |

| Rms aperture jitter                             |

| Clock phase                                     |

| Hold phase                                      |

| Fourier series coefficient of timing mismatch   |

| Sample phase                                    |

| Second-generation                               |

| Third-generation                                |

| Analog-to-digital                               |

| Analog-to-digital converter                     |

| Baseband                                        |

| Bit-error rate                                  |

| Bipolar complementary metal oxide semiconductor |

| Code division multiple access                   |

| Code density test                               |

| Custom Integrated Circuits Conference           |

| Common mode                                     |

| Common mode feedback                            |

| Complementary metal oxide semiconductor         |

| Common mode rejection ratio                     |

| Digital-to-analog                               |

| Digital-to-analog converter                     |

| Discrete Fourier transform                      |

|                                                 |

| dBc  | Decibel relative to carrier                 |

|------|---------------------------------------------|

| dBFS | Decibel relative to full-scale              |

| DC   | Direct current                              |

| DEM  | Dynamic element matching                    |

| DLL  | Delay locked loop                           |

| DNL  | Differential nonlinearity                   |

| DR   | Dynamic range                               |

| DSP  | Digital signal-processing unit              |

| ENOB | Effective number of bits                    |

| ERB  | Effective resolution bandwidth              |

| FDD  | Frequency division duplexing                |

| FFT  | Fast Fourier transform                      |

| FPGA | Field programmable gate array               |

| GBW  | Gain bandwidth                              |

| GSM  | Global System for Mobile Telecommunications |

| HD   | Harmonic distortion                         |

| Ι    | In-phase component                          |

| IC   | Integrated circuit                          |

| IF   | Intermediate frequency                      |

| IIP  | Input intercept point                       |

| INL  | Integral nonlinearity                       |

| I/O  | Input-output                                |

| IP   | Intercept point                             |

| IMD  | Intermodulation distortion                  |

| IR   | Image rejection                             |

| International Solid-State Circuits Conference<br>Iournal of Solid-State Circuits<br>Local Multipoint Distribution System<br>Low-noise amplifier<br>Local oscillator<br>Least significant bit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Local Multipoint Distribution System<br>Low-noise amplifier<br>Local oscillator<br>Least significant bit                                                                                     |

| Low-noise amplifier<br>Local oscillator<br>Least significant bit                                                                                                                             |

| Local oscillator<br>Least significant bit                                                                                                                                                    |

| Least significant bit                                                                                                                                                                        |

| -                                                                                                                                                                                            |

|                                                                                                                                                                                              |

| Multiplying digital-to-analog converter                                                                                                                                                      |

| Metal oxide semiconductor                                                                                                                                                                    |

| Most significant bit                                                                                                                                                                         |

| n-channel metal oxide semiconductor                                                                                                                                                          |

| Oversampling ratio                                                                                                                                                                           |

| Operational transconductance amplifier                                                                                                                                                       |

| Printed circuit board                                                                                                                                                                        |

| Personal Communication System                                                                                                                                                                |

| Phase locked loop                                                                                                                                                                            |

| p-channel metal oxide semiconductor                                                                                                                                                          |

| Power spectral density                                                                                                                                                                       |

| power supply rejection ratio                                                                                                                                                                 |

| Quadrature component                                                                                                                                                                         |

| Quadrature phase-shift keying                                                                                                                                                                |

| Radio frequency                                                                                                                                                                              |

| Read only memory                                                                                                                                                                             |

| Root raised cosine                                                                                                                                                                           |

| Redundant sign digit                                                                                                                                                                         |

| Switched capacitor                                                                                                                                                                           |

|                                                                                                                                                                                              |

| SFDR                       | Spurious free dynamic range                                                                                                                                         |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S/H                        | Sample-and-hold                                                                                                                                                     |

| SI                         | Switched current                                                                                                                                                    |

| SiGe                       | Silicon-germanium                                                                                                                                                   |

| SNDR                       | Signal-to-noise and distortion ratio                                                                                                                                |

| SNR                        | Signal-to-noise ratio                                                                                                                                               |

| SR                         | Slew rate                                                                                                                                                           |

| SRAM                       | Static random access memory                                                                                                                                         |

| sub-ADC                    | Sub-analog-to-digital converter                                                                                                                                     |

| THD                        | Total harmonic distortion                                                                                                                                           |

|                            |                                                                                                                                                                     |

| UMTS                       | Universal Mobile Telecommunication System                                                                                                                           |

| UMTS<br>VCO                | Universal Mobile Telecommunication System<br>Voltage controlled oscillator                                                                                          |

|                            | ·                                                                                                                                                                   |

| VCO                        | Voltage controlled oscillator                                                                                                                                       |

| VCO<br>VGA                 | Voltage controlled oscillator<br>Variable gain amplifier                                                                                                            |

| VCO<br>VGA<br>VHDL         | Voltage controlled oscillator<br>Variable gain amplifier<br>Very High Speed Integrated Circuit Hardware Description Language                                        |

| VCO<br>VGA<br>VHDL<br>VLSI | Voltage controlled oscillator<br>Variable gain amplifier<br>Very High Speed Integrated Circuit Hardware Description Language<br>Very large-scale integrated circuit |

## Contents

|   | Abs                       | tract   |              | i                                       |  |

|---|---------------------------|---------|--------------|-----------------------------------------|--|

|   | Pref                      | ace     |              | ш                                       |  |

|   | Symbols and Abbreviations |         |              |                                         |  |

| 1 | Intr                      | oductio | n            | 1                                       |  |

|   | 1.1                       | Motiva  | ation for th | e Thesis                                |  |

|   | 1.2                       | Resear  | ch Contril   | pution                                  |  |

|   | 1.3                       | Organ   | ization of   | he Thesis                               |  |

| 2 | Wid                       | e-Band  | Analog-te    | p-Digital Converters 9                  |  |

|   | 2.1                       | Ideal A | A/D Conve    | rter                                    |  |

|   | 2.2                       | A/D C   | onverter S   | pecifications                           |  |

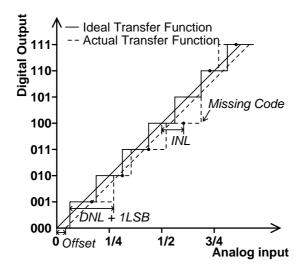

|   |                           | 2.2.1   | Static Sp    | ecifications                            |  |

|   |                           | 2.2.2   | Dynamic      | Specifications 12                       |  |

|   |                           |         | 2.2.2.1      | Signal-to-Noise Ratio                   |  |

|   |                           |         | 2.2.2.2      | Total Harmonic Distortion               |  |

|   |                           |         | 2.2.2.3      | Signal-to-Noise and Distortion Ratio 13 |  |

|   |                           |         | 2.2.2.4      | Spurious Free Dynamic Range             |  |

|   |                           |         | 2.2.2.5      | Effective Number of Bits                |  |

|   |                           |         | 2.2.2.6      | Dynamic Range                           |  |

|   |                           |         | 2.2.2.7      | Intermodulation Distortion              |  |

|   | 2.3                       | Consid  | lerations o  | f A/D Converters in Radio Receivers     |  |

|   |                           | 2.3.1   | Sample I     | Rate                                    |  |

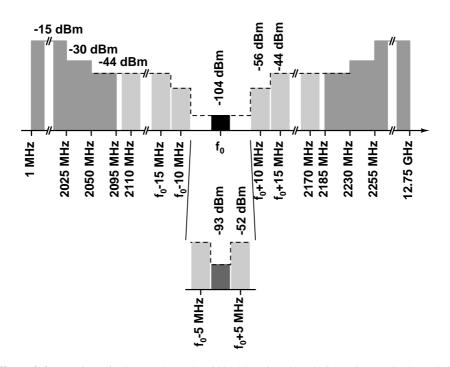

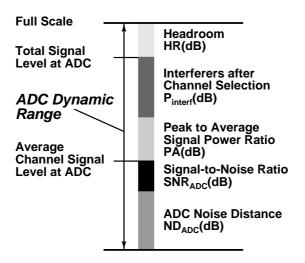

|   |                           | 2.3.2   | Dynamic      | Range 19                                |  |

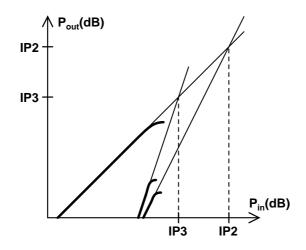

|   |                           | 2.3.3   | Linearity    |                                         |  |

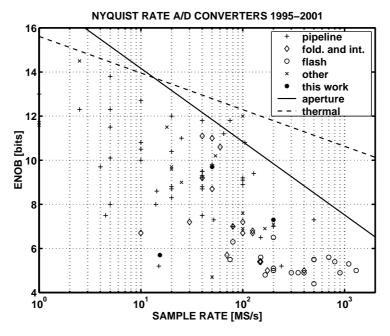

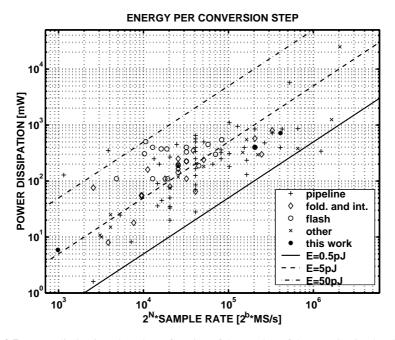

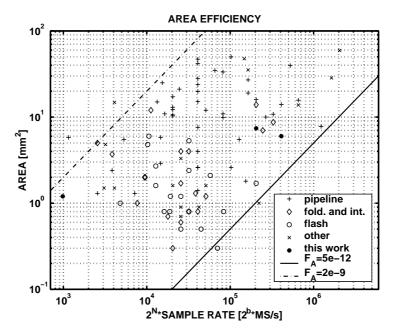

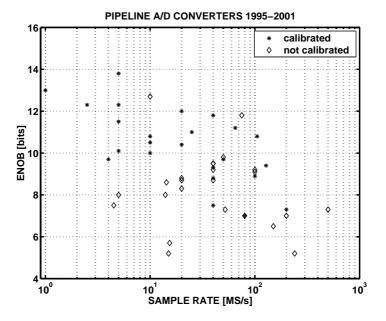

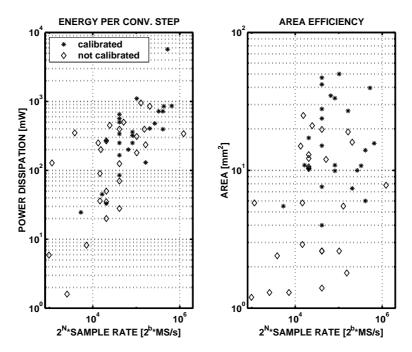

|   | 2.4                       | A/D C   | onverter S   | urvey                                   |  |

| 3 | Pipe               | line An                                                                                                             | alog-to-Digital Converter Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27                                                                                                                                                                                 |

|---|--------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

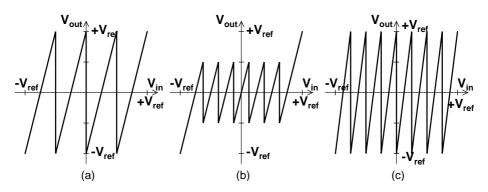

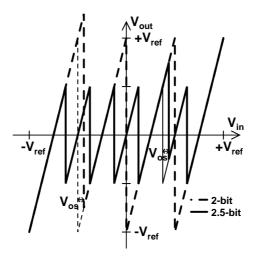

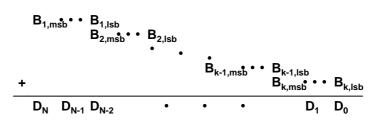

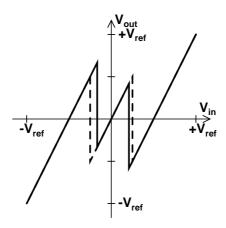

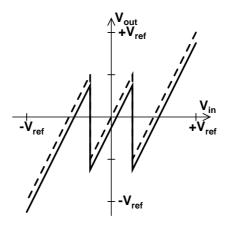

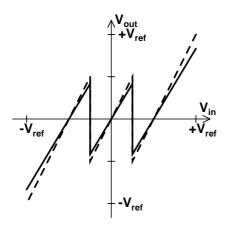

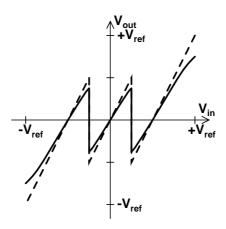

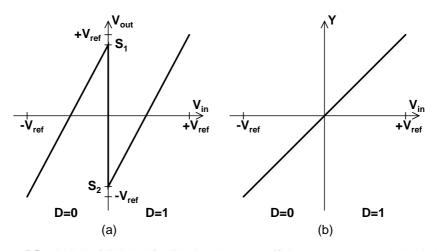

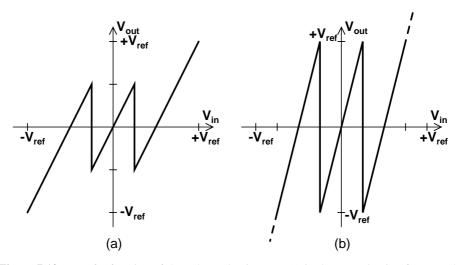

|   | 3.1                | Redun                                                                                                               | dant Sign Digit Coding (RSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29                                                                                                                                                                                 |

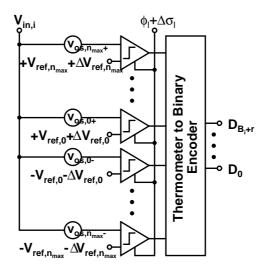

|   | 3.2                | Sub-A                                                                                                               | nalog-to-Digital Converter (sub-ADC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34                                                                                                                                                                                 |

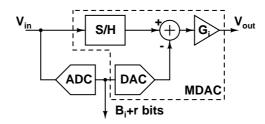

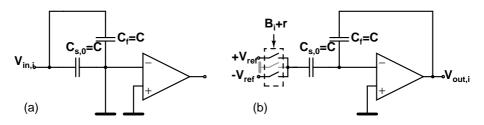

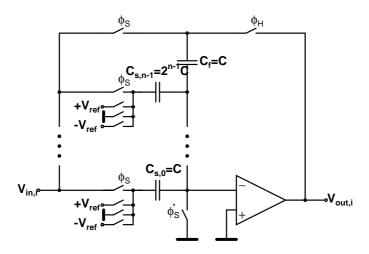

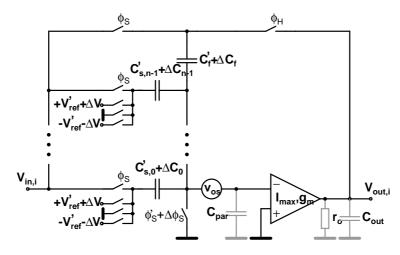

|   | 3.3                | Multip                                                                                                              | lying Digital-to-Analog Converter (MDAC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36                                                                                                                                                                                 |

|   | 3.4                | Nonide                                                                                                              | ealities and Error Sources of Pipeline Stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                                                                                                                                                                                 |

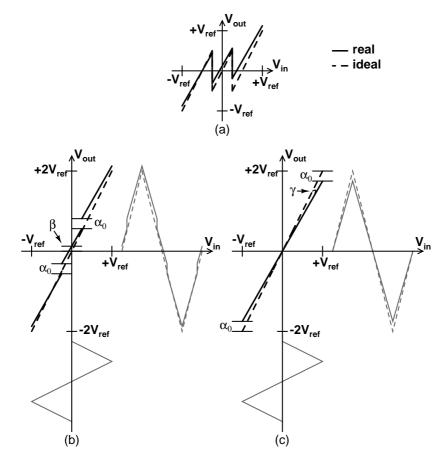

|   |                    | 3.4.1                                                                                                               | Errors in Sub-A/D Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41                                                                                                                                                                                 |

|   |                    | 3.4.2                                                                                                               | Operational Amplifier Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43                                                                                                                                                                                 |

|   |                    |                                                                                                                     | 3.4.2.1 Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43                                                                                                                                                                                 |

|   |                    |                                                                                                                     | 3.4.2.2 Finite Open Loop DC-gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45                                                                                                                                                                                 |

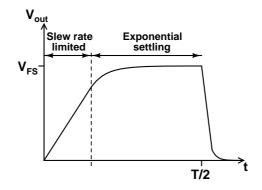

|   |                    |                                                                                                                     | 3.4.2.3 Slew Rate and Gain Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46                                                                                                                                                                                 |

|   |                    | 3.4.3                                                                                                               | Capacitor Mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48                                                                                                                                                                                 |

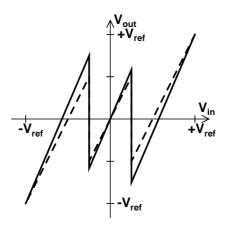

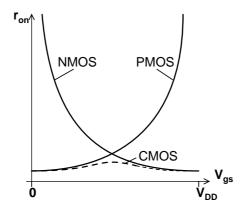

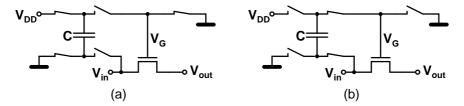

|   |                    | 3.4.4                                                                                                               | MOS Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49                                                                                                                                                                                 |

|   |                    | 3.4.5                                                                                                               | Thermal Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51                                                                                                                                                                                 |

|   |                    | 3.4.6                                                                                                               | Sampling Clock Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52                                                                                                                                                                                 |

|   | 3.5                | Design                                                                                                              | Constraints of Pipeline A/D Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53                                                                                                                                                                                 |

|   |                    | 3.5.1                                                                                                               | Capacitor Sizing and Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53                                                                                                                                                                                 |

|   |                    | 3.5.2                                                                                                               | Open Loop DC-Gain of the Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54                                                                                                                                                                                 |

|   |                    | 3.5.3                                                                                                               | Settling of the Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55                                                                                                                                                                                 |

|   |                    |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                    |

| 4 | Circ               | nit Tecl                                                                                                            | nniques for Pipeline Analog-to-Digital Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61                                                                                                                                                                                 |

| 4 |                    |                                                                                                                     | nniques for Pipeline Analog-to-Digital Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>61</b><br>61                                                                                                                                                                    |

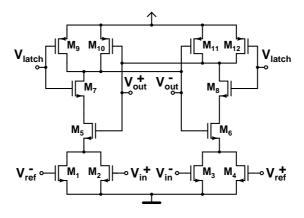

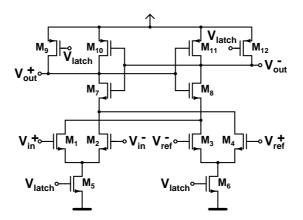

| 4 | <b>Circ</b><br>4.1 | Dynan                                                                                                               | nic Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61                                                                                                                                                                                 |

| 4 |                    |                                                                                                                     | nic Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61<br>62                                                                                                                                                                           |

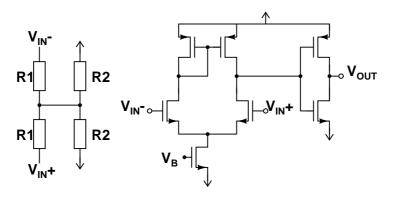

| 4 |                    | Dynan<br>4.1.1<br>4.1.2                                                                                             | nic Comparators          Resistive Divider Comparator          Differential Pair Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61<br>62<br>64                                                                                                                                                                     |

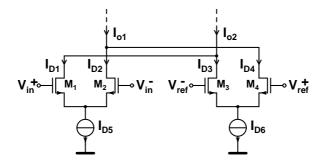

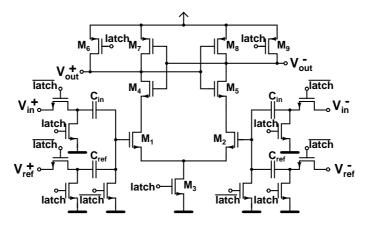

| 4 |                    | Dynam<br>4.1.1<br>4.1.2<br>4.1.3                                                                                    | nic Comparators       Resistive Divider Comparator       Differential Pair Comparator       Charge Distribution Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61<br>62<br>64<br>66                                                                                                                                                               |

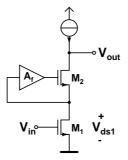

| 4 |                    | Dynan<br>4.1.1<br>4.1.2                                                                                             | nic Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61<br>62<br>64<br>66<br>68                                                                                                                                                         |

| 4 |                    | Dynam<br>4.1.1<br>4.1.2<br>4.1.3                                                                                    | nic Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61<br>62<br>64<br>66<br>68<br>68                                                                                                                                                   |

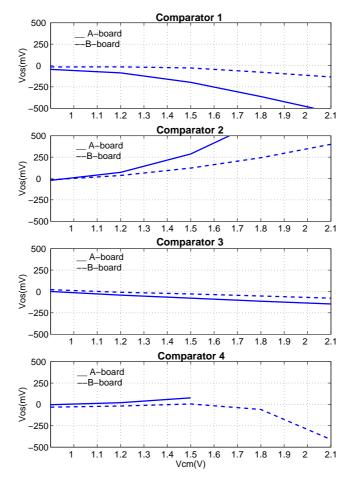

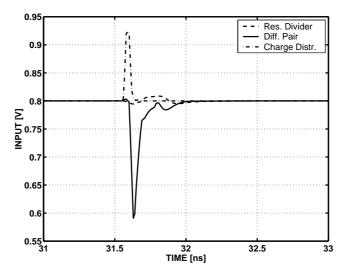

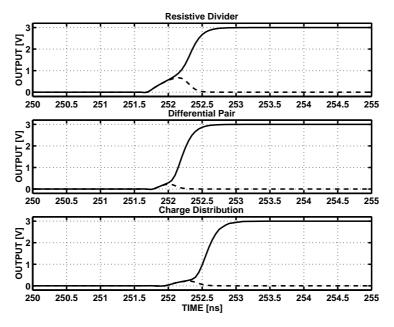

| 4 |                    | Dynam<br>4.1.1<br>4.1.2<br>4.1.3                                                                                    | hic Comparators       Resistive Divider Comparator         Differential Pair Comparator       Differential Pair Comparator         Charge Distribution Comparator       Experimental Results         4.1.4.1       Offset         4.1.4.2       Kickback Noise and Speed                                                                                                                                                                                                                                                                                                                    | 61<br>62<br>64<br>66<br>68<br>68<br>70                                                                                                                                             |

| 4 |                    | Dynan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5                                                                  | nic Comparators       Resistive Divider Comparator         Differential Pair Comparator       Differential Pair Comparator         Charge Distribution Comparator       Differential Results         4.1.4.1       Offset         4.1.4.2       Kickback Noise and Speed         Summary:       Dynamic Comparators                                                                                                                                                                                                                                                                         | <ul> <li>61</li> <li>62</li> <li>64</li> <li>66</li> <li>68</li> <li>68</li> <li>70</li> <li>71</li> </ul>                                                                         |

| 4 | 4.1                | Dynan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5                                                                  | hic Comparators       Resistive Divider Comparator         Differential Pair Comparator       Differential Pair Comparator         Charge Distribution Comparator       Experimental Results         4.1.4.1       Offset         4.1.4.2       Kickback Noise and Speed         Summary:       Dynamic Comparators                                                                                                                                                                                                                                                                         | <ul> <li>61</li> <li>62</li> <li>64</li> <li>66</li> <li>68</li> <li>68</li> <li>70</li> <li>71</li> <li>71</li> </ul>                                                             |

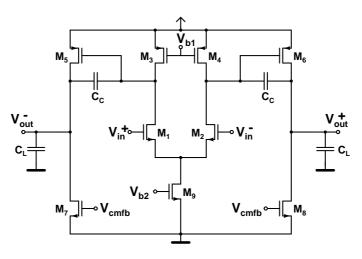

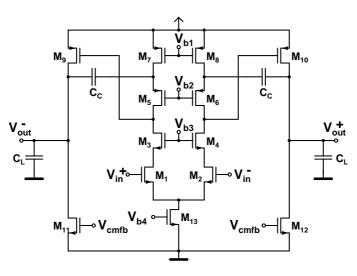

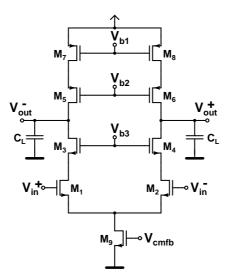

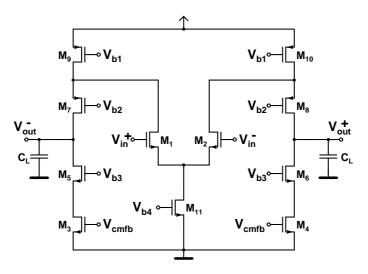

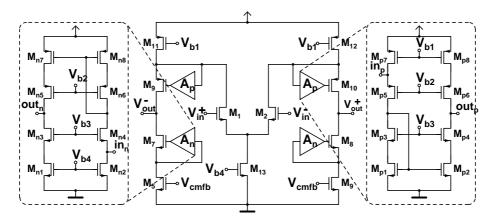

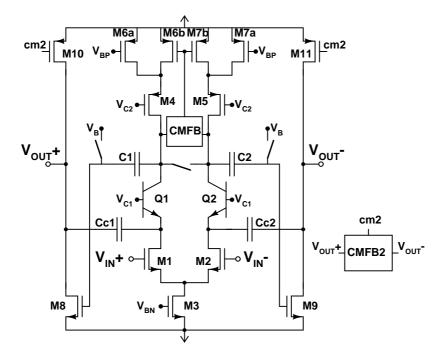

| 4 | 4.1                | Dynan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Operat<br>4.2.1                                               | nic Comparators       Resistive Divider Comparator         Differential Pair Comparator       Differential Pair Comparator         Charge Distribution Comparator       Differential Pair Comparator         Experimental Results       Differential Pair Comparator         4.1.4.1       Offset         4.1.4.2       Kickback Noise and Speed         Summary: Dynamic Comparators       Differential Pair Compensated Amplifier                                                                                                                                                         | <ul> <li>61</li> <li>62</li> <li>64</li> <li>66</li> <li>68</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> </ul>                                                             |

| 4 | 4.1                | Dynam<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Operat<br>4.2.1<br>4.2.2                                      | nic Comparators       Resistive Divider Comparator         Differential Pair Comparator       Differential Pair Comparator         Charge Distribution Comparator       Charge Distribution Comparator         Experimental Results       Charge Distribution Comparator         4.1.4.1       Offset         4.1.4.2       Kickback Noise and Speed         Summary: Dynamic Comparators       Charge Distribution         Miller Compensated Amplifier       Anuja-Style Compensated Amplifier                                                                                            | <ul> <li>61</li> <li>62</li> <li>64</li> <li>66</li> <li>68</li> <li>68</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>73</li> </ul>                                     |

| 4 | 4.1                | Dynan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Operat<br>4.2.1                                               | nic Comparators       Resistive Divider Comparator         Differential Pair Comparator       Differential Pair Comparator         Charge Distribution Comparator       Differential Pair Comparator         Experimental Results       Differential Pair Comparator         4.1.4.1       Offset         4.1.4.2       Kickback Noise and Speed         Summary: Dynamic Comparators       Differential Pair Compensated Amplifier         Ahuja-Style Compensated Amplifier       Differential Pair Comparators                                                                           | <ul> <li>61</li> <li>62</li> <li>64</li> <li>66</li> <li>68</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>74</li> </ul>                                     |

| 4 | 4.1                | Dynan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Operat<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                    | nic Comparators       Resistive Divider Comparator         Differential Pair Comparator       Differential Pair Comparator         Charge Distribution Comparator       Differential Pair Comparator         Experimental Results       Differential Pair Comparator         4.1.4.1       Offset         4.1.4.2       Kickback Noise and Speed         Summary: Dynamic Comparators       Differential Pair Compensated Amplifier         Miller Compensated Amplifier       Differential Pair Compensated Amplifier         Folded Cascode Amplifier       Differential Pair Comparators | <ul> <li>61</li> <li>62</li> <li>64</li> <li>66</li> <li>68</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>74</li> <li>75</li> </ul>                         |

| 4 | 4.1                | Dynan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Operat<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                    | nic Comparators       Resistive Divider Comparator         Differential Pair Comparator       Differential Pair Comparator         Charge Distribution Comparator       Experimental Results         4.1.4.1       Offset         4.1.4.2       Kickback Noise and Speed         Summary: Dynamic Comparators       Summary: Dynamic Comparators         ional Amplifiers       Anulia-Style Compensated Amplifier         Folded Cascode Amplifier       Experimental Results                                                                                                              | <ul> <li>61</li> <li>62</li> <li>64</li> <li>66</li> <li>68</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>74</li> </ul>                                     |

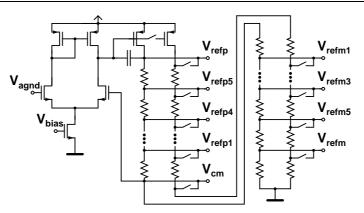

| 4 | 4.1                | Dynam<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Operat<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Voltage         | hic Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>61</li> <li>62</li> <li>64</li> <li>66</li> <li>68</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>74</li> <li>75</li> <li>78</li> <li>78</li> </ul> |

| 4 | 4.1                | Dynan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Operat<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Voltag<br>4.3.1 | nic Comparators       Resistive Divider Comparator         Differential Pair Comparator       Differential Pair Comparator         Charge Distribution Comparator       Experimental Results         4.1.4.1       Offset         4.1.4.2       Kickback Noise and Speed         Summary: Dynamic Comparators       Summary: Dynamic Comparators         ional Amplifiers       Anulia-Style Compensated Amplifier         Folded Cascode Amplifier       Experimental Results                                                                                                              | <ul> <li>61</li> <li>62</li> <li>64</li> <li>66</li> <li>68</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>74</li> <li>75</li> <li>78</li> </ul>             |

| 5 | Ana  | log-to-D                         | Digital Converters for Direct Conversion Receivers            | 85  |

|---|------|----------------------------------|---------------------------------------------------------------|-----|

|   | 5.1  | Single-                          | Chip Direct Conversion Receivers                              | 85  |

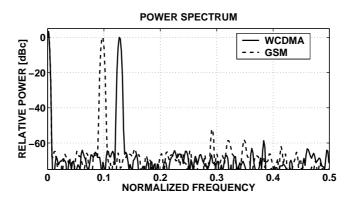

|   |      | 5.1.1                            | Wide-Band CDMA                                                | 87  |

|   | 5.2  | Embed                            | ded A/D Converters of Direct Conversion Receivers             | 87  |

|   |      | 5.2.1                            | Resolution and Sample Rate                                    | 87  |

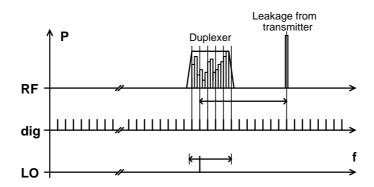

|   |      | 5.2.2                            | Noise and Clock Distortion                                    | 88  |

|   |      | 5.2.3                            | Interfaces                                                    | 91  |

|   |      |                                  | 5.2.3.1 Input                                                 | 91  |

|   |      |                                  | 5.2.3.2 Output                                                | 92  |

|   |      | 5.2.4                            | Power Dissipation and Area                                    | 93  |

|   | 5.3  | Reconf                           | figurable Pipeline A/D Converters                             | 94  |

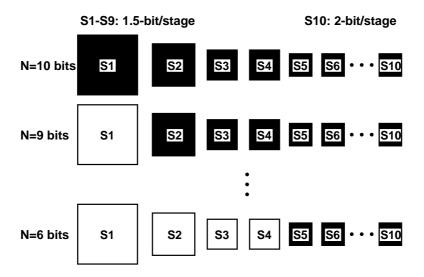

|   |      | 5.3.1                            | Resolution                                                    | 95  |

|   |      | 5.3.2                            | Sample Rate                                                   | 97  |

|   | 5.4  | Applic                           | ation Case I: A Single-Amplifier 6-bit CMOS Pipeline A/D Con- |     |

|   |      | verter f                         | for WCDMA Receivers                                           | 98  |

|   |      | 5.4.1                            | Introduction                                                  | 98  |

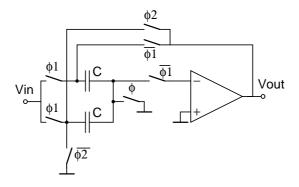

|   |      | 5.4.2                            | Circuit Description                                           | 98  |

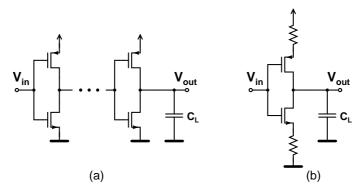

|   |      |                                  | 5.4.2.1 Amplifier Sharing                                     | 99  |

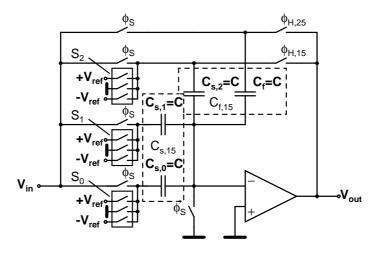

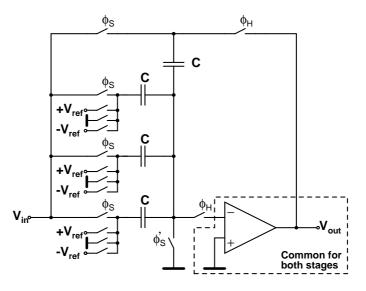

|   |      |                                  | 5.4.2.2 Multiplying D/A Converter (MDAC)                      | 100 |

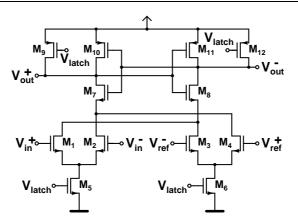

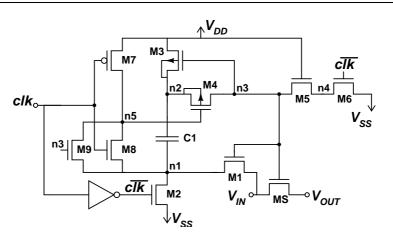

|   |      |                                  | 5.4.2.3 Differential Pair Dynamic Comparator                  | 100 |

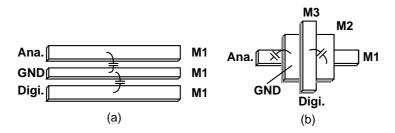

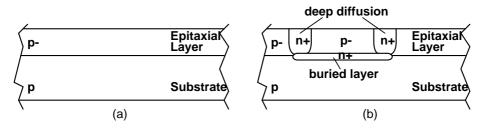

|   |      |                                  | 5.4.2.4 Substrate Noise Reduction                             | 101 |

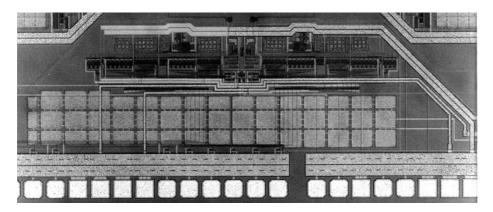

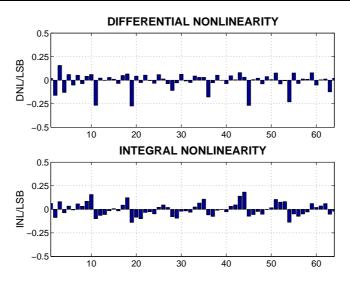

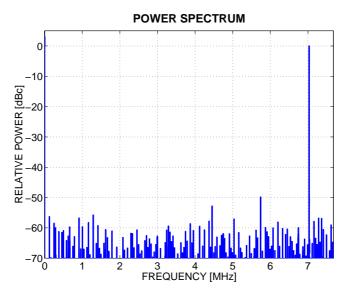

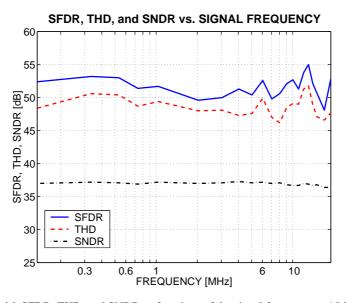

|   |      | 5.4.3                            | Experimental Results                                          | 103 |

|   |      | 5.4.4                            | Conclusions                                                   | 106 |

|   | 5.5  | Applic                           | ation Case II: A Dual-Mode Pipeline A/D Converter for Direct  |     |

|   |      | Conver                           | rsion Receivers                                               | 106 |

|   |      | 5.5.1                            | Introduction                                                  | 106 |

|   |      | 5.5.2                            | Circuit Description                                           | 107 |

|   |      | 5.5.3                            | Simulation Results                                            | 110 |

|   |      | 5.5.4                            | Conclusions                                                   | 110 |

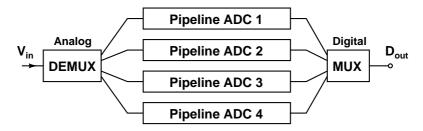

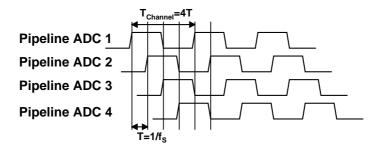

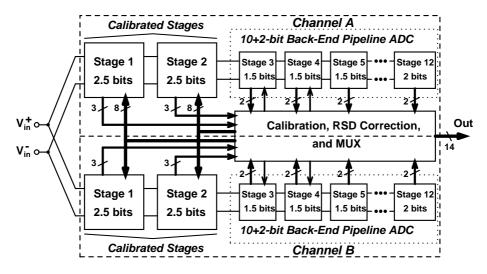

| 6 | Para | Parallel Pipeline A/D Converters |                                                               |     |

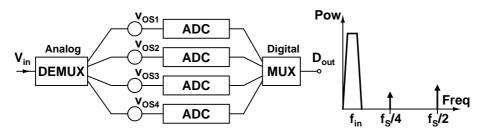

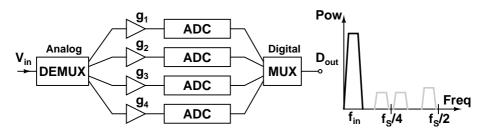

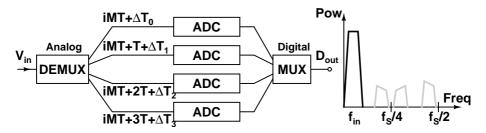

|   | 6.1  | Time-I                           | nterleaved Parallel Pipeline A/D Converter                    | 115 |

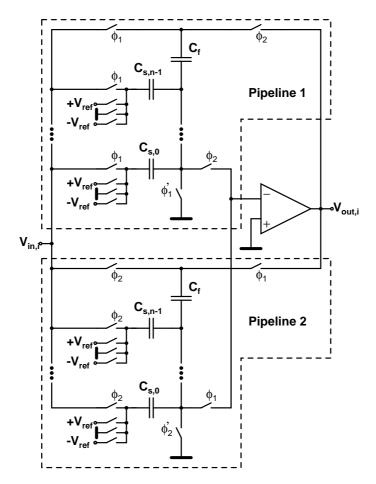

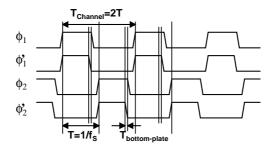

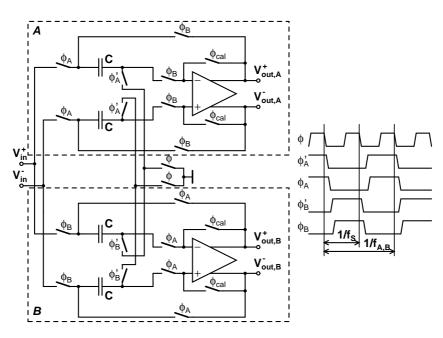

|   | 6.2  | Double-Sampling                  |                                                               |     |

|   | 6.3  | Perform                          | nance Limitations of Parallel Pipeline A/D Converters         | 118 |

|   |      | 6.3.1                            | Channel Offset Mismatch                                       | 118 |

|   |      | 6.3.2                            | Channel Gain Mismatch                                         | 120 |

|   |      | 6.3.3                            | Timing Mismatch                                               | 121 |

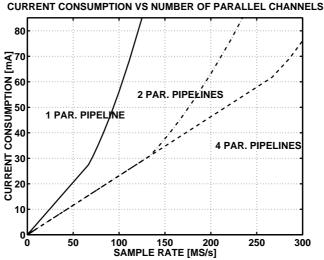

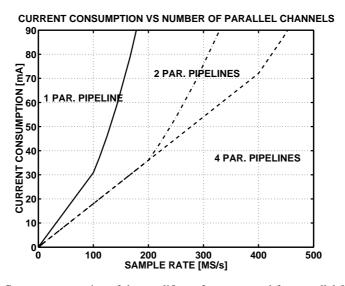

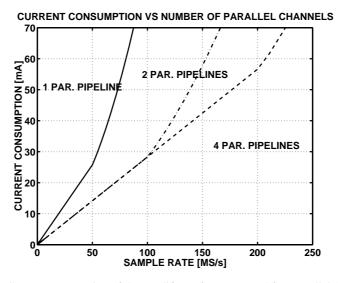

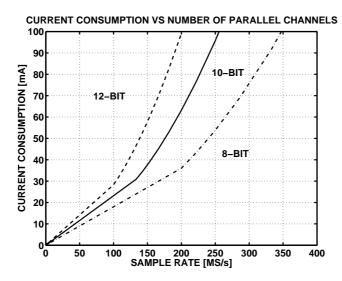

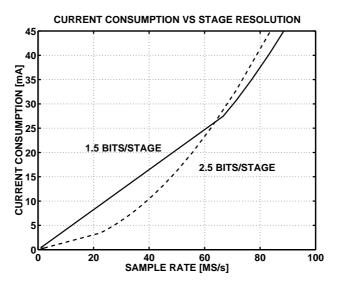

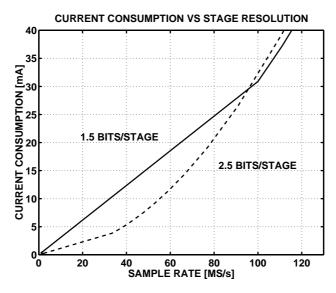

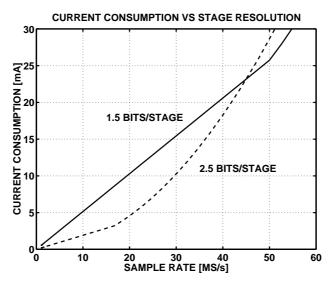

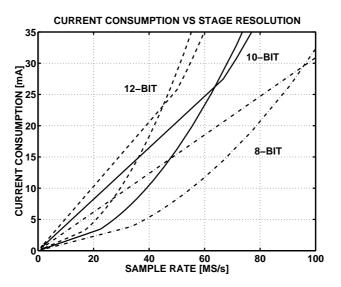

|                                          | 6.4 | Optimizing the Parallel Pipeline A/D Converter Topology for Power |                                                                    |  |  |  |  |

|------------------------------------------|-----|-------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|

|                                          |     | <ul><li>6.4.1 Number of Parallel Channels</li></ul>               |                                                                    |  |  |  |  |

|                                          |     |                                                                   |                                                                    |  |  |  |  |

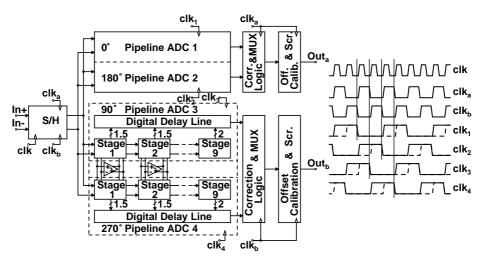

|                                          | 6.5 | Application Case: A 10-bit 200-MS/s CMOS Parallel Pipeline A/D    |                                                                    |  |  |  |  |

|                                          |     | Converter                                                         |                                                                    |  |  |  |  |

|                                          |     | 6.5.1                                                             | Introduction                                                       |  |  |  |  |

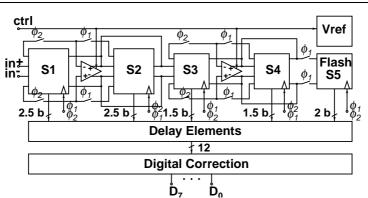

|                                          |     | 6.5.2                                                             | Circuit Description                                                |  |  |  |  |

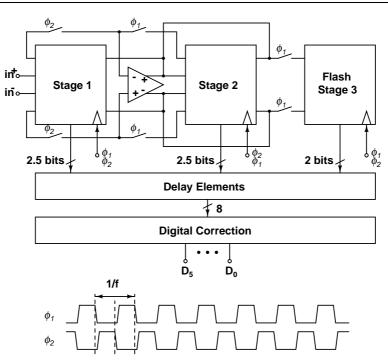

|                                          |     |                                                                   | 6.5.2.1 Pipeline Component A/D Converters                          |  |  |  |  |

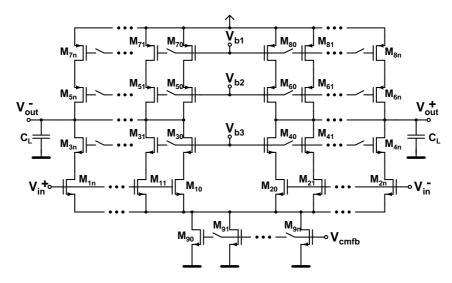

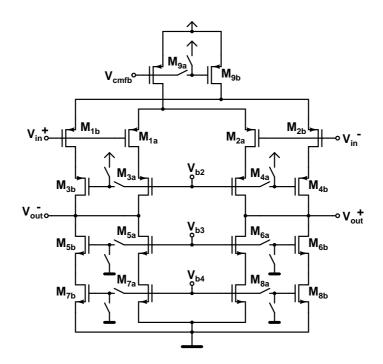

|                                          |     |                                                                   | 6.5.2.2 High-Swing Regulated Folded Cascode Amplifier 132          |  |  |  |  |

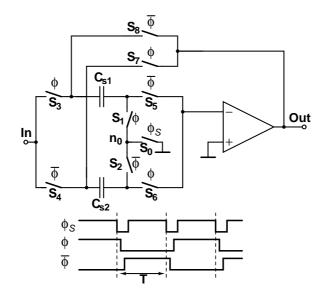

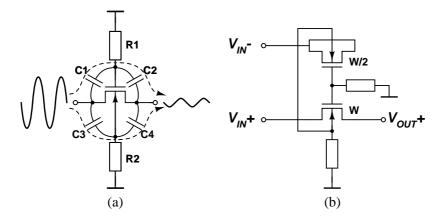

|                                          |     |                                                                   | 6.5.2.3 Timing Skew Insensitive Double-Sampled S/H Circuit 133     |  |  |  |  |

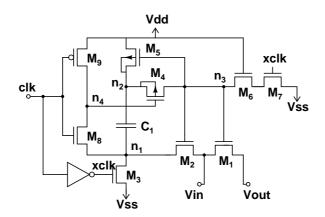

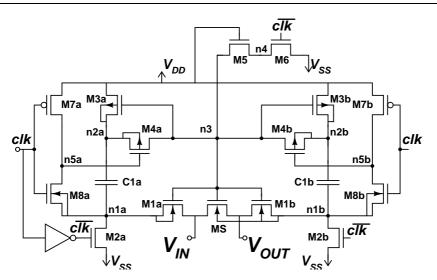

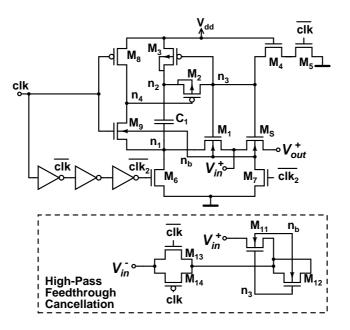

|                                          |     |                                                                   | 6.5.2.4 Bootstrapped MOS-Switch                                    |  |  |  |  |

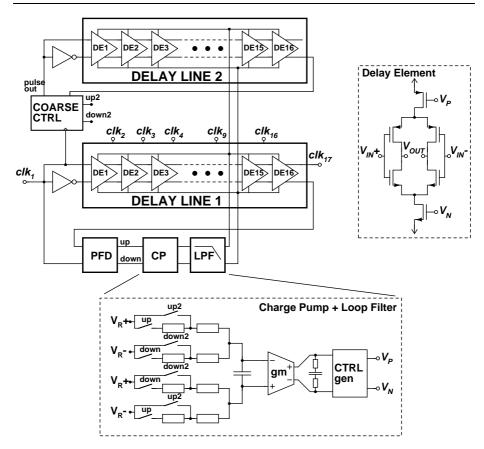

|                                          |     |                                                                   | 6.5.2.5 Clock Generation                                           |  |  |  |  |

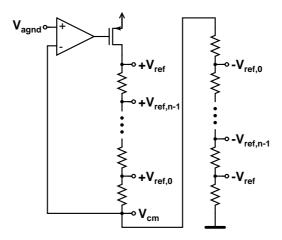

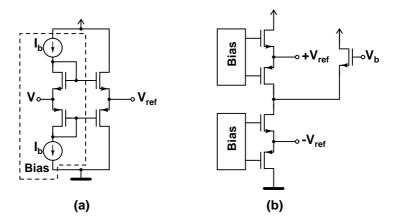

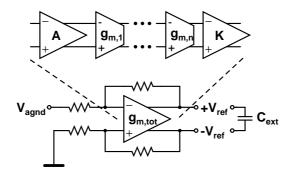

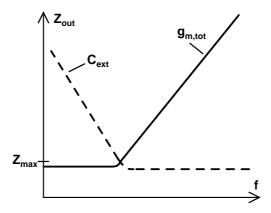

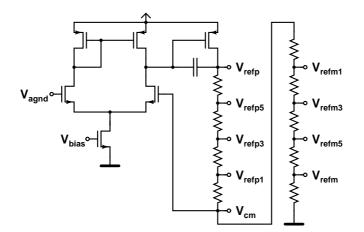

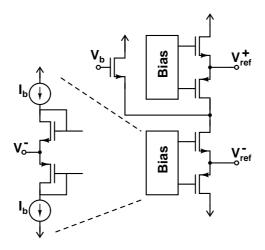

|                                          |     |                                                                   | 6.5.2.6 Reference Voltage Driver                                   |  |  |  |  |

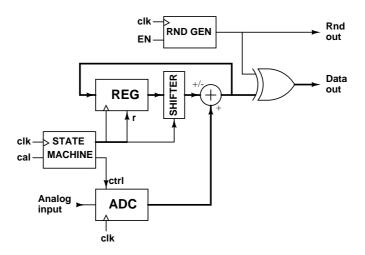

|                                          |     |                                                                   | 6.5.2.7 Offset Calibration and Output Scrambling 136               |  |  |  |  |

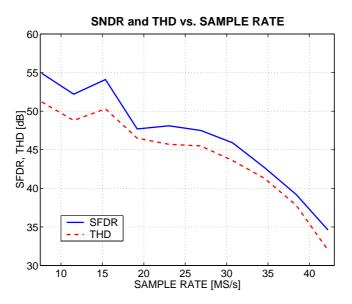

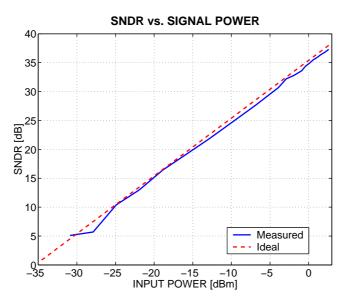

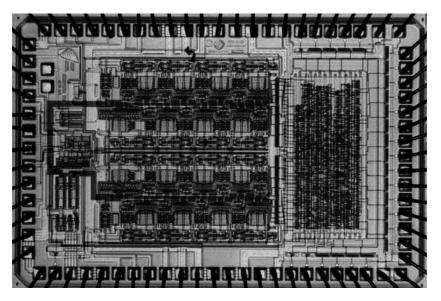

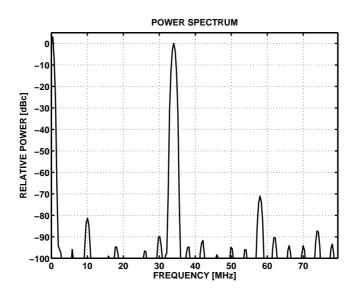

|                                          |     | 6.5.3                                                             | Experimental Results                                               |  |  |  |  |

|                                          |     | 6.5.4                                                             | Conclusions                                                        |  |  |  |  |

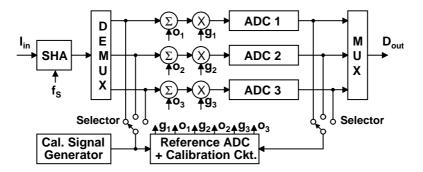

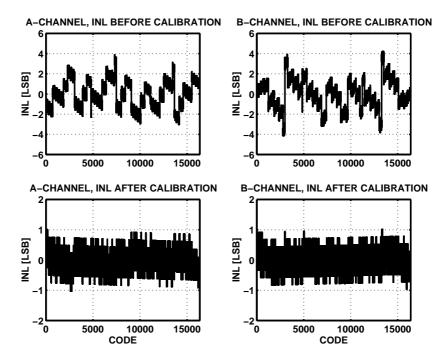

| 7 Calibration of Pipeline A/D Converters |     |                                                                   |                                                                    |  |  |  |  |

| '                                        | 7.1 |                                                                   | of Pipeline A/D Converters145Sources in Pipeline A/D Converters145 |  |  |  |  |

|                                          | 7.2 |                                                                   | ation Methods                                                      |  |  |  |  |

|                                          | 7.2 | 7.2.1                                                             | Capacitor Error Averaging                                          |  |  |  |  |

|                                          |     | 7.2.2                                                             | Analog Calibration Methods                                         |  |  |  |  |

|                                          |     | 7.2.3                                                             | Digital Calibration Methods                                        |  |  |  |  |

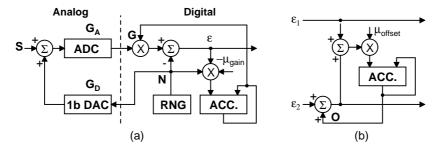

|                                          |     | 7.2.4                                                             | Background Calibration                                             |  |  |  |  |

|                                          |     | 7.2.5                                                             | Timing Error Calibration                                           |  |  |  |  |

|                                          |     | 7.2.6                                                             | Calibration Methods: Summary                                       |  |  |  |  |

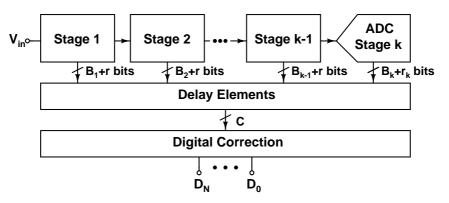

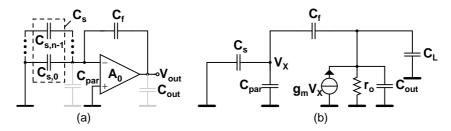

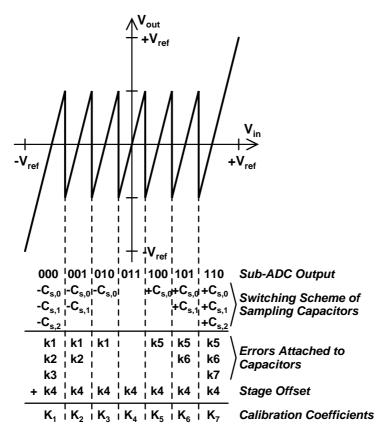

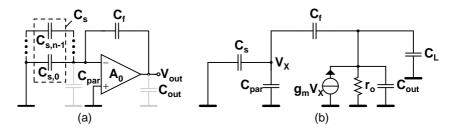

|                                          | 7.3 |                                                                   | pped Digital Self-Calibration                                      |  |  |  |  |

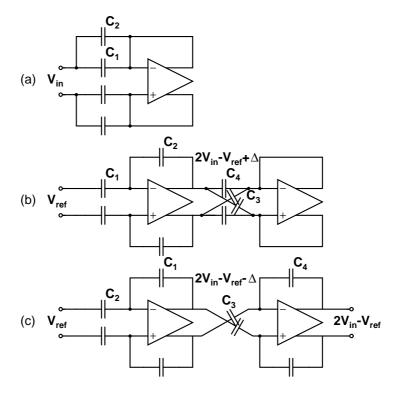

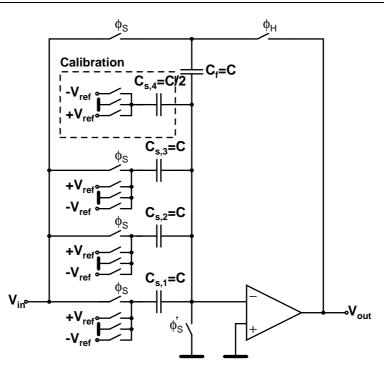

|                                          |     | 7.3.1                                                             | Capacitor Mismatch Correction                                      |  |  |  |  |

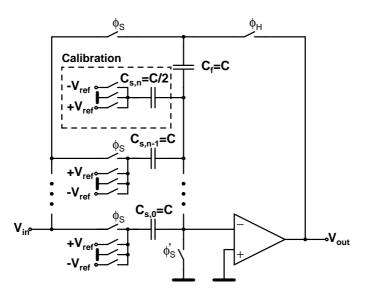

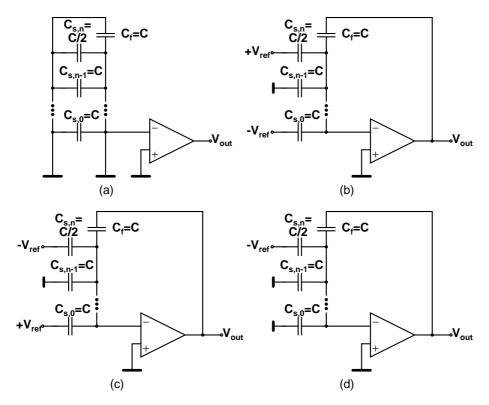

|                                          |     | 7.3.2                                                             | Calibration MDAC                                                   |  |  |  |  |

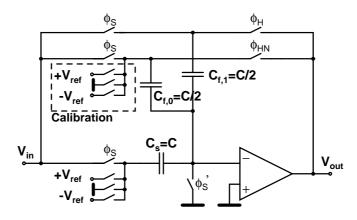

|                                          |     | 7.3.3                                                             | Enhanced Gain Stage                                                |  |  |  |  |

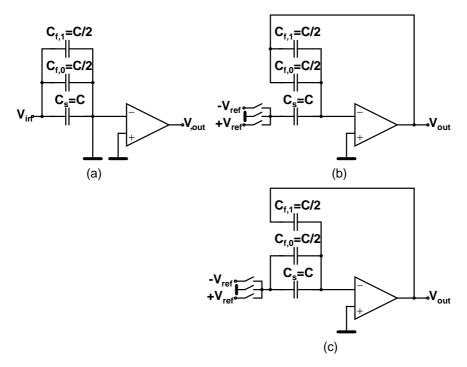

|                                          |     | 7.3.4                                                             | Calculation of Calibration Coefficients                            |  |  |  |  |

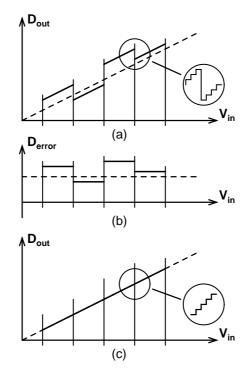

|                                          |     | 7.3.5                                                             | Gain Error Calibration                                             |  |  |  |  |

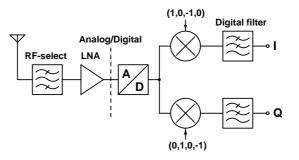

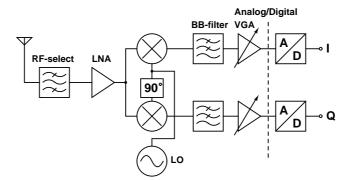

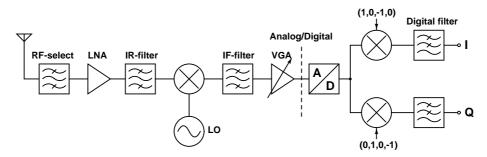

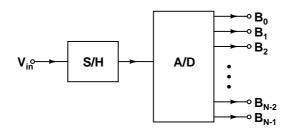

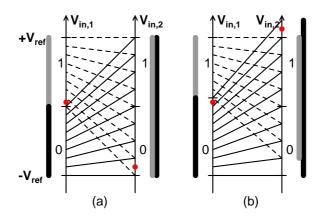

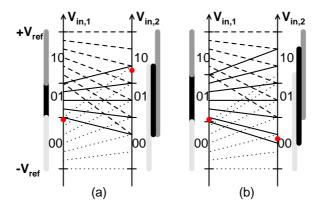

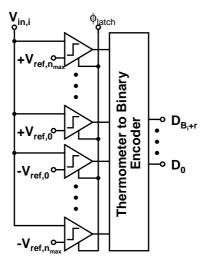

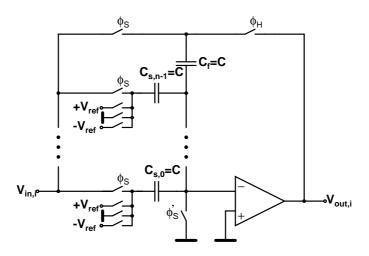

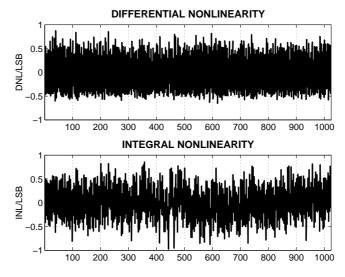

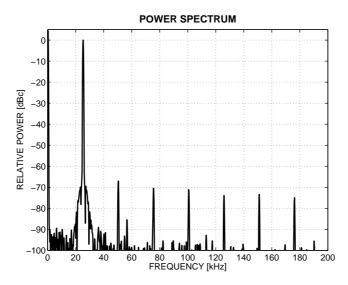

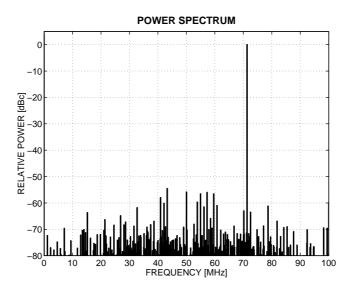

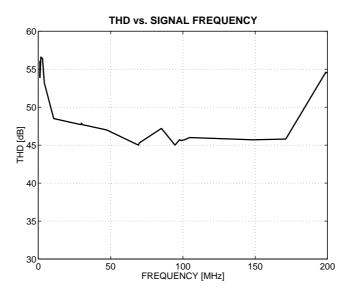

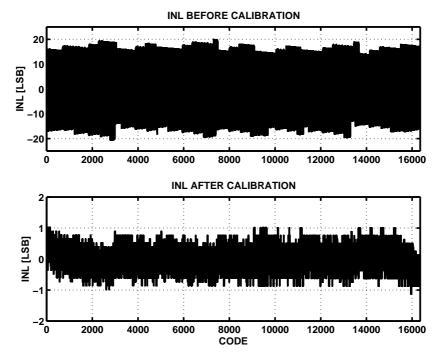

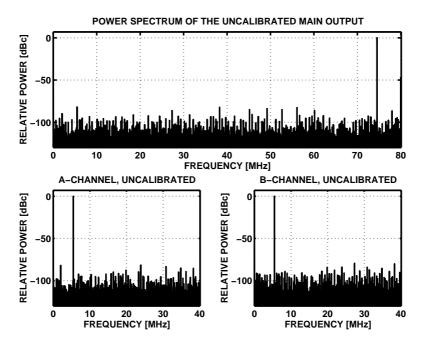

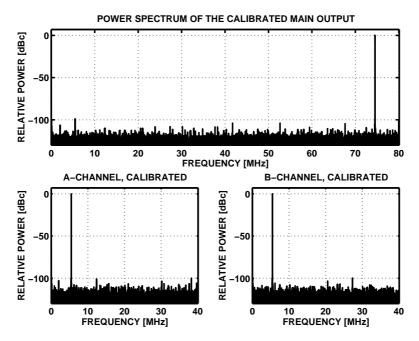

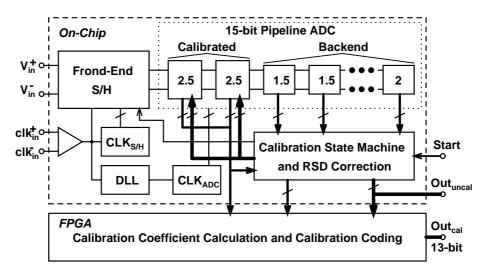

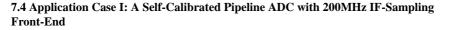

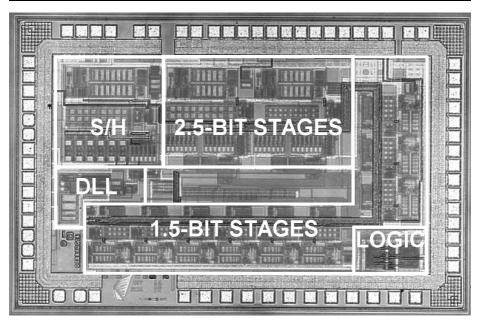

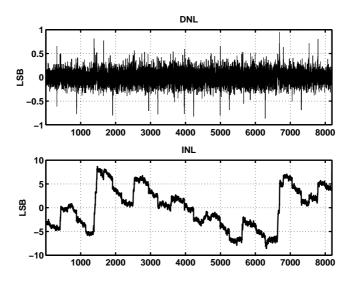

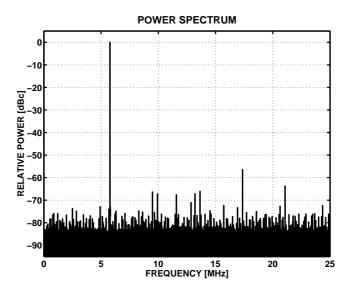

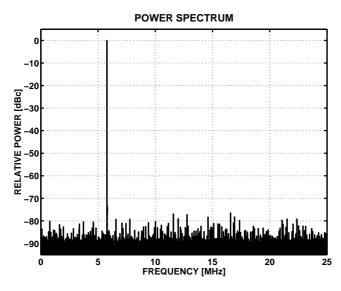

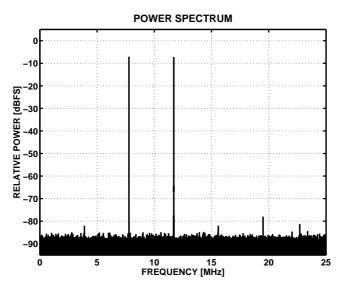

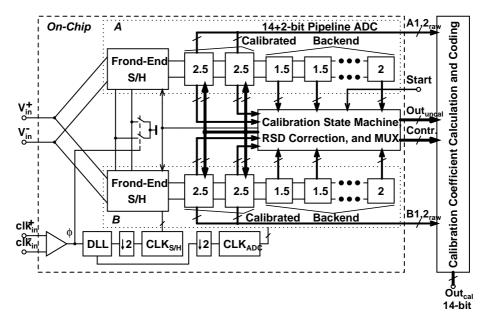

|                                          |     | 7.3.6                                                             | Accuracy Considerations                                            |  |  |  |  |