| Espoo 2004                                                   | Publication 8                                             |

|--------------------------------------------------------------|-----------------------------------------------------------|

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

| LOW-POWER PFC AND FORWA                                      | ARD CONVERTERS –                                          |

| METHODS TO IMPROVE PERF                                      | ORMANCE                                                   |

| Thesis for the degree of Doctor of Science in Tec            | chnology                                                  |

|                                                              |                                                           |

| Vesa Tuomainen                                               |                                                           |

|                                                              |                                                           |

| Dissertation for the degree of Doctor of Science in Techno   | plogy to be presented with due permission of              |

| the Department of Electrical and Communications Engin        | eering for public examination and debate in               |

| Auditorium S4 at Helsinki University of Technology (Espnoon. | 500, Finland) on the 4 <sup>th</sup> of June, 2004, at 12 |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

|                                                              |                                                           |

| Helsinki University of Technology                            |                                                           |

| Department of Electrical and Communications Engineering      | 3                                                         |

| Power Electronics Laboratory                                 |                                                           |

| Teknillinen Korkeakoulu                                      |                                                           |

| Sähkö- ja tietoliikennetekniikan osasto                      |                                                           |

| Sanko- ja tietoinkennetekinikan osasto                       |                                                           |

Tehoelektroniikan laboratorio

Helsinki University of Technology Institute of Intelligent Power Electronics Publications

Distribution:

Helsinki University of Technology

Power Electronics Laboratory

P.O. Box 3000

FIN-02015 HUT

Fax: +358-9-451 2432

© Vesa Tuomainen and Helsinki University of Technology

ISBN 951-22-7098-6

ISSN 1456-0445

Otamedia Oy

Espoo 2004

### **Abstract**

The number of power electronic appliances is growing. Power electronic converters can be used to convert the ac line voltage to a dc voltage, and further through dc-dc conversion stages to desired dc voltages for different loads. This Thesis deals with three single-stage power factor correction converters and a forward type dc-dc converter.

Single-stage converters can be considered as low cost solutions for power factor correction. This is because only one active switching stage is used in the converters. Small signal and steady state analysis are performed for the dither converter. A resonant type snubber is analyzed for the BIFRED and BIBRED converters and a new type of clamp circuit is developed for the BIFRED converter.

The dc-dc conversion part of the Thesis deals with a forward converter with active clamp circuit and self-driven synchronous rectifiers. Resonant transition of the converter is analyzed in detail. Emphasis of the research is on improving the efficiency of the converter. Findings show that the minimization of the turn-on losses in the converter is not necessarily advantageous. The analysis is verified with a 3.4 V and 30 A prototype converter.

## **Preface**

It has been a great pleasure for me to do this Thesis. In this Preface I want to thank all of those people who have helped and supported me in my work.

First of all, I am grateful to Professor Jorma Kyyrä, who supervised the research, for his guidance, invaluable advice and suggestions for this Thesis and for the research behind it. I also want to thank the former heads of the laboratory, Professors Jorma Luomi and Seppo Ovaska.

I want to thank all the people who work and have worked, during the time I have worked for the laboratory, at the Power Electronics laboratory for creating a pleasant and enthusiastic atmosphere. Special thanks are due to secretary of the laboratory Anja Meuronen and to laboratory technician Ilkka Hanhivaara for their assistance in practical matters. I also want to thank the former secretaries Ulla Ahlgren, Tuula Mylläri and Leena Väisänen.

I also want to thank my present and former colleagues for their contribution to my research. M.Sc. Juha Wallius, D.Sc. Vlad Grigore, D.Sc. Veli-Matti Leppänen, M.Sc. Marko Hinkkanen, M.Sc. Petri Mäki-Ontto and M.Sc. Konstantin Kostov

The research work was financially supported by the Graduate School of Electrical Engineering. Some of the research was done in the framework of two projects: the PFC project and the EFF project, which were financially supported by TEKES (the Technology Development Centre of Finland), ABB Industry Oy and Efore Oyj. I want to thank the Graduate School for giving this opportunity to prepare and write this Thesis and I also want to express my thanks to all of the board members of the two projects for setting goals and providing valuable ideas.

I express my gratitude to Tekniikan edistämissäätiö (TES), Finnish Cultural Foundation, Ulla Tuomisen säätiö and Tekniilisen korkeakoulun tukisäätiö for their financial support for this Thesis.

Suuri kiitos kuuluu myös omaisilleni, isovanhemmilleni, sedilleni, tädeilleni ja rakkaille serkuilleni. Erityinen kiitos kuuluu vanhemmilleni, Tapani ja Liisa Tuomaiselle, jotka ovat aina tukeneet työtäni ja kannustaneet minua eteenpäin, sekä henkisesti että taloudellisesti. Ajoittain on saattanut vaikuttaa jopa siltä, että he ovat olleet, jos mahdollista, vieläkin innokkaampia työni edistymisen suhteen kuin minä itse. Lisäksi olen suuressa kiitollisuudenvelassa vanhemmalle veljelleni, DI Petri Tuomaiselle, joka on aina ollut minulle esimerkkinä ja innoituksen lähteenä. Kiitos kaikille.

"Taide on yksi luonnon monista ilmaisukeinoista, niinkuin leivosen laulu, niinkuin myrskyävä meri, niinkuin tuulen humina puissa. Tästä seuraa, ettei taiteen tarkoitus voi olla jäljitellä luontoa, vaan tulkita sitä" V.A. koskenniemi,Matkasauva, WSOY Porvoo 1926, s. 47.

Otaniemi, June 2004 Vesa Tuomainen

# **Contents**

| List | t of Publications                              | Ç  |  |  |  |

|------|------------------------------------------------|----|--|--|--|

| List | t of abbreviations                             | 11 |  |  |  |

| List | _ist of symbols′                               |    |  |  |  |

| 1    | Introduction                                   | 15 |  |  |  |

| 1.1  | Ac-dc conversion                               | 15 |  |  |  |

| 1.2  | Dc-dc conversion                               | 17 |  |  |  |

| 2    | Background of power factor correction          | 21 |  |  |  |

| 2.1  | Standard IEC 61000-3-2                         | 21 |  |  |  |

| 2.2  | Line harmonics in switched mode power supplies | 23 |  |  |  |

| 2.3  | Basic definitions in power factor correction   | 25 |  |  |  |

| 3    | Single-stage power factor correction circuits  | 27 |  |  |  |

| 3.1  | General                                        | 27 |  |  |  |

| 3.2  | Dither converter                               | 29 |  |  |  |

|      | 3.2.1 General                                  | 29 |  |  |  |

|      | 3.2.2 Steady state analysis                    | 30 |  |  |  |

|      | 3.2.3 Small signal analysis                    | 33 |  |  |  |

| 3.3  | BIFRED and BIBRED converters                   | 40 |  |  |  |

|      | 3.3.1 General                                  | 40 |  |  |  |

|      | 3.3.2 Research background                      | 41 |  |  |  |

|      | 3.3.3 Resonant type snubber                    | 42 |  |  |  |

|      | 3.3.4 Passive clamp circuit for BIFRED         | 45 |  |  |  |

| 4    | Forward type dc-dc converter                   | 53 |  |  |  |

| 4.1  | Passive reset methods for forward transformer  | 53 |  |  |  |

|      | 4.1.1 Third winding scheme                     | 54 |  |  |  |

|      | 4.1.2 RCD-clamp                                | 55 |  |  |  |

|      | 4.1.3 Non-dissipative snubber                            | 57 |

|------|----------------------------------------------------------|----|

|      | 4.1.4 Resonant reset                                     | 58 |

| 4.2  | Forward with active clamp                                | 59 |

| 4.3  | Reset circuits and self-driven synchronous rectification | 61 |

|      | 4.3.1 Introduction                                       | 61 |

|      | 4.3.2 Summary of the reset schemes                       | 62 |

| 4.4  | Low voltage conversion with forward with active clamp    | 64 |

|      | 4.4.1 Introduction                                       | 64 |

|      | 4.4.2 Research background                                | 65 |

| 5    | Description of the laboratory setup                      | 73 |

| 5.1  | Laboratory equipment                                     |    |

| 5.2  | BIFRED prototype                                         |    |

| 5.3  | FAC prototype                                            |    |

| 6    | Summaries of the publications                            | 75 |

| 7    | Contribution of this Thesis                              | 79 |

| 8    | Conclusions                                              | 81 |

| Refe | erences                                                  | 85 |

| Арр  | endix A                                                  | 95 |

| Sche | matics of the BIFRED and FAC prototype converters        | 95 |

## **List of Publications**

This thesis consists of an overview and the following publications:

- P[1] Tuomainen, V. and Kyyrä, J. (2002). Steady state analysis of modified dither converter. *Proceedings of Nordic Workshop on Power and Industrial Electronics, NORPIE 2002*, Stockholm, Sweden, 12-14 August 2002, on CD-ROM.

- P[2] Tuomainen, V. and Kyyrä, J. (2003). Small signal analysis of dither converter with a tapped transformer. *Proceedings of 10<sup>th</sup> European Conference on Power Electronics and Applications, EPE 2003*, Toulouse, France, 2-4 September 2003, on CD-ROM.

- P[3] Tuomainen, V. and Kyyrä, J. (2002). Analysis of a lossless snubber for BIFRED and BIBRED. *Proceedings of 10<sup>th</sup> International Power Electronics and Motion Control Conference, EPE-PEMC 2002*, Cavtat & Dubrovnik, Croatia, 9-11 September 2002, on CD-ROM.

- P[4] Tuomainen, V. (2003). A Passive clamp circuit for BIFRED converter. Proceedings of 18<sup>th</sup> Annual IEEE Applied Power Electronics Conference and Exposition, APEC'03, Miami Beach, Florida, 9-13 February 2003, Vol. 2, pp. 658-663.

- P[5] Tuomainen, V. and Kyyrä, J. (2002). Improved switching condition for a forward with active clamp. *Proceedings of 10<sup>th</sup> International Power Electronics and Motion Control Conference, EPE-PEMC 2002*, Cavtat & Dubrovnik, Croatia, 9-11 September 2002, on CD-ROM.

- P[6] Tuomainen, V. and Kyyrä, J. (2002). Effect of the magnetization inductance on forward converter with active clamp. *Proceedings of Nordic Workshop on Power* and *Industrial Electronics*, *NORPIE 2002*, Stockholm, Sweden, 12-14 August 2002, on CD-ROM.

- P[7] Tuomainen, V. and Kyyrä, J. (2003). Effect of resonant transition on efficiency of forward converter with active clamp and self-driven sr's. *Proceedings of 34<sup>th</sup> Annual IEEE Power Electronic Specialists Conference, PESC'03*, Acapulco, Mexico, 15-19 June 2003, Vol. 3, pp. 1333-1338. Provisionally accepted for publication in *IEEE Transactions on Power Electronics*.

- P[8] Tuomainen, V. and Kyyrä, J. (2003). Design considerations of resonant transition forward converter with active clamp. *Proceedings of 10<sup>th</sup> European Conference on Power Electronics and Applications, EPE 2003*, Toulouse, France, 2-4 September 2003, on CD-ROM.

The research reported in publications P[1] - P[8] was performed by the Author alone, who also wrote the publications. However, all work was carried out under the supervision of Professor Jorma Kyyrä, who read the publications and gave the author constructive ideas and valuable suggestions.

## List of abbreviations

A Ampere

A Area

AC Alternating current

BIBREB Boost Integrated with Buck Rectifier/Energy storage /Dc-dc converter

BIFRED Boost Integrated with Flyback Rectifier/Energy storage/Dc-dc

converter

C Capacitor

CCM Continuous conduction mode

D Diode

DC Direct current

DCM Discontinuous conduction mode

ESR Equivalent series resistance

FAC Forward with active clamp

Hz Hertz

IC Integrated circuit

kHz Kilohertz

L Inductor

MOSFET Metal oxide semiconductor field effect transistor

RMS Root mean square

PFC Power factor correction

PCB Printed circuit board

SMPS Switched mode power supply

V Volt

ZVS Zero voltage switching

## List of symbols

C Capacitance

*DPF* Displacement power factor

$\hat{d}_1$  Duty ratio variation

$d_1$  Duty ratio

$D_1$  Steady state duty ratio

$D_{1,\text{max}}$  Maximum duty cycle

$D_2$  Relative portion of switching cycle during which the current of an

inductor falls from peak value to zero

$D_3$  Relative portion of switching cycle during which the current of a

DCM inductor is zero

*f* Frequency

$f_0$  Resonance frequency

$f_{\text{line}}$  Frequency of the line voltage

$f_{\rm s}$  Switching frequency

*i*<sub>C</sub> Capacitor current

$\langle i_{C,+} \rangle_{Tline}$  Average current brought to capacitor C during a line cycle

$\langle i_{\text{C,-}} \rangle_{\text{Tline}}$  Average current taken from capacitor C during a line cycle

$\langle i_{\rm C,+} \rangle_{T_{\rm S}}$  Average current brought to capacitor C during a switching cycle

$\langle i_{C,-} \rangle_{T_s}$  Average current taken from capacitor C during a switching cycle

*i*<sub>D</sub> Diode current

$I_{\rm D}$  Average of diode current

$i_{in}$  Line current / input current

$i_{in,1}$  Line frequency component of the line current

$\langle i_{\rm in} \rangle_{T_{\rm S}}$  Average line current during a switching cycle

$I_{\text{in,peak}}$  Peak value of the line current

$I_{\text{in,rms},1}$  Rms value of the line frequency component of line current

$I_{\text{in.rms}}$  Rms value of the line current

$I_{\text{in,rms}, n}$  Rms value of n:th harmonic of the line current

$i_{\rm L}$  Inductor current

*I*<sub>L</sub> Peak value of inductor current\*

$I_{L,max}$  Maximum peak value of inductor current

$I_{\rm M}, I_{\rm LM}$ , Peak value of the magnetizing current of a transformer

$L_{\rm M}, L_{\rm m}$  Magnetizing inductance of a transformer

$L_{lk}$  Leakage inductance

*n n*:th multiple of the line frequency

$N_1$  Number of turns in the primary winding of a transformer

$N_2$  Number of turns in the secondary winding of a transformer

$N_3$  Number of turns in a tertiary winding of a transformer

$N_4$  Number of turns in a fourth winding of a transformer

$N_{1A}$  Number of turns in the upper part of the primary winding of a tapped

transformer

$N_{1B}$  Number of turns in the lower part of the primary winding of a tapped

transformer

$N_1/N_2$  Turns ratio of a transformer

P Power

*PF* Power factor

$R_{load}$ ,  $R_{l}$  Load resistance

S Apparent power

t Time

$t_{\rm off}$  Switch off time of a switching cycle

$t_{\rm on}$  Switch on time of a switching cycle

THD Total harmonic distortion

$T_{\text{line}}$  Length of a line cycle, inverse of the line frequency

$T_{\rm s}$  Length of a switching cycle, inverse of the switching frequency

$v_{\rm DS}$  Drain-source voltage of a MOSFET

$v_{\rm in}$  Sinusoidal line voltage,  $V_{\rm in} \sin(\omega_{\rm line} t)$

$v_{\text{in},1}$  line frequency component of the line voltage

$|v_{\rm in}|$  Rectified line voltage

$\langle |v_{\rm in}| \rangle_{T_{\rm S}}$  Average of the rectified line voltage during a switching cycle

$V_{\rm in}$  Peak value of the line voltage\*

$V_{\text{in,rms},1}$  RMS value of the line frequency component of the line voltage

$V_{\rm in,rms}$  RMS value of the line voltage

$v_{\rm C}$  Voltage of a capacitor

$V_{\rm C}$  Dc-voltage of a capacitor or control voltage

$V_{\text{C1b}}$  Dc voltage of capacitor  $C_{1b}$  (BIBRED converter)

$V_{\text{out}}$ ,  $V_{\text{o}}$  Output voltage

$\phi_1$  Phase difference between the line frequency voltage and current

$\omega_{\text{line}}$  Angular frequency of the line voltage,  $2\pi f_{\text{line}}$

$\Delta t$ ,  $\Delta t_1$  Time delay required for turn at  $V_{\rm in}$  level in the FAC converter

$\Delta t_2$  Time delay required for ZVS in the FAC converter

<sup>\*</sup> Markings differ in publication P[2].

## 1 Introduction

The number of switched mode power supplies (SMPSs) and other power electronic appliances is growing. SMPSs are needed to convert electrical energy from one form to another. Since electrical sources can be either dc or ac, there are four basic types of converters; namely, conversion can be from ac to ac, dc to ac, ac to dc, and dc to dc. We will consider in this Thesis the two latter directions of conversion of electrical energy. For this reason, the Thesis is roughly divided into two parts. The first part deals with power factor correction converters, i.e. ac to dc conversion, and the second part deals with dc to dc conversion. It should be noted, also, that only relatively low power equipment fed from a dc or a single-phase ac source are considered in the Thesis.

The Thesis is composed of an introductory part and eight publications: P[1], P[2], P[3], P[4], P[5], P[6], P[7] and P[8], which have been presented in international conferences. The introductory part gives background information on the power factor correction and dc-dc conversion with forward converter.

#### 1.1 Ac-dc conversion

Ac to dc rectifiers usually interface with the mains. These devices convert the sinusoidal line voltage to a dc voltage. It is a well-known fact that the input current of a SMPS tends to have a non-sinusoidal, distorted waveform. The distorted line current of a power converter is composed of the line frequency component and higher frequency harmonic components of the current. It should be noted that only the line frequency component of the current is carrying power when voltage is sinusoidal.

As use of energy is growing, the requirements for the quality of the supplied electrical energy are becoming stricter. This means that power electronic converters are used, or have to be used, to convert the input voltage to a precisely regulated dc voltage for the load.

Since the number of electronic appliances that are fed by power converters is soaring, an increasing amount of non-sinusoidal current is drawn from the distribution network. Consequently, due to the increasing amount of harmonic currents drawn, the distribution network becomes more and more polluted. As a direct consequence, available power from the grid becomes less. This is because unnecessary current components, which contribute to the rms value of the line current, are drawn from the grid. On the other hand, the harmonic currents distort the line voltage waveform and may cause malfunction in sensitive electrical equipment connected to the grid, Redl et al. 1995b, Redl 1996 and Redl et al. 1997.

Standard IEC 61000-3-2 (IEC 1995, IEC 2000 and IEC 2001) and its European version EN 61000-3-2, set limits for the allowed harmonic content of the line current of a power supply. Because of the standards and because of the problems related to the distorted line current, power supply manufacturers most probably have to equip their products with power factor correction (PFC) circuits. The main task for a PFC circuit is to shape the input current to resemble the waveform of the sinusoidal line voltage, i.e. to reduce the harmonic content of the line current of a power converter.

An additional PFC circuit in front of a power supply, however, adds to the cost and size of the device. This cost depends naturally on the chosen topology and the complexity of the circuit. Tolerance for any additional cost, however, in low power supply manufacturing is relatively low, owing to the fact that low power SMPSs tend to be mass production devices and sold in an extremely competitive market, Redl et al. 1995b. For this reason, there may well be a niche for low-cost power factor correction converters in which for example the component count is minimized.

As mentioned earlier, the standard and the harmful effects of the line current harmonics, Redl et al. 1995b, Redl 1996 and Redl et al. 1997, bring about a growing need for PFC converters. Single-stage converters combine the two desired objectives, line current shaping and output voltage regulation, into a single power processing stage. This means that power is processed only by one active switching stage, albeit that two separate goals are to be met. Therefore, at least one switch and the control circuitry for it are saved with this arrangement compared to two-stage PFC converters in which two separate converters are cascaded, Zhang et al. 1999. Single-stage

converters offer thus a reduction in the component count and they can be considered as a low-cost alternative for PFC.

In this Thesis three single-stage power factor correction circuits are investigated: the dither converter with a tapped transformer, the BIFRED converter and the BIBRED converter. It should be mentioned, however, that power factor correction properties of these three converters are not investigated in detail in this Thesis. This is because it is assumed, based on earlier research, that these converters can be designed to achieve a line current that satisfies the requirements set by the standard. Instead, the research reported here is concentrated on giving more insight into the operation and design of the converters or on improving the performance of the converters.

For the dither converter we have performed a steady state and small signal analyses. For the BIFRED and BIBRED converters a resonant type non-dissipative snubber is analyzed in detail. Additionally, we have developed and analyzed a passive clamp circuit for the BIFRED converter.

These three power factor correction converters are presented in Chapter 3 and in publications P[1], P[2], P[3] and P[4].

#### 1.2 Dc-dc conversion

Switched mode supplies are widely used in dc-dc conversion. Input voltage for these converters is, as the name indicates, a dc voltage source. The input dc voltage source for a dc-dc converter can be, for example, rectified line voltage, output voltage of a PFC circuit, battery or fuel cell voltage.

A relatively high switching frequency that is used in these power converters enables the use of small reactive components, which reduces the overall size of the power supply. Also, a high switching frequency and small reactive components improve the converter's dynamic behavior, i.e. it is able to cope rapidly to changes in the load and input voltage.

One additional advantage of switched mode power supplies is a relatively high efficiency. Ideally, the energy conversion process would be without losses. However, in practice the components that are used to implement a converter are non-ideal and these non-idealities cause losses in the energy conversion process. Therefore, the efficiency of the conversion process is less than 100 percent. However, although the

perfect efficiency seems to be unattainable, it is well worth striving to get as close as possible to that goal, i.e. to minimize losses.

Efficiency of a power supply is an important design factor. The small but inevitable amount of electric losses transforms to thermal energy, i.e. to heat, in the power supply. Heating due to these losses has to be taken into account in the design process and adequate cooling should be provided for the device. Cooling or heat removal from the power supply is needed in order to ensure that the temperature of the device, and its individual components, do not exceed their maximum allowable operating temperatures. Also, additional cooling may be needed in order to ensure that the components actually do operate somewhat below their maximum limits since operating in a relatively high temperature affects adversely to the expected life-time of a component, for example Stevens et al. 2002.

A small size for a power supply is desirable. As mentioned earlier, a small size is attainable by using a relatively high switching frequency. However, because of the conversion losses there should be a way to conduct the heat out of the device. This means that, for example, a heat sink should be attached to the heat-generating component or components of the converter in order to prevent overheating. This, naturally, increases the physical size of the power supply.

However, even a seemingly small improvement in the efficiency of the conversion process can lead to a somewhat noticeable reduction in the need for cooling. For example, if the efficiency of a power supply is increased from 90 % to 91 %, this means that in other words that the losses are cut by approximately 10 %.

A high efficiency in low voltage dc-dc conversion is a challenge. For example, state-of-the-art electronic devices require relatively low operating voltages, for example 3.3 V, 2.5 V, 1.8 V, 1.5 V, and even sub-1V output voltages can be expected in the future, Lidow et al. 2003. However, the load current for these low voltage outputs should be of several tens of amperes. The high load current can easily cause considerable voltage drops in the rectifying stage and in the power carrying leads of the printed circuit board (PCB). A considerable voltage drop means here that the voltage drop, which together with the current defines the loss of energy, is considerable in relation to the load voltage. This means that, if the load current flows

through a noteworthy voltage-drop somewhere else than in the actual load, the efficiency cannot be very good.

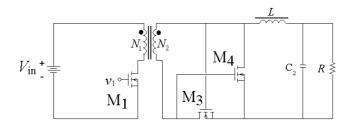

Rectification losses of a power converter can be reduced with synchronous rectifiers, Chryssis 1989. This means that rectifier diodes are replaced with MOSFETs. These MOSFET synchronous rectifiers need, however, synchronized control signals and some energy in order to be driven appropriately. A cost-effective arrangement is to use self-driven synchronous rectifiers in which the control signals for the rectifiers are taken from the windings of the converter's transformer or the output inductor.

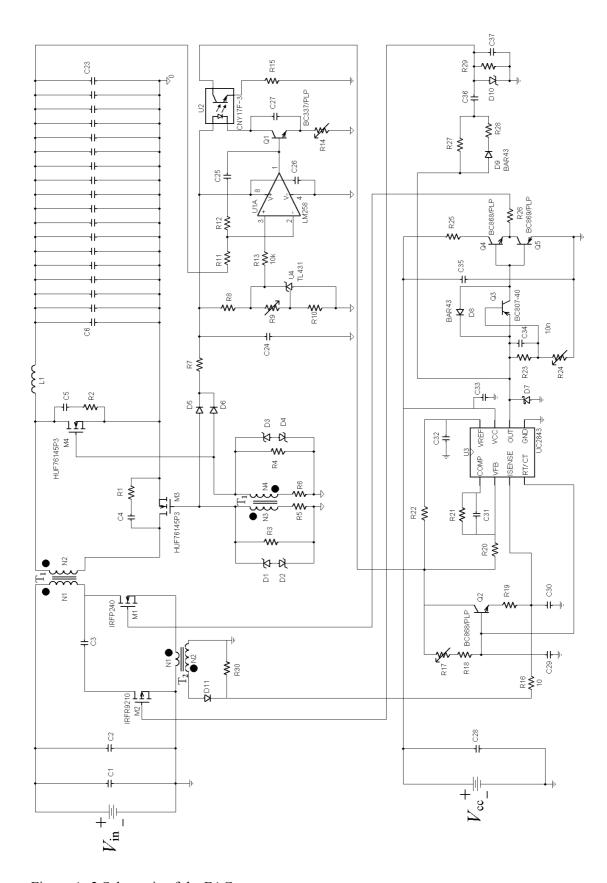

The single switch forward dc-dc converter is discussed in Chapter 4. Four passive and one active reset method for the transformer of the forward converter are presented and the suitability of the reset circuits for self-driven synchronous rectification are assessed. Further background information on forward converter with active clamp reset circuit and with self-driven synchronous rectifiers is given in the chapter. The research results on the active clamp forward converter are reported in publications P[5], P[6], P[7] and P[8].

The research reported in P[5], P[6], P[7] and P[8] is concentrated on giving more insight in to the operation of the active clamp converter and on techniques to improve the efficiency of the converter topology. The research results in the publications have been verified with a 3.4 V and 30 A prototype converter.

## 2 Background of power factor correction

#### 2.1 Standard IEC 61000-3-2

The introduction of the standard IEC 61000-3-2, IEC 1995, IEC 2000 and IEC 2001, set limits for the harmonic content of the line current of a power converter and prompted a need for power factor correction circuits. The IEC (International Electrotechnical Committee) standard has also been adopted by the European Committee for Electrotechnical Standardization (CENELEC) as standard EN 61000-3-2.

The standard divides electrical equipment into four classes: A, B, C and D. The four classes include electrical equipment as follows, IEC 2001:

Class A: Balanced three-phase equipment, household appliances (excluding equipment identified as class D), tools (excluding portable tools), dimmers for incandescent lamps and audio equipment.

Class B: portable tools and arc welding equipment which is not professional equipment.

Class C: lighting equipment.

Class D: personal computers and personal computer monitors, and television receivers (active input power equal or less than 600 W).

Additionally, class D limits are reserved, according to IEC 2001, to equipment that can be shown to have a pronounced effect on the public electricity supply system.

Limits for class A and class D equipment are shown in Table 2.1 and 2.2, respectively. Class A limits are in absolute values whereas the class D limits are given in power related terms. Therefore, for a low power converter, class D limits seem to be stricter. Also, class D applies to equipment with input power  $P_{in} \le 600$  W that can be shown to have a pronounced effect on the public supply system.

Table 2.1. Harmonic limits for class A devices, IEC 2000.

| Harmonic order    | Maximum permissible |  |  |  |  |

|-------------------|---------------------|--|--|--|--|

|                   | harmonic current    |  |  |  |  |

| n                 | A                   |  |  |  |  |

| Odd harmonics     |                     |  |  |  |  |

| 3                 | 2.30                |  |  |  |  |

| 5                 | 1.14                |  |  |  |  |

| 7                 | 0.77                |  |  |  |  |

| 9                 | 0.40                |  |  |  |  |

| 11                | 0.33                |  |  |  |  |

| 13                | 0.21                |  |  |  |  |

| $15 \le n \le 39$ | $0.15\frac{15}{n}$  |  |  |  |  |

| Even harmonics    |                     |  |  |  |  |

| 2                 | 1.08                |  |  |  |  |

| 4                 | 0.43                |  |  |  |  |

| 6                 | 0.30                |  |  |  |  |

| 8 ≤ <i>n</i> ≤ 40 | $0.23\frac{8}{n}$   |  |  |  |  |

Table 2.2. Limits for class D equipment, IEC 2000.

| Harmonic order  n                 | Maximum permissible harmonic current per watt mA/W | Maximum permissible harmonic current A |  |  |

|-----------------------------------|----------------------------------------------------|----------------------------------------|--|--|

| 3                                 | 3.4                                                | 2.30                                   |  |  |

| 5                                 | 1.9                                                | 1.14                                   |  |  |

| 7                                 | 1.0                                                | 0.77                                   |  |  |

| 9                                 | 0.5                                                | 0.40                                   |  |  |

| 11                                | 0.35                                               | 0.33                                   |  |  |

| $13 \le n \le 39$ (odd harmonics) | $\frac{3.85}{n}$                                   | See Table 2.1                          |  |  |

#### 2.2 Line harmonics in switched mode power supplies

Switched mode power supplies are notorious for having a distorted input current, which is rich in harmonic currents. A high harmonic content of the input current of a power converter reduces the available power, which can be drawn from the utility grid. The harmonic components of the current also pollute the utility grid, Redl et al. 1995b, which can cause malfunction in sensitive electrical equipment connected to the same grid.

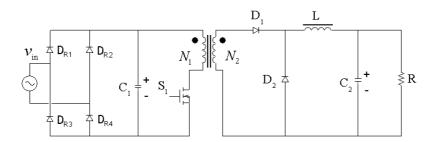

A typical non-power factor corrected front-end power converter is depicted in Fig. 2.1.

The input side of the converter in Fig. 2.1 presents a combination of a large energy storage capacitor and a diode bridge. The diode bridge is composed of the four rectifier diodes,  $D_{R1}$ ,  $D_{R2}$ ,  $D_{R3}$  and  $D_{R4}$ , and it is the power supplies' interface to the mains.

Capacitor voltage  $v_C$  of capacitor  $C_1$  is the input voltage for the high frequency dc-dc conversion stage of the converter. This stage consists of the transformer, switch and the whole secondary side of the circuit. The bulk capacitor,  $C_1$ , should be able store enough energy to cover a momentary blackout of the power grid, Mohan et al. 1995 page 347, and it should also be able to balance the fluctuation of input power at twice the line frequency. Therefore, the bulk capacitor,  $C_1$ , usually has a relatively high capacitance.

The combination of a large capacitor and the diode bridge is the cause for the distortion in the line current. This is because the diodes in the bridge are able to conduct and deliver energy from the mains to the circuit only when the rectified sinusoidal line voltage,  $|v_{\rm in}|$ , has a greater value than capacitor voltage  $v_{\rm C}$ . Since  $C_1$

Figure 2.1. A forward type SMPS used as a front-end converter.

has a relatively high capacitance, the voltage of it does not drop considerably during two consecutive peaks of the line voltage, i.e. during a half line cycle. The time interval during which the rectified sinusoidal line voltage has a higher value than the capacitor voltage is, therefore, rather short.

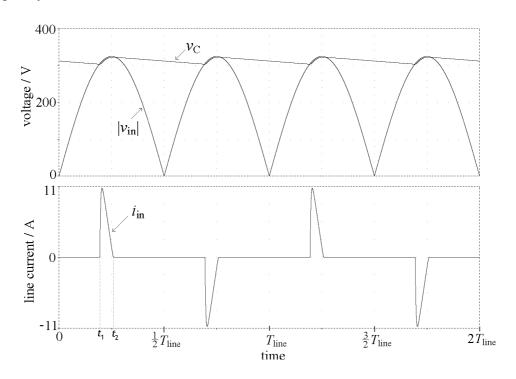

Simulated waveforms of line current  $i_{\rm in}$ , capacitor voltage  $v_{\rm C}$  and rectified line voltage  $|v_{\rm in}|$  in the case of a non-power factor corrected converter is shown in Fig. 2.2. Simulation parameters were:  $V_{\rm in,rms} = 230 \, \text{V}$ ,  $C_1 = 330 \, \mu\text{F}$  and the load was modeled as a 235 W constant power load.

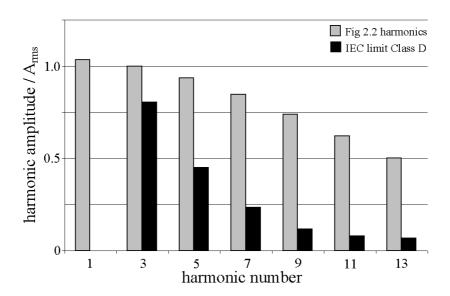

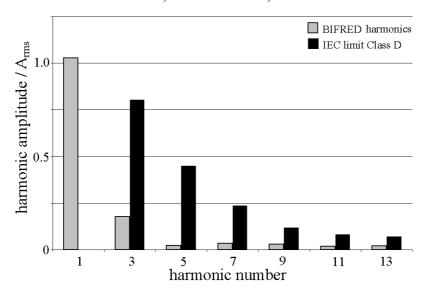

The simulation result clearly shows that the current has a non-sinusoidal, distorted waveform. Rms values of the line frequency component and the six first odd harmonics of the line current, depicted in Fig. 2.2, are shown along with class D limits of standard IEC 61000-3-2 in the bar chart of Fig. 2.3. It is obvious that the device does not meet the limits set by the standard.

The harmonic components of the line current are at frequencies that are odd multiples of the line frequency. The harmonics are denoted as  $I_{\text{in,rms},n}$  where the letter n marks the frequency of the harmonic, which is the n:th multiple of the line frequency.

Figure 2.2. Rectified sinusoidal line voltage and the bulk capacitor voltage in the upper part and resulting line current in the lower part of the picture.

Figure 2.3. Line frequency component and the six first odd harmonics of the line current depicted in Fig. 2.2. Class D limits of standard IEC 61000-3-2 are also shown.

### 2.3 Basic definitions in power factor correction

The distorted line current, depicted in Fig. 2.2, has a relatively rich content of harmonics. The current is also said to have a high crest factor, Mohan et al. 1995, a quantity that describes the ratio of the peak value of the current to the total rms value of the current.

Crest factor =

$$\frac{I_{\text{in,peak}}}{I_{\text{in,rms}}}$$

(2.1)

The rich content of harmonics leads to a poor power factor (PF). Quantity PF is used to measure the ratio of power P to apparent power S drawn from the utility grid. PF is defined as follows, Mohan et al. 1995.

$$PF = \frac{P}{S} = \frac{V_{\text{in,rms,1}} I_{\text{in,rms,1}}}{V_{\text{in,rms}} I_{\text{in,rms}}} \cos \phi_1 \approx \frac{I_{\text{in,rms,1}}}{I_{\text{in,rms}}} \cos \phi_1$$

(2.2)

In Eq. (2.2)  $V_{\rm in,rms}$  and  $V_{\rm in,rms,1}$  are the rms values of the line voltage and line frequency component of the line voltage, respectively, and  $I_{\rm in,rms}$  and  $I_{\rm in,rms,1}$  are defined correspondingly. Parameter  $\phi_1$  depicts the difference in phase between the fundamental components of the line voltage and line current, that is between  $v_{\rm in,1}$  and  $i_{\rm in,1}$ . It is assumed in Eq. (2.2) that the line voltage is not distorted.

The cosine of the phase difference  $\phi_1$  is called displacement power factor *DPF*, Mohan et al. 1995.

$$DPF = \cos\phi \tag{2.3}$$

In power supply applications, the displacement  $\phi_1$  between the line frequency components is usually close to zero. Quantity PF can hence be approximated with good accuracy in power supply applications by the ratio of the two currents in Eq.(2.2). Therefore, a good PF is achieved if the harmonic content is reduced in relation to the line frequency component of the line current.

Total harmonic distortion (*THD*) measures the ratio of the total rms value of the harmonic currents to the rms value of the line frequency component, Mohan et al. 1995.

$$THD = \frac{\sqrt{\sum_{n=2}^{\infty} I_{\text{in,rms},n}^2}}{I_{\text{in,rms},1}} \qquad n = 3, 5, 7...$$

(2.4)

If the line voltage is not distorted, *PF* and *THD* share the following relationship, Mohan et al. 1995.

$$PF = \frac{1}{\sqrt{(1+THD^2)}}DPF \tag{2.5}$$

## 3 Single-stage power factor correction circuits

#### 3.1 General

The family of single-stage converters is an interesting alternative to low-cost power factor correction. A variety of suitable topologies of single-stage converters can be found from literature, for example: Cha et al. 1998, Garcia et al. 1999, Garcia et al. 2000, Jin et al. 2001, Lee et al. 1996, Lee et al. 1997, Madigan et al. 1992, Oba et al. 1998, Redl et al. 1994, Brkovic et al. 1992 and Takahashi et al. 1991.

Properties of and design considerations for a number of single-stage converters have been reported in literature, for example: Jovanović 1994, Newton 2000, Simonetti 1992 and Redl 1995a.

The distinctive property of a single-stage converter is that it has only one active switching element. The active element is used, on one side, to regulate the isolated output voltage as in a normal power supply. The other task for the active element is to shape the line current to resemble as closely as possible the sinusoidal line voltage waveform. There are, hence, two tasks for the one switching element. This means that the other goal has to be reached more or less inherently.

Single-stage converters, in most cases, utilize the fact that the envelope of a discontinuous conduction mode (DCM) inductor current automatically follows the feeding voltage waveform, Liu et al. 1989, Lazar et al. 1995 and Wang et al. 1996. There are also reports of discontinuous capacitor voltage mode PFC circuits, Grigore et al. 1999a, Grigore et al. 1999b and Grigore 2001.

Line current shaping in single-stage converters can, therefore, be dealt with by allowing the input side reactive element to operate in the DCM. The one degree of freedom, duty ratio of the active switch in constant frequency applications, is used to regulate the output voltage. We will assume in the following analyses of the three single-stage converters that they operate, in steady state, with constant duty ratio  $D_1$ .

We do not go into detail of the power factor correction properties of the singlestage converters presented in this Thesis. Instead, we assume that a fairly good line current, that satisfies the requirements of the standard, is reachable with these three single-stage converters.

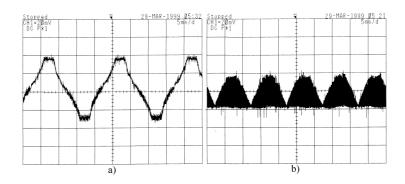

As an example of the PFC properties of a single-stage converter, the line current of a constant duty ratio BIFRED converter, with input power  $P_{\rm in} \approx 235$  W, is shown in Fig. 3.1 a). It can be seen from the figure that the current resembles closely the desired sinusoidal waveform. The fundamental component and the first six harmonics of the current, shown in Fig. 3.1 a), are shown along with class D limits of standard IEC 61000-3-2 in Fig. 3.2, Tuomainen 1999. It is easy to see that the converter fulfills the requirements set by the standard. Fig. 3.1 b) shows the current of the BIFRED's DCM boost inductor.

Figure 3.1. Line current in a) and boost inductor current in b) of constant duty ratio BIFRED converter, Tuomainen 1999. Scale in a) 1 A/div and in b) 2 A/div.

Figure 3.2. Line frequency component and six first harmonics of the line current in Fig. 3.1. a), Tuomainen 1999.

#### 3.2 Dither converter

#### 3.2.1 General

The dither converter, Oba et al. 1998, is an interesting candidate for a single-stage power factor correction converter. A schematic of the converter is shown in Fig. 3.3. The converter is a buck-boost type single-stage converter in which the power factor correction is dealt with by allowing inductor  $L_1$  to operate in the DCM.

The converter can be designed so that the forward part of the converter operates in the continuous conduction mode (CCM). This is due to the fact that capacitor  $C_1$  is not charged directly from the mains and, therefore, the steady state voltage of the capacitor can be considerably lower than the peak of the line voltage.

Usually, in single-stage converters in which the isolation part of the converter operates in the CCM the bulk capacitor voltage has a strong dependence on the load.

That means that the voltage may reach a relatively high level at light loads, which means that the energy storage capacitor has to sustain the voltage stress. Naturally, a high initial voltage on the capacitor aggravates the situation.

The capacitor voltage in the dither converter is, also, dependent on the load but since the voltage can have low steady state values at high loads, there is room for it to rise as a consequence of load reductions. This situation is difficult to achieve, for example, in the BIFRED and BIBRED single-stage converters, in which the minimum primary side energy storage capacitor voltage has to be greater than the peak line voltage. This will be discussed later in Section 3.3.

As mentioned above, the dither converter can be designed to operate in the DCM – CCM operation mode. This allows for smaller current ripple as well as smaller high

Figure 3.3. Dither converter with a tapped transformer, Oba et al. 1998.

frequency flux swinging in the output inductor. This eventually reduces conduction losses in the transformer and in the secondary side and core losses in the inductor. Also, a current with lower ripple reduces the need for filtering capacity.

The research reported in this Thesis, concerning the dither converter with a tapped transformer, is concentrated on finding a steady state representation and a small signal model for the converter. In the following two sections the principles and derivation of the steady state and small signal models of the dither converter, are presented respectively.

#### 3.2.2 Steady state analysis

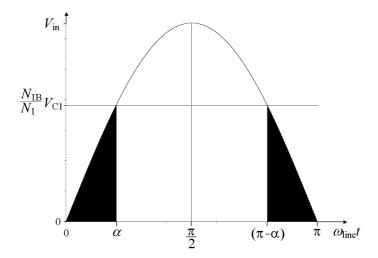

The tapping in the transformer of the converter disables the diode bridge at low instantaneous line voltage values. This introduces zero crossing distortion to the line current. The diode bridge is able to conduct, and power flow to the circuit is enabled, when the instantaneous line voltage is above the following limit:

$$\left| v_{\rm in} \right| > \frac{N_{\rm 1B}}{N_{\rm 1}} V_{\rm C1} = \frac{N_{\rm 1B}}{N_{\rm 1A} + N_{\rm 1B}} V_{\rm C1}$$

(3.1)

Line voltage, during a half line cycle, is illustrated in Fig. 3.4. Angles  $\alpha$  and  $(\pi - \alpha)$ , which denote the points at which the line voltage crosses the level that enables/disables diode bridge are also drawn in the figure. The sine of angle  $\alpha$  can be defined as follows:

Figure 3.4. Line voltage during a half line cycle. Black areas indicate the portions of a half line cycle during which the diode bridge is not able to conduct.

$$\sin(\alpha) = \frac{N_{1B}}{N_1} \frac{V_{C1}}{V_{in}} = \frac{N_{1B}}{N_2} \frac{V_{out}}{V_{in}} \frac{1}{D_1}$$

(3.2)

$D_1$  in Eq.(3.2) denotes the duty ratio of the switch.

Some principles of the steady state operation of the dither converter were reported in Oba et al. 1998, Tuomainen 1999 and Tuomainen et al. 1999. There was, however, no accurate and complete analysis available on this topic in the literature. Therefore, the steady state operation of this converter was investigated and the results of the analysis are reported in publication P[1].

The steady state analysis was made for an ideal converter, therefore the following assumptions were made: the switch, diodes and reactive components were treated as ideal components. Additionally, it was assumed that the capacitances of the two energy storage capacitors of the circuit,  $C_1$  and  $C_2$ , were large enough so that the voltage over them was considered a ripple free dc voltage and that the output inductor current  $i_{L2}$  was constant. It should be noted that despite these assumptions the simulations that were made with non-ideal semi-conductor component models and capacitor and inductor models with finite capacitances and inductance returned results that were very close to the computed results based on the analysis.

The idea behind the analysis was to average the operation of the converter over a switching cycle, i.e. to define the current that was taken from and brought to capacitor  $C_1$  during switching cycle  $T_s$ . The average current that is taken from the capacitor can be expressed as follows:

$$\left\langle i_{\text{C1,-}} \right\rangle_{T_s} = \left( \frac{N_2}{N_1} \right) I_0 D_1 \qquad 0 \le \omega_{\text{line}} t \le \alpha \qquad (3.3)$$

$$\left\langle i_{\text{C1,-}} \right\rangle_{T_{s}} = \left( \frac{N_{2}}{N_{1}} \right) I_{0} D_{1} - \frac{1}{2} \left( \frac{N_{1B}}{N_{1}} \right) I_{L1} D_{1}$$

$\alpha < \omega_{\text{line}} t \le \frac{\pi}{2}$  (3.4)

Similarly, the current that is brought to the capacitor during a switching cycle can formulated as follows:

$$\left\langle i_{\text{Cl},+} \right\rangle_T = 0$$

$0 \le \omega_{\text{line}} t \le \alpha$  (3.5)

$$\left\langle i_{\text{Cl},+} \right\rangle_{T_s} = \frac{1}{2} I_{\text{Ll}} D_2 \qquad \qquad \alpha < \omega_{\text{line}} t \le \frac{\pi}{2}$$

(3.6)

Both of the two currents have to be expressed in two parts. The reason for this is the disabled diode bridge at low instantaneous line voltage values.

It can be noted from Eqs. (3.3 - 3.6) that the average currents that charge and discharge the capacitor are not equal from switching cycle to switching cycle. Therefore, the steady state operating point had to be defined by averaging the operation of the converter over a line cycle.

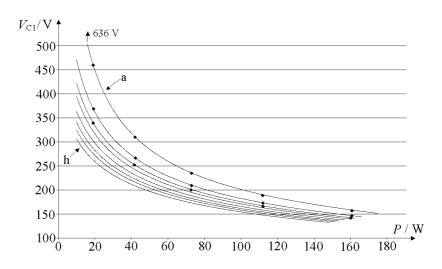

Calculated behavior of the bulk capacitor voltage of the dither converter is shown in Fig. 3.5. The capacitor voltage was determined as a function of load in eight different winding arrangements, which are listed in Table 3.1. Additionally, fifteen simulated points have been added to the figure. As can be seen from Fig. 3.5 the calculated and simulated results are in good agreement.

Details and results of the steady state analysis are presented in publication P[1].

| Model        | a    | b    | с    | d    | e    | f    | g    | h    |

|--------------|------|------|------|------|------|------|------|------|

| $N_2/N_1$    | 1.25 | 1.25 | 1.25 | 1.25 | 1.25 | 1.25 | 1.25 | 1.25 |

| $N_{1B}/N_1$ | 0    | 0.25 | 0.35 | 0.42 | 0.50 | 0.57 | 0.63 | 0.69 |

| $N_2/N_{1D}$ | -    | 5 00 | 3 57 | 3 00 | 2.50 | 2.19 | 2.00 | 1.80 |

Table 3.1. Turns ratios of the transformer used in the simulations.

Figure 3.5. Calculated behavior of the bulk capacitor voltage in eight cases. Fifteen simulated points have been added.

#### 3.2.3 Small signal analysis

Once the steady state operation of the converter had been investigated, the next step was to find a small signal description for the converter. The need for the dynamic model of the converter stemmed from the fact that there were no reports of the dynamic behavior of the converter available in literature.

The small signal analysis was made for an ideal converter model. The only parasitic element that was included in the analysis was the equivalent series resistance (ESR) of the output capacitor.

It should be noted, that the small signal model was analyzed only for the case when the line voltage is as in Eq. (3.1), i.e. the diode bridge is able to conduct. This decision was made since firstly, the converter operates most of the time in this operation mode and secondly, the small signal model of the converter at low instantaneous values of the line voltage resembles a normal forward converter fed by a large dc capacitor, which does not, however, receive any charge to compensate for the energy delivered to the load.

The chosen method for the small signal analysis was state space averaging, Cúk et al. 1977a. Due to the discontinuity of the input side inductor we had to use state space averaging for converters in discontinuous mode, Cúk et al. 1977b. State space averaging and derivation of a small signal model for single-stage converters with multiple discontinuous conduction modes are reported in Schenk et al. 1997 and Schenk et al. 1998.

We identified four reactive components in the circuit, magnetizing inductance of the transformer was omitted, and voltages of the two capacitors and currents of the two inductors were chosen as state variables.

$$\mathbf{x} = \begin{bmatrix} i_1 \\ i_2 \\ v_1 \\ v_2 \end{bmatrix}, \quad \dot{\mathbf{x}} = \frac{d}{dt} \mathbf{x}$$

(3.7)

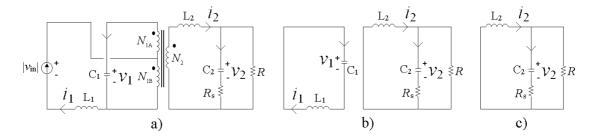

The matrices that describe the three states, depicted in Fig. 3.6, of the converter during a switching cycle can be written as follows:

$$\mathbf{A}_{1} = \begin{bmatrix} 0 & 0 & -\frac{N_{\rm B}}{L_{1}} & 0 \\ 0 & 0 & \frac{N}{L_{2}} & -\frac{r_{\rm p}}{L_{2}} \\ \frac{N_{\rm B}}{C_{1}} & -\frac{N}{C_{1}} & 0 & 0 \\ 0 & \frac{1}{C_{2}} & 0 & \frac{-1}{(R+R_{\rm s})C_{2}} \end{bmatrix}$$

$$(3.8)$$

$$\mathbf{A}_{2} = \begin{bmatrix} 0 & 0 & \frac{-1}{L_{1}} & 0 \\ 0 & 0 & 0 & -\frac{r_{p}}{L_{2}} \\ \frac{1}{C_{1}} & 0 & 0 & 0 \\ 0 & \frac{1}{C_{2}} & 0 & \frac{-1}{(R+R_{s})C_{2}} \end{bmatrix}$$

$$(3.9)$$

$$\mathbf{A}_{3} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & -\frac{r_{\rm p}}{L_{2}} \\ 0 & 0 & 0 & 0 \\ 0 & \frac{1}{C_{2}} & 0 & \frac{-1}{\left(R + R_{\rm s}\right)C_{2}} \end{bmatrix}$$

(3.10)

$$\mathbf{B}_{1} = \begin{bmatrix} (L_{1})^{-1} \\ 0 \\ 0 \\ 0 \end{bmatrix}, \mathbf{B}_{2} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}, \mathbf{B}_{3} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

(3.11)

The following markings were used in Eqs. (3.8 - 3.11) in order to simplify the representation:

$$\frac{N_{1B}}{N_1} = N_B, \quad \frac{N_2}{N_1} = N, \quad r_p = \frac{R}{R + R_s}$$

(3.12)

The relative lengths of the three different states during a switching cycle can be denoted as  $d_1$ ,  $d_2$ , and  $d_3$  and they are defined as follows:

$$d_{1} = D_{1} + d_{1}$$

$$d_{2} = D_{2} + d_{2}$$

$$d_{3} = D_{3} + d_{3}$$

$$d_{1} + d_{2} + d_{3} = 1$$

(3.13)

The small signal state space representation for the converter can be written as follows, Cúk et al. 1977b:

$$\hat{\mathbf{x}} = \mathbf{A} \hat{\mathbf{x}} + \mathbf{B} \hat{\mathbf{v}}_{in} + \hat{d}_1 \Big[ (\mathbf{A}_1 - \mathbf{A}_3) \mathbf{X} + (\mathbf{B}_1 - \mathbf{B}_3) V_{in} \Big] + \hat{d}_2 \Big[ (\mathbf{A}_2 - \mathbf{A}_3) \mathbf{X} + (\mathbf{B}_2 - \mathbf{B}_3) V_{in} \Big] (3.14)$$

in which matrices A and B are defined as:

$$\mathbf{A} = d_1 \mathbf{A}_1 + d_2 \mathbf{A}_2 + d_3 \mathbf{A}_3$$

$$\mathbf{B} = d_1 \mathbf{B}_1 + d_2 \mathbf{B}_2 + d_3 \mathbf{B}_3$$

(3.15)

The analysis resulted in control-to-output open-loop transfer function for the converter, which has the following form:

$$\frac{\dot{v_2}}{\dot{d_1}} = \frac{(Fs + G)}{(As^3 + Bs^2 + Cs + D)}$$

(3.16)

Coefficients for Eq. (3.16) are as follows:

$$\begin{split} A &= \frac{L_2 C_2 C_1}{N D_1} \\ B &= \frac{L_2 C_2}{N D_1} \left[ \frac{1}{\left(R + R_s\right)} \frac{C_1}{C_2} + \frac{I_1}{V_1} \left(N_B D_1 + D_2\right) + \frac{I_1}{\left(V_{\text{in}} - N_B V_1\right)} N_B \left(N_B D_1 + D_2\right) \right] \\ C &= \frac{1}{N D_1} \left[ C_1 r_p + \frac{I_1}{V_1} \frac{L_2}{\left(R + R_s\right)} \left(N_B D_1 + D_2\right) + \frac{I_1}{\left(V_{\text{in}} - N_B V_1\right)} \frac{L_2}{\left(R + R_s\right)} N_B \left(N_B D_1 + D_2\right) + C_2 \left(N D_1\right)^2 \right] \\ D &= \frac{1}{N D_1} \left[ \frac{I_1}{V_1} \left(N_B D_1 + D_2\right) r_p + \frac{I_1}{\left(V_{\text{in}} - N_B V_1\right)} r_p N_B \left(N_B D_1 + D_2\right) + \frac{1}{\left(R + R_s\right)} \left(N D_1\right)^2 \right] \\ F &= C_1 V_1 \frac{1}{D_1} \\ G &= \left( \frac{V_{\text{in}}}{V_1} + 2 \frac{D_2}{D_1} + N_B \left(1 + D_1\right) + \frac{V_1}{\left(V_{\text{in}} - N_B V_1\right)} \frac{N_B \left(N_B D_1 + D_2\right)}{D_1} \right) I_1 - N I_2 \end{split}$$

(3.17)

Figure 3.6. Equivalent circuits of the dither converter during a switching cycle. Line voltage  $v_{in}$  is sufficiently high. a) switch on, b) switch off and c switch off and  $i_1 = 0$ .

Derivation of the small signal model for the dither converter is given in publication P[2].

### Simulation setup for determining the small signal transfer function

The small signal analysis was verified with simulations in a PSpice simulation environment. A converter model was built using near ideal components, i.e. the diodes and the switch had a voltage drop when conducting but not, for example, parasitic capacitances. Additionally, small resistances had to be added in series with the reactive components in order to run the simulations properly.

Due to the time-varying line voltage and due to the limited simulation time, a noise component at the target frequency was observed at the simulated output even without any disturbance in the control voltage. Therefore, for each simulated point shown in publication P[2] six separate simulations were carried out: one without control disturbance and five with a control disturbance with five different initial angles of  $\phi_C = 0^\circ$ ,  $45^\circ$ ,  $90^\circ$ ,  $135^\circ$  and  $180^\circ$ .

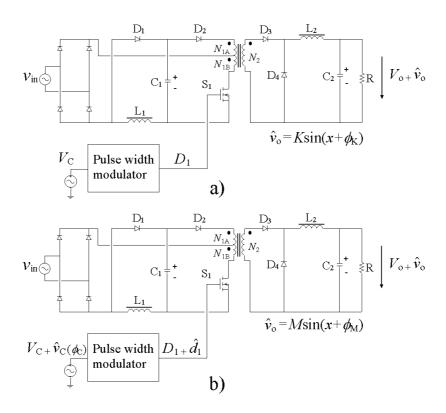

Simulation setup for the case without a control disturbance is depicted in Fig. 3.7 a). In this case, a constant control voltage  $V_{\rm C}$  was used to generate constant duty ratio  $D_{\rm 1}$ . Simulation setup for the case with a control disturbance is depicted in Fig. 3.7 b), in which a low-amplitude control disturbance was added on the top of the control voltage.

Generation of the duty ratio from the control voltage with the help of a sawtooth waveform is shown in Fig. 3.8.

Figure 3.7. a) Simulation setup without a control disturbance and b) setup with a control disturbance.

Figure 3.8. Sawtooth waveform, control voltage and the resulting duty ratio.

The control disturbance and the disturbance in the duty ratio share the following relation, Erickson et al. 2001 pp. 255.

$$D_1 + \hat{d}_1 = \frac{V_C + \hat{v_C}}{V_M} \tag{3.18}$$

Amplitude of the sawtooth waveform,  $V_{\rm M}$ , was in the simulated case  $V_{\rm M}=1{\rm V}$ , which means that the control disturbance and the disturbance in the duty ratio shared the same magnitude.

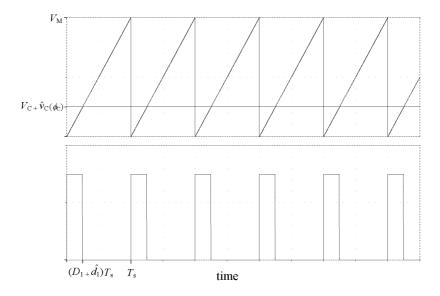

When the control disturbance was present, the observed, simulated output at the disturbance frequency was a sum of the noise observed without the disturbance and the component that was due to the disturbance for the control signal. The propagation of the control-to-output disturbance could then be extracted from the simulation data by finding a suitable angle and amplitude,  $\phi_L$  and L, for the control-to-output disturbance component.

$$M\sin(x+\phi_{\rm M}) = K\sin(x+\phi_{\rm K}) + L\sin(x+\phi_{\rm L}) \tag{3.19}$$

In Eq. (3.19) K and M are the amplitudes of the noise at the output without and with the control disturbance. Angles  $\phi_K$  and  $\phi_M$  are the corresponding phases for the two components observed at the output. The amplitude and angle for the disturbance at the output was obtained graphically, i.e. by matching two sinusoidal waveforms.

An example of the extraction of the control-to-output disturbance at frequency 1721 Hz is presented in Table 3.2. The first column of Table 3.2 gives the initial settings for the simulation, the second, third and fourth column gives the data obtained from the simulations. The fifth and sixth columns give the wanted data that was extracted by trial and error from the simulation data.

It should be noted that the control-to-output phase difference, which is given in the seventh column, is obtained by subtracting the extracted phase  $\phi_L$  (sixth column) from the phase of the simulated control disturbance (second column). The reason for this is that the fourier analysis of PSpice program, despite the initial settings (given in the first column), returned, in this simulation example, the initial phase for the control disturbance  $-66,61^{\circ}$  degrees shifted (second column).

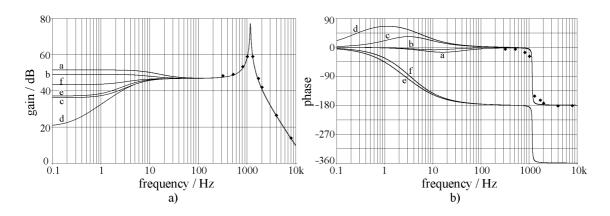

By using this method to determine the propagation of a small disturbance in the control signal to the output voltage we were able to verify the analysis. As can be seen from Fig. 3.9, the obtained simulation results correspond to the computed and expected behavior of the converter with good accuracy.

The computed gains and phases of the transfer function in Fig. 3.9 have been determined for six different instantaneous values of the line voltage, which are listed in Table 3.3.

Table 3.2. Simulation results for determining control-to-output gain and phase of the dither converter at frequency 1721 Hz.

| $\hat{v}_{\rm C}$ / mV                   | $\phi_{\mathrm{C,sim.}}$ | M/mV  | $\phi_{ m M}$ | $L = \stackrel{\circ}{v_2} / \text{mV}$ | $\phi_{ m L}$ | φ <sub>ν2</sub> * |

|------------------------------------------|--------------------------|-------|---------------|-----------------------------------------|---------------|-------------------|

| $0.5 \ (\phi_{\rm C} = 0^{\rm o})$       | -66,61°                  | 80,2  | 105,8         | 118                                     | -235          | -168,39           |

| $0.5(\phi_{\rm C} = 45^{\rm o})$         | -21,61°                  | 56,74 | 165,5         | 106,8                                   | -199          | -177,39           |

| $0.5 \ (\phi_{\rm C} = 90^{\rm o})$      | 23,39°                   | 98,13 | -113,6        | 110                                     | -140          | -163,39           |

| $0.5 \ (\phi_{\rm C} = 135^{\rm o})$     | 68,39°                   | 121,1 | -69,89        | 93,5                                    | -92           | -160,39           |

| $0.5 \ (\phi_{\rm C} = 180^{\rm o})$     | 113,4°                   | 170,5 | -34,11        | 121,5                                   | -38,5         | -151,9°           |

| Average of $L$ and $\phi_{v2}$ were used |                          |       | Avg.          | 110 mV ⇒ 46,8db                         | -             | -164,3 °          |

$<sup>\</sup>phi_{v2} = \phi_{L} - \phi_{C,sim}$

$$K = 50,23 \text{ mV}, \ \phi_{K} = -23,11^{\circ}$$

Figure 3.9. Computed gain and phase of the control-to-output transfer function,  $D_1 = 0.25$ . Nine simulated points have been added to the figure.

Table 3.3. Instantaneous line voltage values used in the calculations.

| Symbol                | a   | b   | c   | d   | e   | f  |

|-----------------------|-----|-----|-----|-----|-----|----|

| $V_{ m in}$ / ${f V}$ | 325 | 265 | 165 | 145 | 115 | 85 |

#### 3.3 BIFRED and BIBRED converters

#### 3.3.1 General

The BIFRED (Boost Integrated with Flyback Recitifier/Energy storage/Dc-dc converter) and BIBRED (Boost Integrated with Buck Rectifier/Energy storage /Dc-dc converter) are two single-stage converters, first presented by Madigan et al. 1992 and 1999. Both converters are capable of producing an input current with a low harmonic content and, also, a regulated and isolated output voltage. Line current shaping, i.e. power factor correction, and the output voltage regulation are attained in these two converters by using only one switch.

As mentioned in Section 3.2, the dither converter can be designed to operate in the DCM – CCM and that it is difficult to achieve the same situation with the BIFRED and BIBRED. For example, for European line voltage, the peak of the line voltage is  $V_{\rm in} \approx 325$  V, above which the bulk capacitor voltage of the BIFRED and BIBRED should be. Electrolytic capacitors for power electronic equipment, however, tend to have a limit for maximum voltage at around 450 - 500 V, Sarjeant et al. 2001 and Stevens et al. 2002. This voltage limit for the electrolytic capacitors is easily exceeded with European line voltage and with DCM – CCM BIFRED and BIBRED converters.

It is, therefore, reasonable to design the BIFRED and BIBRED converters to operate in the DCM – DCM mode, which means that the input inductor and the output inductive element both operate in the DCM mode. For this reason, we have assumed in our analyses that these two converters operate in the DCM – DCM operation mode.

It should be noted here, that the BIFRED converter bears a strong resemblance with the isolated version of the SEPIC converter. Also, the BIBRED converter resembles the isolated version of the Cúk converter.

Design considerations for the BIFRED converter were reported, for example, in Willers et al. 1994 and Willers et al. 1999. Small signal analysis of the SEPIC (BIFRED) converter was reported in Schenk et al. 1997.

Variable frequency control was researched for the BIBRED converter in Jovanović et al. 1994. Small signal dynamics of the isolated version of the Cúk converter (BIBRED) were reported in Vorperian 1996. Small signal considerations for

Cúk and SEPIC converters as power factor correction circuits were reported in Simonetti et al. 1992.

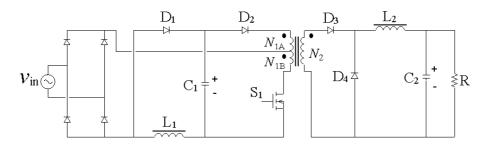

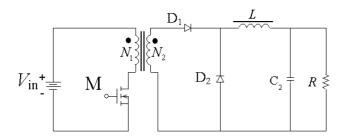

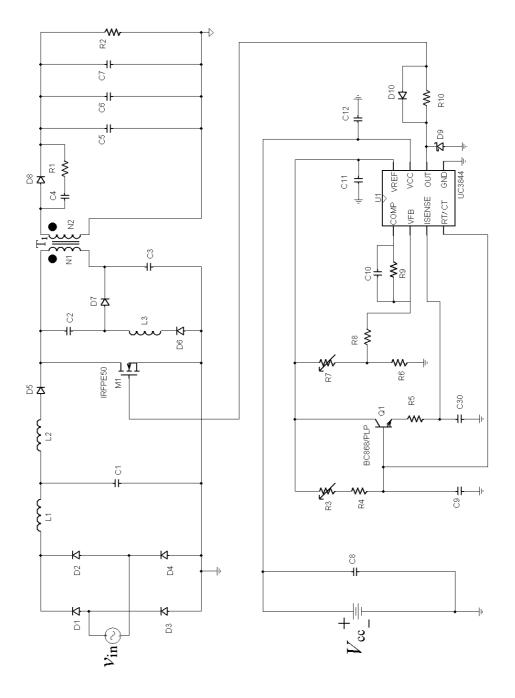

# 3.3.2 Research background

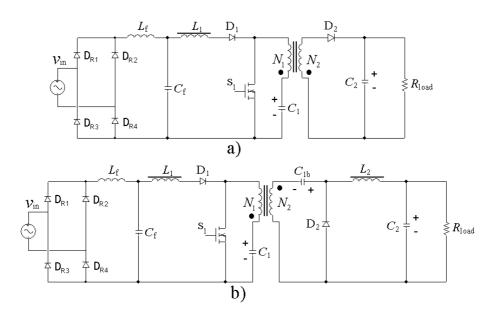

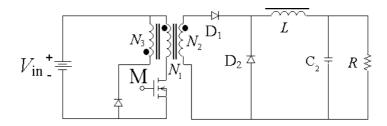

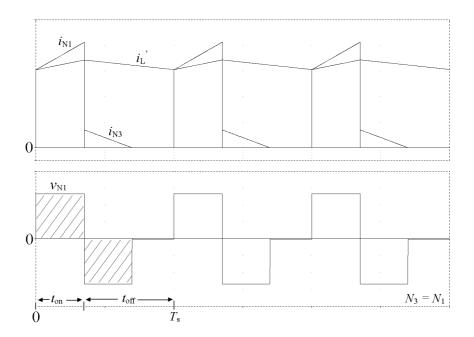

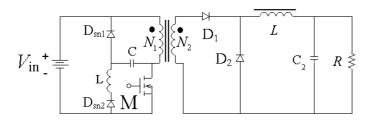

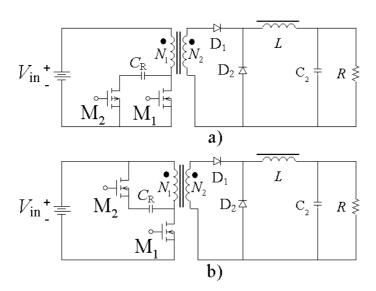

The BIFRED and BIBRED converters actually include two converters, which are integrated so that both of them utilize the same switch. The BIFRED converter is an integration of a discontinuous conduction mode (DCM) boost converter and a flyback converter. In the BIBRED, the corresponding parts are a DCM boost converter and a forward converter. Schematics of the BIFRED and BIBRED converters are shown in Fig. 3.10 a) and b), respectively.

The tight integration of the two sub-converters in these two single-stage converters causes some problems. One of them arises from the leakage inductance of the transformer, which has, in both converters, a pronounced effect on the voltage stress on the switch. Namely, the current in the leakage inductance has to be changed at turn-off instant of the switch from a positive peak value, i.e. the peak current of the transformer, to a negative peak value in a short period of time. The negative peak value means here the peak value of the DCM boost inductor current which is to be directed to flow through the primary winding of the transformer after the switch has been opened.

Figure 3.10. a) Schematic of the BIFRED converter and b) schematic of the BIBRED converter.

However, the boost inductor current cannot be immediately rerouted to flow through the winding due to the presence of the leakage inductance. Therefore, it is necessary to apply a voltage across the leakage inductance in order to achieve the desired change in the magnitude and flowing direction of the current. For that purpose a snubber circuit has to be employed, on one side, to provide the needed voltage and, on the other side, to provide an alternative path for the two inductive currents for the duration of the process of changing the direction of the current.

# 3.3.3 Resonant type snubber

A resonant type non-dissipative snubber was presented and analyzed for flyback converter in Shaughnessy 1980, Domb et al. 1982, Ninomiya et al. 1985 and Ninomiya et al. 1988, and for the forward converter in Tanaka et al. 1988. The references contain detailed analyses of the snubber for flyback and forward converters.

The same snubber circuit was proposed for BIFRED in Willers et al. 1999 and for BIBRED in Jovanović et al. 1994. The proposed snubber is, without doubt, a suitable circuit for the BIFRED and BIBRED topologies.

Previous studies, however, do not provide a detailed analysis of the circuit in these two single-stage converters, despite the fact that these two converters, due to the tight integration, pose a tougher challenge for the snubber than, for example, a flyback converter. Moreover, there are some differences in the operation of the snubber circuit in the BIFRED and BIBRED applications at turn-off instant of the switching device, which are due to the presence of the boost inductor and, therefore, two inductive currents.

The voltage produced by the snubber circuit is directly linked to the voltage stress on the switching device, and, consequently, the switch has to be selected so that it is able to withstand the expected voltage stress. However, a switch that can sustain high voltages tends to be more expensive or, at least, it tends to have a higher onresistance than a switch with a lower voltage rating. Therefore, a switch with a lower voltage rating saves in the costs or improves the efficiency of the converter, or both. It was, therefore, important to analyze the operation of the non-dissipative snubber in the two single-stage converters and to find out the expected maximum voltage stress as a function of the circuit parameters.

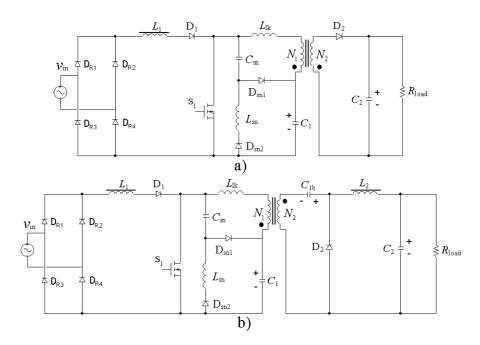

The BIFRED and BIBRED converters with resonant type non-dissipative snubber circuits are presented in Figs. 3.11 a) and b), respectively.

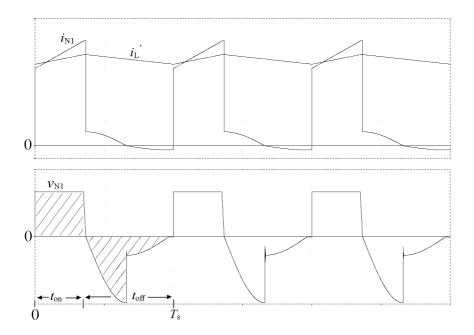

#### Turn-off transition in BIFRED converter

The snubber circuit protects the switch from voltage spikes and provides a path for the two inductive currents right after the switch has been turned off. During a period that we call here turn-off transition, a voltage is developed in the snubber capacitor, which allows for the current in the leakage inductance to change appropriately. The turn-off transition initiates from the turn-off of the switch and ends when the current in the leakage inductance has changed its direction and magnitude appropriately.

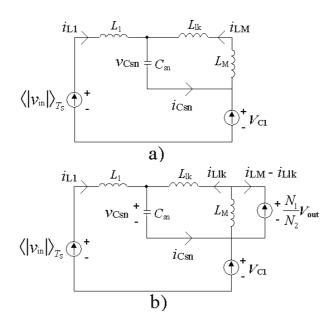

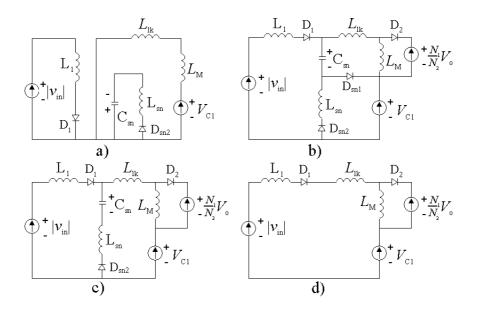

The turn-off transition is divided into two phases that we call here the first and the second phase. The first phase begins when the main switch is turned off and it ends when the snubber capacitor has been charged to a voltage level that allows for the secondary side diode,  $D_2$ , to become forward biased. The equivalent circuit of the BIFRED converter during the first phase is shown in Fig. 3.12 a).

The second phase of the turn-off transition begins, naturally, at the end of the first phase and it ends when snubber diode  $D_{sn1}$  becomes reverse biased. Equivalent circuit of the BIFRED converter during the second phase is shown in Fig. 3.12 b).

Figure 3.11. a) BIFRED and b) BIBRED with non-dissipative snubber circuit.

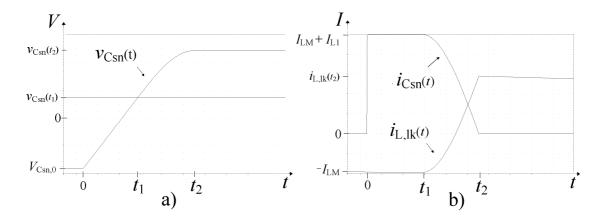

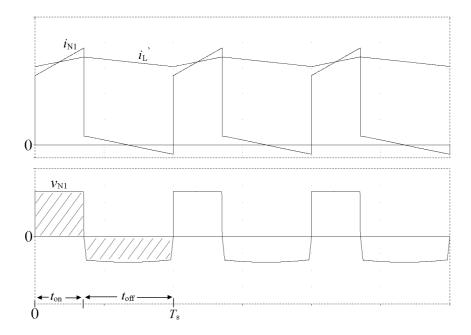

Simulated waveforms of the voltage and current of the snubber capacitor and current of the leakage inductance during the first phase  $(0 \le t \le t_1)$  and second phase  $(t_1 \le t \le t_2)$  of the turn-off transition are depicted in Figs. 3.13 a) and b).

It can be seen from the figure that the bulk of the needed change in the current of the leakage inductance,  $i_{L,lk}$ , takes place during the second phase. On the other hand, the snubber capacitor is being charged with a nearly constant current during the whole of the first phase.

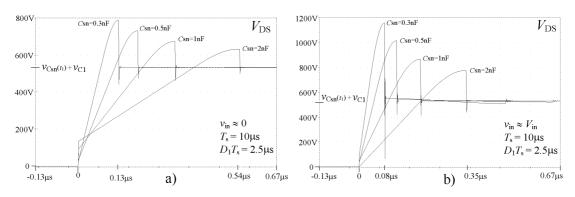

A simulated example of the voltage stress over the switch of the BIFRED converter is shown in Fig. 3.14. The figure shows the voltage stress in four different cases. Line voltage  $v_{in}$  in Fig 3.14 a) is approximately zero and in b) in the vicinity of the peak line voltage.

It can be seen from Fig. 3.14 that a rapid turn-off transition requires small capacitance  $C_{\rm sn}$ . A small capacitance, however, causes a relatively high voltage stress over the switch. On the other hand, a lower voltage stress is attainable with a larger  $C_{\rm sn}$ . This, however, lengthens the duration of the turn-off transition, which can become relatively long, especially at low line voltages.

A detailed analysis of the non-dissipative snubber for the BIFRED and BIBRED converters can be found from publication P[3].

Figure 3.12. a) Equivalent circuit of BIFRED: a) during the first phase, and b) during the second phase of the turn-off transition.

Figure 3.13. a) Simulated voltage of the snubber capacitor and b) simulated current of the snubber capacitor and the leakage inductance during the turn-off transition.

Figure 3.14. Simulated voltage over the switch of BIFRED at turn-off: a)  $v_{\rm in} \approx 0$  V and b)  $v_{\rm in} \approx 325$  V. Snubber capacitances:  $C_{\rm sn} = 0.3$  nF, 0.5 nF, 1 nF, and 2 nF.

## 3.3.4 Passive clamp circuit for BIFRED

As mentioned above, the BIFRED converter poses a tougher challenge for the snubber circuit than, for example, a flyback converter. This is due to the fact the direction of the current in the leakage inductance of the transformer has to be changed rather than to merely suppress it to zero after the switch has been turned off. For this reason, the voltage stress on the switching device may become unnecessarily high.

With the resonant type non-dissipative snubber, a switch with a relatively high voltage rating has to be used and this degrades the efficiency of the converter as explained above.

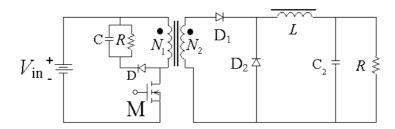

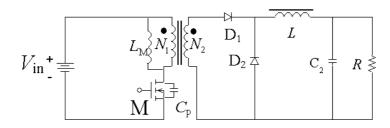

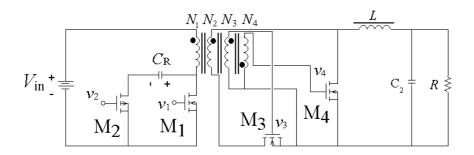

It might be, therefore, advantageous to clamp the voltage over the switch at turnoff to a known dc voltage rather than to charge the resonant snubber, from a negative initial voltage, to a high and somewhat unknown positive voltage at every turn-off. We developed and presented in publication P[4] a passive clamp circuit for the BIFRED converter. It should be mentioned, however, that the circuit could be used for the BIBRED converter as well.

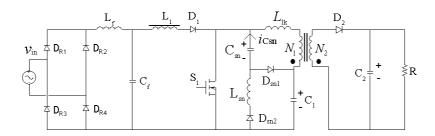

The BIFRED converter with the passive clamp circuit is presented in Fig. 3.15. The schematic of the passive clamp circuit is similar to that of the resonant snubber circuit.

The idea in the passive clamp solution is that the circuit is designed so that clamp capacitor  $C_{sn}$  retains a steady dc voltage. Therefore, the voltage over the switch becomes clamped at every turn-off to a voltage level defined by the sum of the voltages of capacitors  $C_{sn}$  and  $C_1$ .

Voltage of the clamp capacitor can be determined from charge balance. The current brought to the capacitor comprises the current that flows through the capacitor during the time the current changes direction in the leakage inductance right after the switch has been turned off. The current, and therefore, the charge that is taken from the capacitor during a switching cycle is determined by inductance  $L_{\rm sn}$ . Since the voltage over the clamp capacitor is a dc voltage, the current rises linearly in the clamp circuit inductor during the time the switch is conducting. Therefore, the size of the inductance determines the average current taken from the capacitor and the dc voltage in the capacitor. This is the opposite of the resonant type snubber in which the size of the snubber capacitance determines the voltage stress on the switch and the inductor is merely chosen to provide a high enough resonance frequency for the resonant circuit, publication P[3].

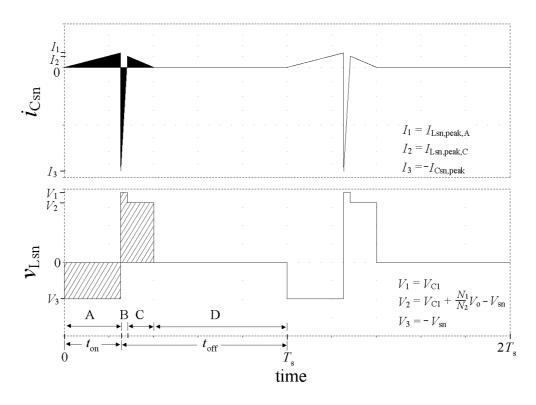

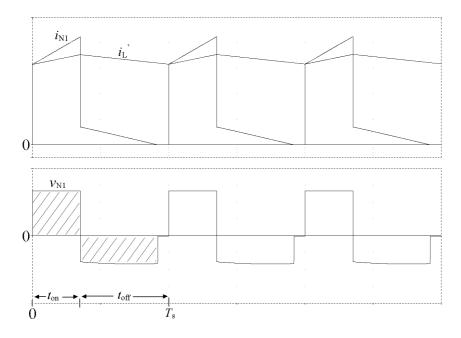

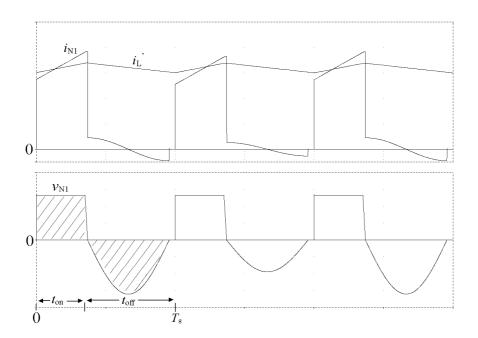

Simulated waveforms of current of the passive clamp capacitor and voltage across the passive clamp inductor during two successive switching cycles are depicted

Figure 3.15. BIFRED converter with a non-dissipative protective circuit for the switch. Leakage inductance of the transformer is shown as  $L_{lk}$ .

in Fig. 3.16. The positive direction of clamp capacitor current  $i_{Csn}$  is shown in Fig. 3.15.

Switching cycle  $T_s$  in Fig. 3.16 is divided into four intervals, A, B, C and D, and from which the passive clamp circuit is active during the three first intervals. Equivalent circuits of the converter for the four intervals are shown in Fig. 3.17.

In the derivation of the operation of the passive clamp circuit we assumed that voltage  $V_{C1}$  of capacitor  $C_1$ , output voltage  $V_0$  and clamp capacitor voltage  $V_{sn}$  are constants. We also assumed that the converter operates in the DCM – DCM operation mode with a constant duty ratio.

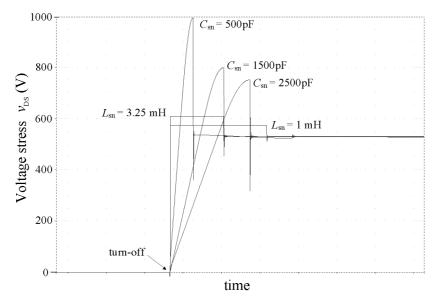

Voltage stress over the switch of the BIFRED converter at turn-off is shown in five different cases in Fig. 3.18. Three of the cases shown are simulated with resonant type snubber and the two other cases are attained with the passive clamp circuit.

Figure 3.16. Current and voltage of the passive clamp circuit.

Figure 3.17. Equivalent circuits of the BIFRED with the passive clamp. Intervals A, B, C and D are depicted in a), b), c) and d), respectively.

Figure 3.18. Simulated voltage stress over the switch at turn-off. Passive clamp:  $L_{\rm sn}=1$  mH and 3.25 mH and  $C_{\rm sn}=2.2$   $\mu F$ . Resonant snubber:  $C_{\rm sn}=500$ , 1500 and 2500 pF and  $L_{\rm sn}=50$   $\mu H$ .

It can be seen from the simulation result that in the case of the passive clamp circuit the voltage over the switch becomes clamped to a dc voltage immediately after the switch has been turned off. Additionally, the voltage remains constant throughout the turn-off transition.

The advantage of the passive clamp circuit becomes obvious if the simulation results of the passive clamp circuit are compared with the corresponding results from the resonant type snubber circuit. Clearly, the passive clamp circuit can be designed

so that the voltage stress over the switch is lower than in the case of the resonant type snubber and/or so that the turn-off transition is shorter than in the resonant type snubber. Additionally, it can be shown that the voltage stress is not dependent on the load in the case of the passive clamp circuit. On the contrary, the voltage stress is dependent on the load in the case of the resonant snubber.

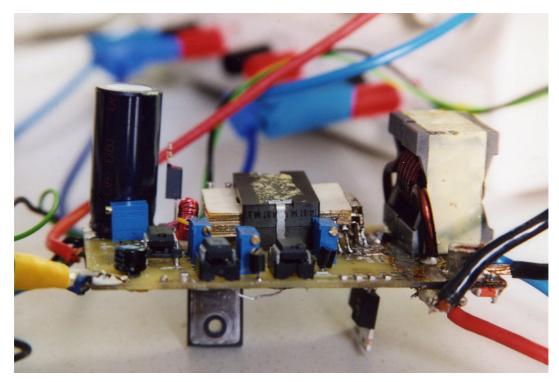

A prototype of the BIFRED converter was built to verify the analysis. Details of the prototype are given in publication P[4].

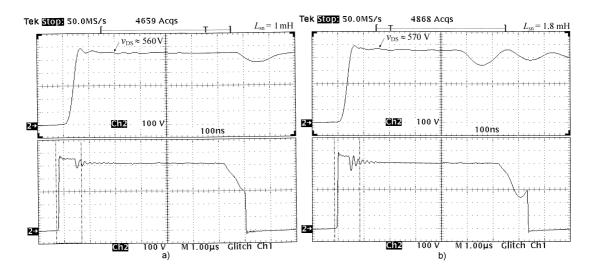

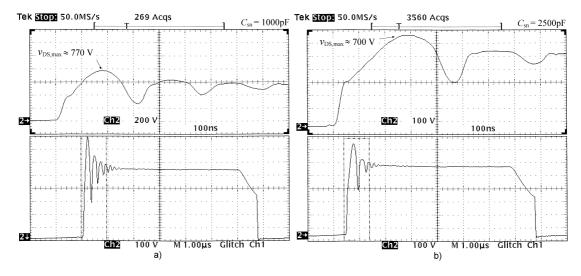

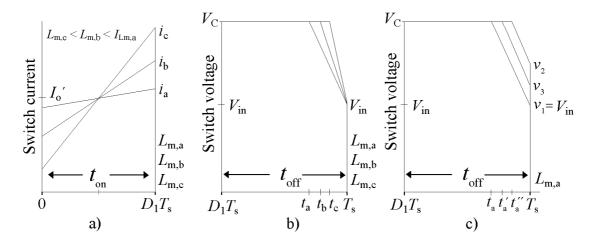

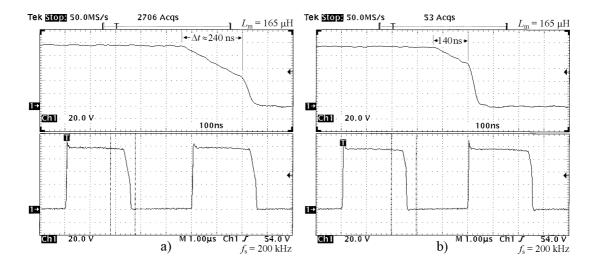

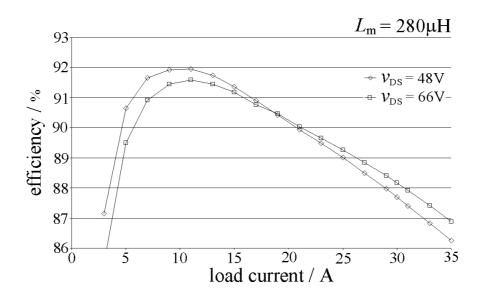

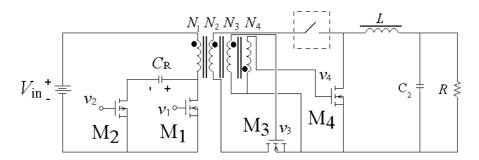

Measured waveforms of the voltage over the switch of the BIFRED prototype with the passive clamp circuit are shown in Fig. 3.19. In each figure the lower part shows the voltage during the off time of the switch,  $t_{\rm off}$ , and the upper part shows a detail from the lower part of the respective figure. It is easy to see that the circuit clamps the voltage over the switch, after turn-off, to a certain voltage level.