Helsinki University of Technology Laboratory for Theoretical Computer Science Research Reports 95 Teknillisen korkeakoulun tietojenkäsittelyteorian laboratorion tutkimusraportti 95 Espoo 2005 HUT-TCS-A95

# AUTOMATA-THEORETIC AND BOUNDED MODEL CHECKING FOR LINEAR TEMPORAL LOGIC

Timo Latvala

TEKNILLINEN KORKEAKOULU TEKNISKA HÖGSKOLAN HELSINKI UNIVERSITY OF TECHNOLOGY TECHNISCHE UNIVERSITÄT HELSINKI UNIVERSITE DE TECHNOLOGIE D'HELSINKI

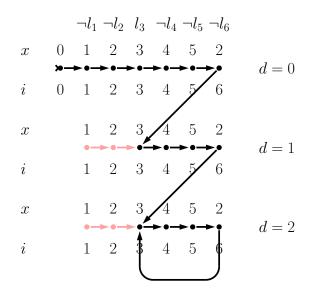

Helsinki University of Technology Laboratory for Theoretical Computer Science Research Reports 95 Teknillisen korkeakoulun tietojenkäsittelyteorian laboratorion tutkimusraportti 95 Espoo 2005 HUT-TCS-A95

# AUTOMATA-THEORETIC AND BOUNDED MODEL CHECKING FOR LINEAR TEMPORAL LOGIC

Timo Latvala

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Department of Computer Science and Engineering, for public examination and debate in Auditorium T2 at Helsinki University of Technology (Espoo, Finland) on the 12th of August, 2005, at 12 o'clock noon.

Helsinki University of Technology Department of Computer Science and Engineering Laboratory for Theoretical Computer Science

Teknillinen korkeakoulu Tietotekniikan osasto Tietojenkäsittelyteorian laboratorio Distribution: Helsinki University of Technology Laboratory for Theoretical Computer Science P.O.Box 5400 FI-02015 TKK Tel. +358-0-451 1 Fax. +358-0-451 3369 E-mail: lab@tcs.hut.fi

© Timo Latvala Original publications © Springer-Verlag, Publishing Association Nordic Journal of Computing

ISBN 951-22-7787-5 ISBN 951-22-7788-3 (PDF) ISSN 1457-7615

Multiprint Oy Helsinki 2005 **ABSTRACT:** In this work we study methods for model checking the temporal logic LTL. The focus is on the automata-theoretic approach to model checking and bounded model checking.

We begin by examining automata-theoretic methods to model check LTL safety properties. The model checking problem can be reduced to checking whether the language of a finite state automaton on finite words is empty. We describe an efficient algorithm for generating small finite state automata for so called non-pathological safety properties. The presented implementation is the first tool able to decide whether a formula is non-pathological. The experimental results show that treating safety properties can benefit model checking at very little cost. In addition, we find supporting evidence for the view that minimising the automaton representing the property does not always lead to a small product state space. A deterministic property automaton can result in a smaller product state space even though it might have a larger number states.

Next we investigate modular analysis. Modular analysis is a state space reduction method for modular Petri nets. The method can be used to construct a reduced state space called the synchronisation graph. We devise an on-the-fly automata-theoretic method for model checking the behaviour of a modular Petri net from the synchronisation graph. The solution is based on reducing the model checking problem to an instance of verification with testers. We analyse the tester verification problem and present an efficient on-the-fly algorithm, the first complete solution to tester verification problem, based on generalised nested depth-first search.

We have also studied propositional encodings for bounded model checking LTL. A new simple linear sized encoding is developed and experimentally evaluated. The implementation in the NuSMV2 model checker is competitive with previously presented encodings. We show how to generalise the LTL encoding to a more succint logic: LTL with past operators. The generalised encoding compares favourably with previous encodings for LTL with past operators. Links between bounded model checking and the automatatheoretic approach are also explored.

**KEYWORDS:** Verfication, Model checking, LTL, automata, safety properties, Petri nets, modular analysis, LTS, testers, bounded model checking, PLTL

# CONTENTS

| List of Publications |              |                                                            | vi            |

|----------------------|--------------|------------------------------------------------------------|---------------|

| 1                    | Intro<br>1.1 | o <b>duction</b><br>Contributions                          | <b>1</b><br>6 |

| 2                    | Mod          | lel Checking LTL                                           | 8             |

| 3                    | Auto         | omata-theoretic Methods                                    | 11            |

|                      | 3.1          | Model Checking Safety Properties                           | 12            |

|                      |              | 3.1.1 Safety Properties                                    | 13            |

|                      |              | 3.1.2 Algorithms                                           | 14            |

|                      | 3.2          | Model Checking Liveness Properties of Modular Petri Nets . | 18            |

|                      |              | 3.2.1 Petri Nets and Modular Nets                          | 19            |

|                      | 3.3          | On-the Fly Verification Using Testers                      | 21            |

|                      |              | 3.3.1 Labelled Transition Systems and Testers              | 22            |

|                      |              | 3.3.2 Algorithms                                           | 23            |

| 4                    | Bou          | nded Model Checking                                        | 28            |

|                      | 4.1          | A New Encoding for BMC                                     | 30            |

|                      | 4.2          | LTL with Past                                              | 33            |

| 5                    | Con          | clusions                                                   | 37            |

| -                    | 5.1          | Topics for Further Research                                | 37            |

| Bi                   | Bibliography |                                                            |               |

| A                    | Add          | itions and Corrections to Publications                     | 53            |

| Ar                   | Articles     |                                                            |               |

### PREFACE

This Thesis is the result of studies, research and a fair amount of coffee drinking at the Laboratory for Theoretical Computer Science of Helsinki University of Technology.

I am indebted to my supervisor Nisse Husberg for introducing me to the laboratory and for urging me on, especially in the beginning. Discussions with my instructor Keijo Heljanko – usually over coffee – have been excellent brainstorming sessions. His sharp insights and ability to explain complex problems have been invaluable. The head of the laboratory Ilkka Niemelä has not only contributed to the Thesis by securing funding to the laboratory. At least as important is the leadership and scientific integrity he has displayed running the laboratory. My sincerest thanks also go to my co-authors Marko Mäkelä, Heikki Tauriainen, Armin Biere, Tommi Junttila and Keijo Heljanko.

In addition to the the Laboratory for Theoretical Computer Science, this work has been funded by Helsinki Graduate School in Computer Science, National Technology Agency of Finland (TEKES), the Nokia Corporation, EKE Electronics, Genera, the Academy of Finland (projects 47754, 53695, 211025) and by personal grants from the Jenny and Antti Wihuri Foundation, Foundation of Technology (Tekniikan edistämissäätiö) and the Nokia Foundation. Their support is gratefully acknowledged.

My parents and my brother have always supported my aspirations and for this I am grateful. Without my love Emma everything would have been much more difficult.

Otaniemi, July 2005

Timo Latvala

#### LIST OF PUBLICATIONS

This dissertation consists of five publications and this dissertation summary. In publications [P1]–[P3] we employ the automata-theoretic approach to model checking LTL in different contexts, and in publications [P4]–[P5] we investigate efficient encodings for bounded model checking the temporal logic LTL and its generalisation PLTL.

- [P1] Timo Latvala. Efficient model checking of safety properties. In T. Ball and S. Rajamani, editors, *Model Checking Software*. 10th International SPIN Workshop, Portland, Oregon, USA, volume 2648 of Lecture Notes in Computer Science, pp. 74–88, Springer, 2003.

- [P2] Timo Latvala and Marko Mäkelä. LTL model checking for modular Petri nets. In J. Cortadella and W. Reisig, editors, Application and Theory of Petri Nets 2004. 25th International Conference, ICATPN 2004, Bologna, Italy, volume 3099 of Lecture Notes in Computer Science, pp. 298–311, Springer, 2004.

- [P3] Timo Latvala and Heikki Tauriainen. Improved on-the-fly verification with testers. Nordic Journal of Computing, 11(2):148–164, 2004

- [P4] Timo Latvala, Armin Biere, Keijo Heljanko, and Tommi Junttila. Simple bounded LTL model checking. In A. Hu and A. Martin, editors Formal Methods in Computer-Aided Design 2004, 5th International Conference FMCAD 2004, Austin, Texas, USA, volume 3312 of Lecture Notes in Computer Science, pp. 186–200, Springer, 2004.

- [P5] Timo Latvala, Armin Biere, Keijo Heljanko, and Tommi Junttila. Simple is Better: Efficient bounded model checking for past LTL. In R. Cousot, editor, Verification, Model Checking and Abstract Interpretation 2005, 6th International Conference VMCAI 2005, Paris, France, volume 3385 Lecture Notes in Computer Science, pp. 380–395, Springer, 2005.

The current author is the sole author of [**P1**] and has played a major role in all other publications.

Publication [P2] was co-authored by Marko Mäkelä. The key ideas and proofs were developed by the current author and the paper was to a large extent written by the current author. The implementation and the experiments were the co-author's work.

Publication [**P3**] was co-authored by Heikki Tauriainen. The original idea and initial versions of the algorithm were developed by the current author. The paper was jointly written, and the correctness proof for the algorithm and certain improvements to the algorithm were contributed by the co-author.

Publication [P4] was co-authored by Armin Biere, Keijo Heljanko and Tommi Junttila. The BMC encoding developed was to a large extent joint work with K. Heljanko, starting from initial versions by K. Heljanko. The current author had the main responsibility for writing the paper. The analysis of the original encoding in Section 2 was written by Armin Biere. The implementation and the experiments were contributed by the author. Publication [**P5**] was co-authored by Armin Biere, Keijo Heljanko, and Tommi Junttila. The BMC encoding developed was to a large extent joint work with K. Heljanko, starting from initial versions by the author. The current author had the main responsibility for writing the paper. Also the implementation and the experiments are work of the current author.

# **1** INTRODUCTION

We are moving towards a society where computers and software are increasingly managing business and safety critical functions. In effect, we are relying on our computers and software to function correctly more than ever. At the same time, the environment our systems are functioning in is becoming more challenging. There is complexity in the form of concurrency, heterogeneity, changing requirements and numerous other sources.

Of the above mentioned sources of complexity perhaps the most studied is concurrency. Concurrency can be an issue at many levels of a complex system. A modern telecommunication system must resolve concurrency issues between the participating devices of the network. At the same time, the mobile devices themselves are also concurrent systems: a mobile phone may be receiving a text message while the user is adding an item to the calendar. Another common feature of many complex systems is reactivity. A reactive system receives inputs from the environment and continuously reacts to the changing situation. Typical reactive systems include embedded controllers, mobile phones or computer operating systems.

Modelling reactive systems is challenging. A reactive system cannot be adequately described by the traditional model of behaviour where a system receives inputs and performs finite computations to produce output. Even small reactive and concurrent systems can be very complex to analyse: the combinatorial explosion of possible states in the system makes analysing the state space of the system hard. In addition, the inherent non-determinism in these systems contributes to the combinatorial explosion and complicates analysis in many ways. For systems implemented as hardware the sources of complexity are similar. The dominating factor causing state explosion is the large number of internal states combined with the non-determinism due to many free input variables in the system.

Despite the increasing complexity of systems there is an expectation of increased productivity. Thus, understanding and analysing concurrent and reactive systems is a challenging but necessary endeavour. Currently the most widely used verification and validation method is testing. However, the nondeterminism inherent in reactive and concurrent systems severely degrades the performance of methods such as testing. Repeating failing executions is very difficult in the presence of non-determinism, and this hinders effective regression testing and debugging. The large state spaces usually associated with concurrent systems and hardware systems also make achieving good coverage of the possible behaviours hard: even measuring coverage is difficult. The overall increase in the complexity of systems and the inadequacy of testing have been suggested as reasons for the faint signs that productivity in the software industry is actually decreasing [75].

An active research direction aiming at increasing the productivity of system designers is the research on *computer aided verification*. In this framework one analyses a mathematical *model* of the system and the environment w.r.t. a formal specification. The implicit assumption is that the mathematical model of the system reflects the important aspects of the real system. The analysis of the properties of the model is, however, only valid for the real system as far as the model reflects the properties of the real system. Computer analysis of the relationship between the system model and the specification, as well as various methods for obtaining the model and the specification can be seen as one definition of computer aided verification.

In 1977 Amir Pnueli [133] suggested that *temporal logic*, a variant of modal logic, could be suitable for specifying properties of reactive and concurrent systems. Pnueli argued that temporal logic provided a natural mathematical framework for reasoning about systems with non-terminating infinite behaviour. The specific variant of temporal logic Pnueli advocated modelled a system as a set of infinite sequences of states (executions). The notion of time in this model is discrete, and in an execution each time point has a unique future. The specification language Pnueli presented is called linear temporal logic (LTL).

Using temporal logic as a specification language for systems quite naturally leads to the idea of model checking. *Model checking* [31, 134, 36] is one of the most actively studied computer aided verification techniques. In model checking a temporal logic specification is checked against a *Kripke* model of the system. Kripke models of reactive systems capture the continuous interaction with the environment by modelling it with infinite computations. However, the interaction with the environment must be explicitly modelled since Kripke models do not have a notion of input or output w.r.t. the environment. The Kripke model represents the discrete state transition behaviour as a directed labelled graph. Computations of the system are infinite paths in the graph. Temporal logic is used to specify the allowed computations of the system. The computations allowed by the temporal logic specification can be mechanically compared with the computations of the Kripke model of the system. This process is called model checking.

Model checking has several attractive features. Once the Kripke model of the system and the temporal logic specifications have been defined (a nontrivial task in itself), the process is fully automatic. If a computation that violates the specification is found in the Kripke model, it can be displayed to the system designer to aid the debugging process [35, 119, 74]. In addition, the model checker can be designed to display a proof if the temporal logic property holds [128, 131, 113].

An alternative approach to model checking for proving temporal logic properties of a system is to use *deductive verification*. In deductive verification both the system and the properties are formalised as logical formulae. A theorem prover is used to show that the system has the desired properties. Deductive verification is often criticised for requiring highly educated experts to complete the proofs: the theorem provers are solving undecidable problems and in many cases need manual intervention to succeed. Model checking can, at least partly, be criticised on the same grounds. Although model checking is in principle automatic, manual abstraction is often required for a successful model checking effort. Deductive verification has been the method of choice for proving properties for some classes of systems such as general parametric systems. However, a recent result shows that model checking combined with finitary abstraction is as powerful as deductive verification [108]. Thus, because it is easier (in the current author's opinion) to find abstractions of systems than to find powerful invariants for automated proofs, model checking has greater potential than deductive verification.

Perhaps the greatest hurdle to ubiquitous industrial use of model checking is the *state explosion problem* (see [164] for a review). Even for simple models of concurrency, e.g. 1-safe Petri nets [48], analysing fundamental properties such as reachability of illegal states, is PSPACE-complete<sup>1</sup> (see e.g. [58]). Concurrent systems usually exhibit a combinatorial explosion in the number of global system states, because events in the system can occur in many possible ways as the participating processes are fairly independent. Research into alleviating the state explosion problem has been and remains one of the most active areas of study. Different approaches to alleviate the state explosion problem include symbolic model checking [24, 126, 14], partial order methods [162, 106, 70, 170], complete finite prefixes [125, 126, 84], compositional methods [38, 76, 121, 103], symmetry reduction [98, 78, 56, 140, 102] and abstraction [43, 34, 45, 71].

Although the state explosion problem is a great challenge, other issues also impede the industrial use of model checking. Constructing an accurate model of the system under inspection is a resource intensive task that can require the largest portion of the resources of a model checking effort [57, 138, 161]. For software systems obstacles faced when modelling a system include how to model advanced features of programming languages such as pointers, dynamic memory allocation and recursion. Another problem is ensuring the accuracy of the model when modelling a large system. Hardware systems mostly lack the complex features of software systems, but the large size of the systems makes isolating a manageable subsystem difficult. Many attempts at solving the modelling problem are based on automating the model construction phase in the model checking effort [91, 40, 9, 95].

Model checking requires that the specification is formulated in a temporal logic. Unfortunately, expressing the desired property accurately can be challenging even for a practitioner. False model checking results due to erroneous formulas are not unusual in model checking efforts [89, 91, 57]. Several approaches have been suggested to alleviate these problems: providing templates of useful formulas [50]; adding syntactic sugar to the logic and extending the language [10, 6]; providing a graphical front-end for LTL [152] and developing a domain specific front-end for the property language [41].

In some cases expressing the required properties is impossible because the logic which is used does not have the required expressive power. LTL and its simple extensions can only specify a proper subset of the  $\omega$ -regular properties called the star-free  $\omega$ -regular properties [159]. Lichtenstein et al. [120] have argued that full  $\omega$ -regularity is useful for facilitating compositional reasoning. Furthermore, there are interesting properties which are not even regular. For instance, expressing pre-condition, post-condition style properties for functions in formalisms where recursion is allowed is not a regular property [5]. Some research has been conducted in model checking non-regular specification formalisms. In [5] a method for model checking recursive state machines for a non-regular logic is developed, while [111] presents model checking of pushdown specifications for regular systems.

<sup>&</sup>lt;sup>1</sup>Here and in the following we use complexity classes as defined in [130].

The focus of this work has been to develop efficient model checking methods. The main techniques we have investigated are the automata-theoretic approach to model checking and bounded model checking. We have applied the automata-theoretic framework to different domains with special emphasis on the algorithmics for model checking LTL. In bounded model checking we have focused on developing efficient encodings of the LTL model checking problem into propositional logic.

The automata-theoretic approach to model checking [115, 168, 169, 166] presents automata as a uniform approach to specification and verification. The approach exploits the close connection between temporal logic and automata on infinite words. Any LTL property can be expressed by a so called *Büchi* automaton [168, 67]. In this approach automata are used to model both the system under inspection and the specification. Interesting questions, e.g. whether the behaviour of the system obeys the specification, can easily be cast into automata-theoretic terms. In many cases asymptotically optimal algorithms have been obtained using the automata-theoretic approach. Since automata are essentially labelled graphs, many of the key algorithms are actually adapted graph algorithms.

An important class of properties are the so called *safety properties*. Safety properties are properties of the system that have finite counterexamples or, more informally, properties requiring that "nothing bad happens". A safety property can e.g. express that "if the variable y becomes negative at some point, then the Boolean variable x will have been false before this occurs". As safety properties include properties such as invariants, they are usually considered the most important and critical subset of properties to verify in a system. Another reason safety properties are interesting is that algorithms for model checking safety properties are simpler and more efficient than algorithms for the general case. The automata-theoretic approach accommodates treating safety properties as a special case. Standard finite automata on finite words can detect counterexamples to LTL safety properties while so called Büchi automata are required by general LTL properties. The relevant algorithms for finite automata are simpler than the corresponding ones for Büchi automata. In some cases the difference can be so radical that model checking safety properties is decidable, while model checking general properties is not: LTL safety properties are decidable for (unbounded) Place/Transition nets, while general (state based) LTL properties are not [58]. Safety properties are also interesting outside the model checking context. In runtime analysis of programs [83] only safety properties can be monitored, since liveness properties can only be refuted by an infinite trace.

Many of the previously mentioned benefits can be obtained by having a compact deterministic finite automaton expressing the LTL safety property. We have investigated the problem of generating a finite automaton from an LTL safety specification in [**P1**].

An attractive feature of the automata-theoretic approach to model checking is its ability to flexibly adapt to different frameworks. A popular way to describe the behaviour of a distributed system is to use Petri nets [136]. In their most basic form, Petri nets do not include structural information such as the system's partition into processes. One extension of Petri nets that adds process structure to Petri nets is called modular Petri nets [26]. This additional structural information can be exploited by methods that attempt to alleviate the state explosion problem. *Modular analysis* is a method to generate a smaller state space for modular Petri nets such that the reduced state space still contains the relevant information for analysing the behaviour of the system. In publication [**P2**] we present an automata-theoretic LTL model checking method that is compatible with modular analysis.

The model checking method developed in [P2] reduces model checking modular Petri nets to a special case of *verification with testers* [163, 81]. Testers are a form of automata suitable for defining illegal behaviours of labelled transition systems (LTSs). LTSs model systems as finite sets of synchronising processes. Each process is modelled by a finite state automaton. Testers are LTSs with additional structural information to enable them to express both liveness and safety properties. The basic algorithmic problems related to verification with testers had not been characterised fully until [P3]. In [P3] we study the tester verification problem and present and prove correct an efficient algorithm for solving the tester verification problem.

Symbolic model checking [24, 126] is an efficient way of alleviating the state explosion problem. The basic idea is to represent the state space implicitly using symbolic means. In their seminal paper Burch et al. [24] used propositional logic formulae manipulated with (ordered) Binary Decision Diagrams (BDDs). Using this arrangement they succeeded in model checking systems with unprecedently large state spaces. BDDs are a canonical representation for Boolean formulas. They can succinctly represent many Boolean functions. However, the efficiency of the BDD representation for a function is dependent on finding good variable ordering for the variables in the Boolean formula. This can be difficult, and there are functions which do not have any succinct BDD representation [22]. The problem manifests itself in model checking when the BDD representing the currently reachable state space (or equivalently the Boolean formula) is computed. Unpredictable blow-ups in memory usage can occur if the current variable order is unsuitable for the current Boolean formula. For this reason, several variable ordering heuristics [137] and partitioning methodologies [23, 129] have been developed for BDDs.

In bounded model checking [14] (BMC) a limited model checking problem is considered: only counterexamples of a fixed length k are sought for. By letting the bound k grow incrementally we can prove that the systems contains no counterexamples of length k or shorter. For a finite state system the method is complete if one lets the bound grow large enough. However, determining exactly how large the bound must be is a hard problem. Bounded model checking uses the same basic idea as symbolic model checking with BDDs: the state space of the system is represented implicitly using Boolean formulas. However, Boolean formulas are not represented using a canonical form. Instead the BMC problem defined above is mapped to the propositional satisfiability problem (SAT). BMC has its roots in similar methods employed for AI planning problems [107]. Given a system M, a temporal logic formula  $\psi$  and a bound k, a Boolean formula is constructed which is satisfiable if and only if M has a counterexample of length k to  $\psi$ . A propositional satisfiability solver is used to perform the query. Solving the SAT problem from a BDD representation is easy, but the canonical representation of Boolean formulas can unexpectedly blow-up. In BMC, the growth of the size of the BMC formulas can be known in advance, but predicting the running times of the SAT solver is difficult. BMC is particularly good at finding short counterexamples, and there are several papers describing successful industrial applications of BMC [15, 39, 17]. The size and efficiency of the encoding into propositional logic affects the performance of BMC. In [P4, P5] we have investigated efficient encodings for LTL and its generalisation PLTL.

There are also other ways to implement symbolic model checking without BDDs. Many of these are attempts to remedy the problems encountered when using BDDs. Verification using Boolean expression diagrams [172] (BEDs) aims at combining the advantage of BDDs and compact propositional logic expressions by combining them in a hybrid data structure. The use of BDDs allows easily checking whether the complete state space has been explored, and the compact propositional representation alleviates the space requirements of the BDDs. Another approach is to strictly use an efficient propositional representation as in [2]. Symbolic reachability analysis is achieved by using quantifier elimination, which can, however, be time consuming and cause a blow-up in the propositional expression. Quantifier elimination can be avoided if a SAT solver that can return all possible solutions to the propositional formula is used. This approach is used in [77]. However, the representation of all solutions as a Boolean formula can be exponential in the number of propositional variables.

## **1.1 CONTRIBUTIONS**

In this dissertation we study methods and algorithms that aim at facilitating more efficient verification, especially model checking. Publications [P1]–[P3] describe ways to improve model checking and verification using the automata-theoretic approach. In publications [P4]–[P5] we discuss novel methods for bounded model checking.

The main contributions of each publication are the following:

- [P1] An algorithm based on [112] for translating LTL safety formulas to finite automata is presented. Experimental results indicate that the tool is competitive compared to tools translating LTL to Büchi automata, and that treating safety as a special case improves performance. Additionally, the implemented translation tool scheck can identify pathological safety formulas. Pathological safety formulas are safety formulas without (comparatively) succinct bad prefixes and therefore are inefficient to model check using the same techniques as other safety formulas.

- [P2] Modular analysis is a way of alleviating the state explosion problem for modular Petri nets. An automata-theoretic method for model checking the temporal logic LTL-X compatible with modular analysis is presented. The method retains the ability of modular analysis to exploit invisible transitions to reduce the state space. Experimental results show the same mixed results as for modular analysis in general.

- [P3] Testers are an alternative formalism to LTL and Büchi automata for specifying properties of a reactive system. They have a more refined view of visibility than standard Büchi automata synchronisation, and can therefore allow a more fine grained treatment of concurrency to alleviate the state explosion problem. The problem of on-the-fly verification with testers is analysed and solved. An efficient on-the-fly algorithm is presented an proved correct.

- [P4] A succinct SAT encoding of the bounded LTL model checking is presented. The size of the encoding is linear in the bound and the size of the formula. The encoding has been implemented on top of the NuSMV2 model checker [28]. Experiments show that the encoding scales better than previous encodings both in the length of bound and the size of the formula.

- [P5] Based on the LTL encoding in [P4], a SAT encoding of the bounded PLTL model checking is presented. The size of the encoding is linear in the bound and quadratic in the size of the formula. However, if the nesting depth of past operators is fixed the encoding is also linear in the size of the formula. The experimental results confirm that the encoding produces smaller SAT instances and that SAT solvers are able to return results faster than previous implementations.

The Structure of the Dissertation The dissertation consists of five publications and this dissertation summary, and has the following structure.

In Section 2 we introduce the most important concepts in model checking LTL, the main theme of this dissertation. The automata-theoretic approach to model checking, with special emphasis on results related to publications [P1]–[P3] are presented in Section 3. In Section 4 we discuss bounded model checking and describe the results of publications [P4]–[P5]. Conclusions and future work are discussed in Section 5.

# 2 MODEL CHECKING LTL

The basic problem this work examines is model checking the temporal logic LTL. In this section we introduce the notation used throughout the text and define the central problems.

We use Kripke structures in their most basic form as the model of computation. The model is appropriate for reactive computation where the relative order of events matters but the absolute time difference between events does not. We restrict our attention to finite state systems. Although this is a fairly limited model it can with appropriate abstractions capture a large class of systems.

We define a Kripke structure in the following way.

**Definition 1** A Kripke structure is tuple  $M = \langle S, \delta, s_0, l \rangle$ , where

- *S* is a finite set of states,

- δ ⊆ S × S is the transition relation such that for all s ∈ S there exists s' ∈ S with (s, s') ∈ δ,

- $s_0 \in S$  is the initial state and

- $l : S \rightarrow 2^{AP}$  is a labelling function, where AP is a set of atomic propositions.

An execution is an infinite sequence of states  $\sigma = s_0 s_1 s_2 \dots$  such that  $s_0$  is the initial state and  $(s_i, s_{i+1}) \in \delta$  for all  $i \ge 0$ .

A Kripke structure can be seen as defining a language of infinite words over  $2^{AP}$ , a fact which is exploited by the automata theoretic approach to model checking. The language of a Kripke structure M is denoted  $\mathcal{L}(M)$  and defined by  $\mathcal{L}(M) = \{l(\sigma) \mid \sigma \text{ is an excution of } M\}$ , where we have generalised l(s) to sequences in the natural way. Executions  $\sigma$  projected with the labelling function  $l(\sigma)$  are referred to as *computations*. Although we only allow non-terminating executions we can model deadlocking executions by adding a selfloop to a deadlocking state.

We use the temporal logic LTL to specify legal computations of a Kripke structure. An LTL formula  $\varphi$  is defined over a set of atomic propositions *AP*. The syntax of LTL is given by the following inductive definition:

- 1.  $\psi \in AP$  is an LTL formula.

- 2. If  $\psi_1$  and  $\psi_2$  are LTL formulae then so are  $\neg \psi_1$ ,  $\mathbf{X} \psi_1$ ,  $\psi_1 \mathbf{U} \psi_2$ ,  $\psi_1 \mathbf{R} \psi_2$ ,  $\psi_1 \wedge \psi_2$  and  $\psi_1 \vee \psi_2$ .

The temporal operators are the next-time operator  $\mathbf{X}$ , the until-operator  $\mathbf{U}$ , and its dual the release-operator  $\mathbf{R}$ . Given an LTL formula  $\psi$ , the set of unique subformulas of  $\psi$  is denoted by  $cl(\psi)$  and the shorthand  $|\psi|$  denotes the cardinality of  $cl(\psi)$ .

The semantics of LTL is is defined over computations  $\pi = \sigma_0 \sigma_1 \sigma_2 \dots$ with  $\sigma_i \in 2^{AP}$ . We say that  $\pi$  is a model of  $\psi$  at position *i*, denoted  $\pi^i \models \psi$ , when the inductively defined relation ' $\models$ ' holds:

$$\begin{array}{lll} \pi^{i} \models \psi & \Leftrightarrow & \psi \in \sigma_{i} \text{ for } \psi \in AP. \\ \pi^{i} \models \neg \psi & \Leftrightarrow & \pi^{i} \not\models \psi. \\ \pi^{i} \models \psi_{1} \lor \psi_{2} & \Leftrightarrow & \pi^{i} \models \psi_{1} \text{ or } \pi^{i} \models \psi_{2}. \\ \pi^{i} \models \psi_{1} \land \psi_{2} & \Leftrightarrow & \pi^{i} \models \psi_{1} \text{ and } \pi^{i} \models \psi_{2}. \\ \pi^{i} \models \mathbf{X} \psi & \Leftrightarrow & \pi^{i+1} \models \psi. \\ \pi^{i} \models \psi_{1} \mathbf{U} \psi_{2} & \Leftrightarrow & \exists n \geq i : \pi^{n} \models \psi_{2} \text{ and } \pi^{j} \models \psi_{1} \text{ for all } i \leq j < n. \\ \pi^{i} \models \psi_{1} \mathbf{R} \psi_{2} & \Leftrightarrow & \forall n \geq i : \pi^{n} \models \psi_{2} \text{ or } \pi^{j} \models \psi_{1} \text{ for some } i \leq j < n. \end{array}$$

When  $\pi^0 \models \psi$  we usually simply write  $\pi \models \psi$ . Commonly used abbreviations are the standard Boolean shorthands  $\top \equiv p \lor \neg p$  for some  $p \in AP$ ,  $\bot \equiv \neg \top, p \Rightarrow q \equiv \neg p \lor q, p \Leftrightarrow q \equiv (p \Rightarrow q) \land (q \Rightarrow p)$ , and the derived temporal operators  $\mathbf{F} \psi \equiv \top \mathbf{U} \psi$  ('finally'),  $\mathbf{G} \psi \equiv \neg \mathbf{F} \neg \psi$  ('globally'). We use LTL-X to denote the subset of LTL without the next-operator  $\mathbf{X}$ .

In some cases it is desirable to rewrite a formula to *positive normal form*, where negation only occurs in front of atomic propositions. This can be accomplished using the dualities  $\neg (\psi_1 \mathbf{U} \psi_2) \equiv \neg \psi_1 \mathbf{R} \neg \psi_2, \neg (\psi_1 \mathbf{R} \psi_2) \equiv \neg \psi_1 \mathbf{U} \neg \psi_2, \neg \mathbf{X} \psi \equiv \mathbf{X} \neg \psi$  and de Morgan's laws for propositional logic.

The basic problem of satisfiability for LTL, i.e. does an LTL formula  $\psi$  have any model  $\pi$  such that  $\pi \models \psi$  is PSPACE-complete in the size of the formula [151]. Determining if an LTL formula accepts all models, the validity problem, can be solved by negating the given formula and solving the satisfiability problem. Validity is also a PSPACE-complete problem [151].

There are two interesting model checking problems w.r.t. Kripke structures. The so called existential model checking problem asks, given a Kripke structure M and an LTL formula  $\psi$ , does M have a computation  $\pi$  such that  $\pi \models \psi$ . The dual of the existential problem is the universal problem that asks if all computations  $\pi$  of M are models of  $\psi$  (denoted  $M \models \psi$ ). The problems are dual in the sense that  $M \not\models \psi$  iff  $\pi \models \neg \psi$  for some computation  $\pi$  of M. Solving the model checking problem for Kripke structures is PSPACE-complete in the size of the formula [151, 168]. The complexity of the problem is only linear in the size of the Kripke structure |M|, but |M|can be very large due to the state explosion problem. The precise complexity of model checking a single ultimately periodic computation, i.e. deciding whether  $\pi \models \psi$ , where  $\pi = u(v)^{\omega}$  and  $u, v \in (2^{AP})^*$ , is currently unknown [118]. It is an interesting problem because LTL model checking can be decided by only studying ultimately periodic computations [168]. The problem is in P and at least NC<sub>1</sub>-hard [118], but efforts to prove the problem NL-hard have so far failed. For the at least exponentially more succinct logic NLTL (a linear temporal logic with forgettable past) the problem is P-complete [118].

An LTL formula  $\psi$  defines a language of infinite words over  $2^{AP}$  given by  $\mathcal{L}(\psi) = \{\pi \in (2^{AP})^{\omega} \mid \pi \models \psi\}$ . Consequently, when LTL is used as a specification language, the language of the formula can be seen as defining the legal computations of the Kripke structure. In this view a Kripke structure is a model of an LTL formula  $\psi$  iff  $\mathcal{L}(M) \subseteq \mathcal{L}(\psi)$ . To solve the satisfiability and validity problems for LTL, we must decide whether  $\mathcal{L}(\psi) = \emptyset$  or  $\mathcal{L}(\psi) = (2^{AP})^{\omega}$  respectively.

Two important logics that LTL is often compared with are the branchingtime logics CTL and CTL\* (see e.g. [36]). CTL\* is a strict superset of LTL, where a formula can contain arbitrarily nested path quantifiers. The path quantifiers express existential or universal choice over paths and can be used to express properties of the form "for all paths in the system, there exists a path to the initial state from any state of the path". Model checking CTL\* is PSPACE-complete [54]. CTL is a syntactic restriction of CTL\* that is important because it has polynomial time model checking algorithms w.r.t. the size of the formula [32].

Although model checking CTL is easier than model checking LTL and CTL\* is more expressive than LTL while retaining the same model checking complexity, this work focuses on LTL and its extensions. Vardi [167] has argued that the linear-time framework is superior to the branching-time framework for several reasons. We repeat some of the reasons here. In practice CTL has proven to be difficult to use. Engineers find the branching nature of time unintuitive. Another important factor is compositional reasoning. CTL is neither expressive enough for compositional reasoning, nor does have it have a complexity theoretical advantage in this domain. All interesting questions in compositional model checking are at least PSPACEcomplete for CTL w.r.t. the size of the formula (the same complexity as LTL). There are also issues that are specific to the research conducted in this work. For branching-time properties it is an open question whether there is any advantage in treating safety properties as a special case [112]. Bounded model checking fits naturally in the linear-time framework while it is not compatible with the general branching-time framework. The work on BMC for branching time has exclusively focused on the universal fragments of branching time temporal logics [132, 174].

# **3 AUTOMATA-THEORETIC METHODS**

The automata-theoretic approach to model checking [115, 168, 166] exploits the close connection between LTL and automata on infinite words. By viewing both the system and the specification as automata, the approach provides a uniform way of deciding essentially all problems related to model checking LTL.

The connection between LTL and automata on infinite words is usually established through languages. An LTL formula defines a language over infinite strings that can be accepted by an automaton on infinite words. The most basic type of automaton on infinite words is called a Büchi automaton.

Let  $w \in \Sigma^{\omega}$  be an infinite word over the alphabet  $\Sigma$ . A Büchi automaton is a tuple  $\mathcal{A} = \langle \Sigma, Q, \delta, Q_0, F \rangle$ , where  $\Sigma$  is the alphabet, Q is a finite set of states,  $\delta : (Q \times \Sigma) \to 2^Q$  is the transition function,  $Q_0 \subseteq Q$  the set of initial states, and  $F \subseteq Q$  is a set of accepting states. A run of the automaton  $\mathcal{A}$  on a word  $w = \sigma_0 \sigma_1 \sigma_2 \ldots \in \Sigma^{\omega}$  is a mapping  $\rho : \mathbb{N} \to Q$  such that  $\rho(0) \in Q_0$ and  $\rho(i+1) \in \delta(\rho(i), \sigma_i)$  for all  $i \ge 0$ . Let  $inf(\rho)$  to denote the set of states occurring infinitely often in the run. A word w is accepted if there is a run  $\rho$ on w such that  $inf(\rho) \cap F \neq \emptyset$ .

A generalised Büchi automaton generalises the acceptance condition of a standard Büchi automaton. The single set of accepting states F is replaced by a family of sets  $\mathcal{F} = \{F_1, F_2, \ldots, F_k\}$ . A word w is accepted if there is a run  $\rho$  on w such that  $\bigwedge_{i=1}^k inf(\rho) \cap F_i \neq \emptyset$ .

A number of papers have considered the problem of efficiently generating a Büchi automaton  $\mathcal{A}$  that accepts exactly the same language as a given LTL formula (see e.g. [67, 44, 64, 156]). The worst case complexity for the size of the automaton is exponential in the size of the formula, which is not surprising since the LTL satisfiability problem can be solved in linear time w.r.t. the size of Büchi automaton representing the LTL formula. Recall that for an LTL formula  $\psi$  and a system M, the property  $\psi$  holds in the system iff  $\mathcal{L}(M) \subset \mathcal{L}(\psi)$ . This is equivalent to  $\mathcal{L}(M) \cap \mathcal{L}(\neg \psi) = \emptyset$ . From this it is straight-forward to derive an automata-theoretic approach to solve the model checking problem. We start by constructing the Büchi automaton  $\mathcal{A}_{\neg\psi}$  for the negation of the property  $\psi$ . Next, the product  $M \times \mathcal{A}_{\neg\psi}$  is computed which accepts the intersection of the languages  $\mathcal{L}(\mathcal{A}_{\neg\psi}) \cap \mathcal{L}(M)$  of the two automata M and  $\mathcal{A}_{\neg\psi}$ . Clearly,  $M \models \psi$  if and only if  $\mathcal{L}(M \times \mathcal{A}_{\neg\psi}) = \emptyset$ . This can be checked by fairly simple graph algorithms, since the language of a Büchi automaton is empty iff there is no reachable accepting state  $q \in F$ such that q can be reached from itself by a non-empty path. We can thus reduce the LTL model checking problem to checking if the language of the product automaton is empty. This is referred to as an emptiness check of an automaton on infinite words.

In the previously presented approach it is important that we can directly construct the automaton for the negation of the property. Complementing a Büchi automaton is complicated and has an exponential  $(2^{O(n \log n)})$  worst case lower bound [139]. If the automaton for the LTL formula is deterministic, complementing the Büchi automaton is a linear-time procedure that only doubles the size of the automaton [114]. However, deterministic Büchi

automata cannot express all LTL properties (see e.g. [166]).

There are several possible ways of determining whether  $\mathcal{L}(M \times \mathcal{A}_{\neg \psi}) = \emptyset$ . If we are working in a explicit state context the most common solutions either use some variant of the nested depth-first algorithm [42, 90] or an algorithm based on Tarjan's algorithm to compute the maximal strongly connected components (SCCs) for a directed graph [155]. An SCC is a maximal subset of states  $C \subseteq Q$  of the automaton such that for all  $q_i, q_j \in C$  there is a path from  $q_i$  to  $q_j$  and vice versa. Both approaches solve the emptiness problem in linear time w.r.t. the size of the automaton. Section 3.3 discusses explicit state algorithms for checking emptiness in detail.

# 3.1 MODEL CHECKING SAFETY PROPERTIES

A very interesting subclass of all properties specifiable with LTL (or more generally all  $\omega$ -regular properties) are those for which *all* counterexamples are finite. LTL is defined over infinite words but a finite counterexample can be understood as saying that any continuation of a finite counterexample is also a counterexample. For this subclass of properties, it is possible to detect violations of the property by analysing only finite computations. Thus, these properties in one sense require that "nothing bad happens", because once a system leaves the set of safe states the property is irrevocably violated. The properties are therefore referred to as *safety properties*. Properties for which *all* counterexamples are infinite are called liveness properties. Any property can be expressed as a conjunction of a safety and a liveness property [3]. More details on the classification can be found in [4].

Since safety properties have finite counterexamples, we can for each LTL safety property construct a standard automaton on finite words (FSA) that accepts all violating computations for the given property. This automaton can be doubly exponential in the size of the formula in the worst case [112]. However, if we restrict ourselves to safety properties with so called informative counterexamples (also called non-pathological formulas), only a worst case singly exponential automaton is required. This is interesting because the algorithmics for finite automata is simpler than for Büchi automata. The language of a standard finite automaton is non-empty if some final state can be reached. Model checking safety formulas can therefore be reduced to reachability. Compared with general LTL properties where model checking is reduced through Büchi automata to repeated reachability of a set of accepting states, model checking safety properties is much simpler.

Model checking safety properties is an interesting special case of the general model checking problem. Although model checking finite state systems remains PSPACE-complete w.r.t. the given LTL safety formula [150], the simpler algorithms required for model checking safety properties can in some cases reduce an undecidable problem to a decidable one. One concrete example is model checking state-based LTL for (unbounded) Petri nets [58]. Another example, where the difference is not quite as radical, is BDD-based model checking. Solving the problem for the safety case can in practice be considerably easier than the general case [61], although the difference in the number of image computations is linear vs.  $n \log n$  [18] or quadratic [53], depending on the used approach. Also for finite complete prefixes safety is much easier than the general case [84].

There are three basic problems to be solved when applying the automatatheoretic approach to model checking safety properties:

- Deciding if the given LTL specification is actually a safety property.

- Deciding if the given LTL specification is pathologically safe.

- Constructing an FSA accepting all computations violating the safety specification.

The two first problems are PSPACE-complete in the size of the formula [150, 112].

#### 3.1.1 Safety Properties

LTL safety properties can be formally defined using the language characterisation of properties (see e.g. [112]). Let  $L \subseteq \Sigma^{\omega}$  be a language on infinite words over an alphabet  $\Sigma$ . We say that a finite word  $x \in \Sigma^*$  is a *bad prefix* for a language L, if for every  $y \in \Sigma^{\omega}$  we have that  $x \cdot y \notin L$ . Given a language L, if all  $w \in \Sigma^{\omega} \setminus L$  have a bad prefix we call L a safety language. An LTL formula is a safety property if it defines a safety language.

Safety properties with only informative counterexamples are of special interest, since a singly exponential FSA can capture all counterexamples (bad prefixes). An informative counterexample for an LTL formula can be seen as explaining the failure of each subformula for the given formula. All subformulas in the original formula have a reason for not holding. Let  $\psi$  be an LTL formula in positive normal form and  $\pi$  a finite computation  $\pi = \sigma_0 \sigma_1 \dots \sigma_n$ . The computation  $\pi$  is informative for  $\psi$  iff there exists a mapping  $L : \{0, \dots, n+1\} \rightarrow 2^{cl(\neg\psi)}$  such that the following conditions hold:

- $\neg \psi \in L(0)$ ,

- L(n+1) is empty, and

- for all  $0 \le i \le n$  and  $\varphi \in L(i)$ , the following hold.

- If  $\varphi$  is an atomic proposition, then  $\varphi \in \sigma_i$ .

- If  $\varphi = \varphi_1 \lor \varphi_2$ , then  $\varphi_1 \in L(i)$  or  $\varphi_2 \in L(i)$ .

- If  $\varphi = \varphi_1 \land \varphi_2$ , then  $\varphi_1 \in L(i)$  and  $\varphi_2 \in L(i)$ .

- If  $\varphi = \mathbf{X} \varphi_1$ , then  $\varphi_1 \in L(i+1)$ .

- If  $\varphi = \varphi_1 \mathbf{U} \varphi_2$ , then (i)  $\varphi_2 \in L(i)$  or (ii)  $(\varphi_1 \in L(i)$  and  $\varphi_1 \mathbf{U} \varphi_2 \in L(i+1)$ ).

- If  $\varphi = \varphi_1 \mathbf{R} \varphi_2$ , then (i)  $\varphi_2 \in L(i)$  and (ii)  $(\varphi_1 \in L(i) \text{ or } \varphi_1 \mathbf{R} \varphi_2 \in L(i+1))$ .

If  $\pi$  is informative for  $\psi$ , the mapping *L* is called the *witness* for  $\neg \psi$  in  $\pi$ .

The bad prefixes for a safety formula  $\psi$  can be used to classify formulas based on how well their counterexamples explain the violation of the

property. A safety formula  $\psi$  is *intentionally* safe iff all the bad prefixes for  $\psi$  are informative. The formula  $p \mathbf{U} q \vee \mathbf{G} p$  is intentionally safe. A formula  $\psi$  is *accidentally* safe iff every computation that violates  $\psi$  has an informative prefix. In other words,  $\psi$  can have bad prefixes which are not informative. Every computation is, however, guaranteed to have at least one informative prefix. For instance,  $\mathbf{G} \ (p \Rightarrow (\mathbf{X} \mathbf{G} q \wedge \neg \mathbf{X} q))$  is accidentally safe. A safety formula  $\psi$  is *pathologically* safe if there is a computation that violates  $\psi$  and has no informative bad prefix. The formula  $\mathbf{G} q \vee \mathbf{G} r \vee (\mathbf{G} \ (q \vee \mathbf{F} \mathbf{G} p) \wedge \mathbf{G} \ (r \vee \mathbf{F} \mathbf{G} \neg p))$  is pathologically safe [112]. A safety property for which all bad prefixes are not informative must contain some conflicting requirements or be vacuous in some sense. A pathological formula is always equivalent to some intentionally safe formula [112], but no procedure to rewrite a pathologically safe formula to an equivalent intentionally safe formula has been described in the literature.

### 3.1.2 Algorithms

Kupferman and Vardi [112] have showed that it is possible to construct an automaton, exponential in the size of the formula, which recognises all informative bad prefixes. An automaton recognising all informative bad prefixes can be used for model checking all non-pathological formulas but could potentially miss counterexamples for pathological safety formulas. Thus, if we want to avoid the doubly exponential construction to detect all bad prefixes, a method for determining whether a formula is pathological is needed. Sistla [150] has showed that the temporal operators G, R and X form a syntactically safe subset of LTL when only positive combinations of these operators are allowed. Syntactically safe LTL formulas are always either intentionally safe or accidentally safe [112]. If all interesting properties could easily be expressed in this subset we would not need to check whether a formula is pathological. However, many interesting safety formulas are not syntactically safe. One example is the safety formula **G**  $((q \land \neg r \land \mathbf{F} r) \Rightarrow \neg p \mathbf{U} r)$  from the specification pattern templates [50] that expresses "p is false between qand r".

Let  $\psi$  be an LTL formula and  $\mathcal{A}^{i}_{\neg\psi}$  an FSA accepting all informative bad prefixes of  $\psi$ .  $\mathcal{A}^{i}_{\neg\psi}$  can define a language over infinite strings, which we denote by  $\mathcal{L}_{\omega}(\mathcal{A}^{i}_{\neg\psi})$ , if we see  $\mathcal{A}^{i}_{\neg\psi}$  as defining the good finite prefixes of the language. An infinite string belongs to  $\mathcal{L}_{\omega}(\mathcal{A}^{i}_{\neg\psi})$  iff it has finite good prefix. A Büchi automaton accepting  $\mathcal{L}_{\omega}(\mathcal{A}^{i}_{\neg\psi})$  can be obtained by interpreting  $\mathcal{A}^{i}_{\neg\psi}$ as a Büchi automaton and adding a selfloop labelled with  $2^{AP}$  to the unique accepting state of  $\mathcal{A}^{i}_{\neg\psi}$ . Then,  $\psi$  is not pathological iff  $\mathcal{L}(\neg\psi) \subseteq \mathcal{L}_{\omega}(\mathcal{A}^{i}_{\neg\psi})$

In [**P1**] we presented a decision procedure for pathological formulas. The procedure is not complexity theoretically optimal, but seems to work fairly well in practice. Let  $\bar{\mathcal{A}}^i_{\neg\psi}$  denote the complement of  $\mathcal{A}^i_{\neg\psi}$  when it is seen as a Büchi automaton. Recall that deterministic Büchi automata can be complemented with a linear-time procedure. Given an LTL formulas  $\psi$ , the steps in the procedure are the following:

1. Construct a *deterministic* finite automaton  $\mathcal{A}^{i}_{\neg\psi}$  for the informative bad prefixes of  $\psi$ .

- 2. Construct a Büchi automaton  $\mathcal{B}_{\neg\psi}$  for  $\neg\psi$ .

- 3. Interpret  $\mathcal{A}^{i}_{\neg\psi}$  as a Büchi automaton, and complement this deterministic Büchi automaton to produce the automaton  $\overline{\mathcal{A}}^{i}_{\neg\psi}$ .

- 4. Emptiness check  $\bar{\mathcal{A}}^i_{\neg\psi} \times \mathcal{B}_{\neg\psi}$ . Then,  $\psi$  is not pathological iff  $\mathcal{L}(\bar{\mathcal{A}}^i_{\neg\psi} \times \mathcal{B}_{\neg\psi}) = \emptyset$ .

As long as the size of  $\mathcal{A}^{i}_{\neg\psi}$  remains reasonable this procedure works fairly well. An interesting property of the definition of pathological safety formulas is that any non-safety property will also be classified as pathological. No separate test is therefore needed. This can be seen from the definition of safety languages. Any non-safety formula  $\varphi$  must have at least one infinite counterexample that does not have a bad prefix and can therefore not be captured by  $\mathcal{L}_{\omega}(\mathcal{A}^{i}_{\neg\psi})$ .

A prerequisite for checking if a formula is pathologically safe is the ability to construct a deterministic automaton that accepts all informative prefixes. Kupferman and Vardi [112] have derived an algorithm from the definition of informativeness. The algorithm produces a *reverse deterministic* finite automaton exponential in the size of the formula which is suitable for use in symbolic model checkers. An automaton is reverse deterministic if for a fixed letter  $\sigma \in \Sigma$  each state has unique predecessor for that letter. This automaton is especially suitable for backwards symbolic reachability analysis [112].

In [P1] we presented an algorithm for an automaton accepting all informative prefixes of a safety property. The algorithm is a refinement the algorithm presented in [112]. Our version is more suitable for explicit state model checkers. The refined algorithm applies some of the standard reduction tricks already presented in [44] to produce small automata. Additionally, the implemented tool can determinise and minimise the produced reverse deterministic automaton. Minimisation was implemented after [P1] had been published. Determinising the automaton is usually a good idea for two reasons: the deterministic automata tend to produce smaller product state spaces [60, P1, 145]. It is of course possible that determinising the automaton causes an exponential blow-up.

The algorithm as presented in [P1] contained a two small bugs, and additionally we have recently discovered a way to make the algorithm more efficient in the case where the LTL formula contains the next-operator. Therefore, we show the improved and correct construction here. The two small bugs that have been corrected are the following: In [P1] line 26 was placed between lines 24 and 25. This would cause incorrect results in the computation of S', since  $sat(S, S', \psi)$  would return the wrong results. The second error was that the **if** on line 29 was missing, and thus all states would be added to the working set X without checking whether they had been encountered before. In order for the algorithm to terminate, the **if** is required.

We have recently discovered a way to optimise the algorithm when the formula under inspection contains the **X**-operator. The optimisation does not require any changes in the pseudocode of the algorithm. Only the definitions of  $rcl(\psi)$  and  $sat(S, S', \psi)$  change slightly. The new definitions are given below.

As only the absolutely necessary notation is defined here, we refer to [**P1**] for a more detailed explanation of the construction. The construction is based on labelling the states of the automaton with subformulas. A label can be seen as corresponding to a proof requirement. If we reach a state with the empty label, there are no proof requirements left and we have found a witness for the formula. Symmetrically, all states labelled with the full formula are designated as initial states.

We define the restricted closure  $rcl(\psi)$  of an LTL formula  $\psi$  (in positive normal form) as smallest set satisfying the following constraints.

- $\psi \in rcl(\psi)$ .

- If  $\psi_1 \mathbf{U} \psi_2 \in cl(\psi)$ , then  $\psi_1 \mathbf{U} \psi_2 \in rcl(\psi)$ .

- If  $\psi_1 \mathbf{R} \psi_2 \in cl(\psi)$ , then  $\psi_1 \mathbf{R} \psi_2 \in rcl(\psi)$ .

- If  $\mathbf{X} \psi_1 \in cl(\psi)$  then  $\psi_1 \in rcl(\psi)$ .

The intuition behind the restricted closure is that we only include the information which is necessary to remember for evaluating the temporal formulas. Because we minimise the information in the labels of the states, the missing information must be computed and expressed in the transitions from one state to another. Let S, S' be subsets of  $cl(\psi)$ . We define the function  $sat(\psi, S, S')$  in the following way.

- sat(true, S, S') = true and sat(false, S, S') = false.

- $sat(\psi, S, S') =$ true if  $\psi \in S$ , otherwise  $sat(\psi, S, S') =$  false.

- $\psi = \psi_1 \land \psi_2 : sat(\psi, S, S') = sat(\psi_1, S, S') \text{ and } sat(\psi_2, S, S').$

- $\psi = \psi_1 \lor \psi_2 : sat(\psi, S, S') = sat(\psi_1, S, S') \text{ or } sat(\psi_2, S, S').$

- $\psi = \mathbf{X} \psi_1 : sat(\psi, S, S') = sat(\psi_1, S', \emptyset).$

The algorithm constructs the automaton by starting from an empty set of requirements and working backwards to construct all predecessors. For each state, we analyse which proof requirements can be discarded by moving to the current state from a potential predecessor. Each predecessor is the maximal set of subformulas compatible with moving to the current state on a certain atomic proposition.

The size of the automaton is in the worst case exponential in the number of temporal operators of the formula. This is better than  $O(2^{|cl(\psi)|})$  that could be achieved with a direct implementation of the algorithm by Kupferman and Vardi [112].

**Theorem 2** The number of states of the automaton  $\mathcal{A}^i_{\psi}$  bounded by  $2^{|rcl(\psi)|}$ . This bound is in  $O(2^{|tf(\psi)|})$ , where  $tf(\psi)$  is the set of temporal subformulas of  $\psi$ .

Constructing finite automata for model checking temporal logic has been considered in several papers. Many of these papers are concerned with the problem of monitoring software or runtime verification. Monitoring running

1 Input: A formula  $\psi$  in positive normal form. 2 Output: A finite automaton  $\mathcal{A}^i_{\psi} = \langle \Sigma, Q, \delta, Q_0, F \rangle$ . 3 **proc** translate( $\psi$ )  $4 F := \{\emptyset\}; \Sigma := 2^{AP};$  $5 Q := X := \{\emptyset\};$ 6 while  $(X \neq \emptyset)$  do 7 S :="some set in X";  $X := X \setminus \{S\}$ for each  $\sigma \in 2^{AP}$  do 8 9  $S' := \sigma;$ 10 for each  $\varphi \in rcl(\psi)$  do //in increasing subformula order 11  $\operatorname{switch}(\varphi)$  begin 12 case  $\varphi = \psi_1 \lor \psi_2$ : 13 if  $(sat(\psi_1, S', S) \text{ or } sat(\psi_2, S', S))$  then  $S' := S' \cup \{\varphi\}$ ; 14 case  $\varphi = \psi_1 \wedge \psi_2$ : 15 if  $(sat(\psi_1, S', S) \text{ and } sat(\psi_2, S', S))$  then  $S' := S' \cup \{\varphi\}$ ; 16 case  $\varphi = \mathbf{X} \psi_1$ : 17 if  $(\psi_1 \in S)$  then  $S' := S' \cup \{\varphi\};$ 18 case  $\varphi = \psi_1 \mathbf{U} \psi_2$ : 19 if  $(sat(\psi_2, S', S) \text{ or } (sat(\psi_1, S', S) \text{ and } \varphi \in S))$ 20 then  $S' := S' \cup \{\varphi\};$ 21 case  $\varphi = \psi_1 \mathbf{R} \psi_2$ : if  $(sat(\psi_2, S', S) \text{ and } (sat(\psi_1, S', S) \text{ or } \varphi \in S))$ 22 then  $S' := S' \cup \{\varphi\};$ 23 24 end 25 od if  $\sigma \notin rcl(\psi)$  then  $S' := S' \setminus \{\sigma\};$ 26 27  $\mathbf{if}(sat(\psi, S', \emptyset)) \mathbf{then} \ Q_0 := Q_0 \cup \{S'\};$ 28  $\delta(S', \sigma) = \delta(S', \sigma) \cup \{S\};$ 29 if  $S' \notin Q$  then  $X := X \cup \{S'\}; Q := Q \cup \{S'\};$ 30 od 31 od

Figure 3.1: Algorithm for constructing a finite automaton for informative prefixes.

software either requires a deterministic automaton or on-the-fly determinisation of the automaton representing the illegal behaviours. Geilen [65] presents a tableau construction for monitoring bad and good prefixes of LTL formulas. The construction is essentially a forward version of the algorithm of Kupferman and Vardi [112] and has the same complexity. Havelund and Roşu [83] describe an algorithm for synthesising monitors for a past temporal logic. The method is similar to the history variables method presented in [12]. Both methods could be used to generate a deterministic finite automaton for a past temporal logic with the syntactic form  $\mathbf{G} \psi$ , where the temporal operators in  $\psi$  must be past operators. See Section 4 for an example of a temporal logic with past operators.

Sen et al. [146] describe a method based on coinduction to generate a minimal deterministic finite automaton for *all* bad prefixes. The intended target application is monitoring of software. The advantage of the method compared with the method described in [112] is that the method generates the optimal (potentially doubly exponential) automaton directly. In [112] an exponential Büchi automaton is generated as an intermediate step.

An automaton for informative bad prefixes can be used to detect minimal counterexamples for intentionally safe formulas. Since not all bad prefixes are detected, minimality for accidentally safe formulas is not guaranteed. However, it is questionable if non-informative counterexamples are useful for debugging purposes. By definition, the non-informative counterexamples are due to formulas that are malformed in the sense that they do not have only informative counterexamples. However, as long as there is no efficient procedure to transform pathological formulas to non-pathological formulas, completeness of a safety model checking procedure cannot be guaranteed without detecting all counterexamples. Understanding and minimising counterexamples is an area which has received a fair amount of attention lately [100, 135, 73, 148, 143].

## 3.2 MODEL CHECKING LIVENESS PROPERTIES OF MODULAR PETRI NETS

A popular way of describing systems is using Petri nets [136]. Petri nets can be seen as a generalisation of communicating automata. Concurrency can easily be described with Petri nets and synchronisation is described explicitly.

In their most basic form Petri nets have no concept of a module or a process that could be used to split a system description into parts. Petri nets describe a system as one monolithic object. However, splitting the description is convenient for designers and it has many benefits. Reasons often cited are that a modular description (i) matches the system design better, (ii) facilitates reuse of the design, (iii) enables reuse of analysis results and (iv) makes it is easier to get an overview of the system.

Modular Petri nets [26] extend Petri nets by adding a module/process structure to Petri nets. In modular Petri nets modules interact through transition fusion and shared places. We will however restrict our attention to nets using only transition fusion. Shared places can always be simulated by transition fusion [26]. This section presents an automata-theoretic method for model checking modular Petri nets.

#### 3.2.1 Petri Nets and Modular Nets

This section presents the relevant notations and definitions.

**Definition 3** A Place/Transition net (PT-net) is a tuple  $N = (P, T, W, M_0)$ where P is a finite set of places, T is a finite set of transitions such that  $P \cap T = \emptyset$ ,  $W : (P \times T) \cup (T \times P) \rightarrow \mathbb{N}$  is the arc weight function and  $M_0 : P \rightarrow \mathbb{N}$ is the initial marking.

A marking is a multiset over P. For a transition  $t \in T$  we identify  $t^{\bullet}(\bullet t)$  with the multiset given by  $t^{\bullet}(p) = W(t, p) (\bullet t(p) = W(p, t))$  for any  $p \in P$ .

A transition  $t \in T$  is enabled in a marking M iff  $\bullet t \subseteq M$ . In a marking M, an enabled transition t can occur resulting in the marking  $M' = M - \bullet t + t^{\bullet}$ . This is denoted  $M \xrightarrow{t} M'$ . The notation can be generalised to a sequence  $\sigma = t_1 t_2 \dots t_n$  of transitions:  $M_1 \xrightarrow{\sigma} M_{n+1}$  denotes that there exists a sequence of markings such that  $M_1 \xrightarrow{t_1} M_2 \xrightarrow{t_2} \dots \xrightarrow{t_n} M_{n+1}$ . A marking in which no transition is enabled is called a *deadlocking* marking, while any marking that can be produced by the occurrence of a sequence of transitions from the initial marking is called *reachable*.

A modular Petri net describes a system as a collection of Petri nets. Synchronisation between the modules is accomplished using transition fusion.

**Definition 4** A modular PT-net is a tuple  $\mathcal{N} = (S, TF)$  where:

- *S* is a finite set of modules:

- each module  $s \in S$  is a PT-net  $s = (P_s, T_s, W_s, M_{0_s})$ ,

- the sets of nodes corresponding to different modules are pairwise disjoint, i.e., for all  $s_1, s_2 \in S : s_1 \neq s_2 \Rightarrow (P_{s_1} \cup T_{s_1}) \cap (P_{s_2} \cup T_{s_2}) = \emptyset$ .

- Let  $T = \bigcup_{s \in S} T_s$  be the set of all transitions.  $TF \subseteq 2^T$  is a finite set of transition fusion sets such that for all  $tf \in TF$  we have that if  $t_i, t_j \in tf$  and  $i \neq j$  then  $t_i \in T_s \Rightarrow t_j \notin T_s$ . In other words, a module may contribute only one transition to a fusion transition but a transition can participate in several fusion transitions.

A global marking M of a modular net is simply the union of the markings of the subnets, since the places of the subnets are disjoint. We call a transition not part of any transition fusion set an internal transition. By  $M[[\sigma\rangle\rangle M'$ , where  $\sigma = t_0 t_1 t_2 \dots t_n t f$ , we denote that M' is reachable from M by a sequence of internal transitions  $t_0 t_1 t_2 \dots t_n$  followed by a fused transition tf. Christensen and Petrucci [26] have presented a method for computing a synchronisation graph. The graph shows the global behaviour of the system in terms of the fusion transitions.

**Definition 5** Let  $\mathcal{N} = (S, TF, M_0)$  be a modular net with the initial marking  $M_0$ . The synchronisation graph  $\mathbf{G} = (\mathbf{V}, \mathbf{E}, \mathbf{v}_0)$  of the net is defined inductively as follows:

•  $\mathbf{v}_0 = M_0 \in \mathbf{V}$ .

- If  $M \in \mathbf{V}$  and  $M[[t_1t_2...t_ntf\rangle]M''$  then  $(M, tf, M'') \in \mathbf{E}$  and  $M'' \in \mathbf{V}$ .

- V and E contain no other elements.

The synchronisation graph has a few attractive features. It can in some cases be constructed even if the local components have infinite state spaces when considered in isolation [26]. Since the synchronisation graph only includes fusion transitions, it can be much smaller than the reachability graph representing the full behaviour. It is fairly straight-forward to compute interesting properties such as absence of deadlocks using the synchronisation graph, by checking some simple conditions local to the modules [26]. Mäkelä [123] has extended the basic results from standard modular Petri nets to nested modular high-level Petri nets. Nesting allows succinct description of hierarchy and can be very expressive when modelling large systems. Mäkela also describes an implementation of computing the synchronisation graph in the Petri net reachability analyser Maria [122].

It is possible to prove any LTL-X property using an adapted automata theoretic model checking algorithm [P2]. Essentially the model checking problem is reduced to an instance of tester verification, a topic which is discussed in Section 3.3. We say that a transition is *invisible* if it cannot affect the truth value of the atomic propositions of the given LTL formula. The presented method requires that all visible transitions are present in the synchronisation graph. Currently only a simple analysis is made to determine whether a transition is visible and the result is a safe over-approximation. A potential avenue of future work is computing more accurate over-approximations of visibility of transitions.

Constructing the synchronisation graph is similar to a few other methods for alleviating the state explosion problem. Katz and Miller [105] present a method for pruning invisible transitions from the state graph. The method produces a stuttering equivalent [117] state graph w.r.t. to the original state graph at the cost of an additional traversal of the original state graph. Since the reduced state graph is stuttering equivalent to the original state graph, it preserves all LTL-X properties. By applying partial order reduction methods and state space caching methods [69] the performance of the reduction method can be improved significantly. The use of state space caching avoids the overhead of ever having to remember the full state graph while the use of partial order reduction methods both reduces the memory overhead and improves the final result. A disadvantage of the method is that it is incompatible with on-the-fly model checking methods (see below).

Yorav [175] describes a method for path reduction in both sequential program and parallel programs. Again, the idea is based on eliminating all invisible transitions (w.r.t. the specification) from the state graph. The method works on the level of the control flow graph of the given program and produces a reduced control flow graph. The sequential case is extended to the parallel case by applying a modified path reduction to the individual processes which also preserves send and receive statements. The reduced program is stuttering bisimiliar with the original program and therefore preserves all CTL\*-X properties. Kurshan et al. [116] present a method similar to Yorav's method for compressing invisible transitions. Their reasoning is explicitly based on partial order reduction methods for producing a reduced control flow graph. They argue that their method can reduce the state space more aggressively than Yorav's because they can use the theory for partial order reductions instead of only depending on static syntactic transformations.

Compared with the methods of Katz and Miller and Kurshan et al., and Yorav's path reduction method, there are some subtle differences in how model checking is performed in [P2]. The most notable difference is in how loops of invisible transitions are treated. All three previous methods can guarantee that all loops of invisible transitions have their counterparts in the reduced state graph. This allows them to use standard automata theoretic techniques for model checking the state graph. Loops of invisible transition are not preserved by the synchronisation graph. We could force all invisible transitions to appear in the synchronisation graph, but this would certainly eliminate any reduction in the state space we could gain by using it. We therefore choose to modify the standard automata theoretic procedure to use a weaker form of synchronisation and reduce the model checking problem to an instance of tester verification. An interesting topic for future work is whether the definition of the synchronisation graph could be modified to preserve loops of invisible transitions while allowing maximal reduction.

# 3.3 ON-THE FLY VERIFICATION USING TESTERS

An alternative approach to using Büchi automata for model checking and verification is using testers. Testers are a special form of automata that are structurally very similar to Büchi automata. In model checking using Büchi automata the system synchronises at each step with the Büchi automaton. When performing verification with a tester, a more general form of synchronisation is used. The synchronisation explicitly considers the visibility of transitions and a tester only synchronises with visible actions of the system under inspection. This allows testers to be used for verifying systems where a tighter form of synchronisation would reduce the efficiency of certain state space reduction methods such as net unfoldings [59] and modular analysis (see above).

To be able to express all relevant properties, while hampered by the looser than normal synchronisation with the system, the acceptance condition of testers is strictly more general than for Büchi automata. The stronger acceptance condition also allows deterministic testers to accept some languages that require non-deterministic Büchi automata. However, there are languages that cannot be accepted by a deterministic tester but can be captured a non-deterministic one [81].

Verification with techniques related to testers has been considered in several papers. Valmari [163] introduced the tester framework to allow efficient use of stubborn sets, a partial order reduction method. Esparza and Heljanko [59] borrow techniques from testers to facilitate model checking of Petri net unfoldings. As explained in Section 3.2, a similar method is used for model checking modular Petri nets in [**P2**]. Testers are also relevant for compositional verification techniques using compositional behavioural preorders like the NDFD preorder, which is the weakest compositional preorder and equivalence that preserves LTL-X properties [103]. Testers can be used to decide the CFFD behavioural preorder [86], a closely related preorder to NDFD.

### 3.3.1 Labelled Transition Systems and Testers

Testers are usually defined in the framework of *labelled transition systems* (LTSs). An LTS describes a system as an automaton with named actions.