TKK Dissertations 79 Espoo 2007

## DENSE IMPLEMENTATIONS OF BINARY CELLULAR NONLINEAR NETWORKS: FROM CMOS TO NANOTECHNOLOGY

**Doctoral Dissertation**

Jacek Flak

Helsinki University of Technology Department of Electrical and Communications Engineering Electronic Circuit Design Laboratory TKK Dissertations 79 Espoo 2007

### DENSE IMPLEMENTATIONS OF BINARY CELLULAR NONLINEAR NETWORKS: FROM CMOS TO NANOTECHNOLOGY

**Doctoral Dissertation**

#### Jacek Flak

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Department of Electrical and Communications Engineering for public examination and debate in Auditorium S4 at Helsinki University of Technology (Espoo, Finland) on the 29th of June, 2007, at 12 noon.

Helsinki University of Technology Department of Electrical and Communications Engineering Electronic Circuit Design Laboratory

Teknillinen korkeakoulu Sähkö- ja tietoliikennetekniikan osasto Piiritekniikan laboratorio Distribution: Helsinki University of Technology Department of Electrical and Communications Engineering Electronic Circuit Design Laboratory P.O. Box 3000 FI - 02015 TKK FINLAND URL: http://www.ecdl.tkk.fi/ Tel. +358-9-4512271 Fax +358-9-4512269 E-mail: jacek@ecdl.tkk.fi

© 2007 Jacek Flak

ISBN 978-951-22-8853-3 ISBN 978-951-22-8854-0 (PDF) ISSN 1795-2239 ISSN 1795-4584 (PDF) URL: http://lib.tkk.fi/Diss/2007/isbn9789512288540/

TKK-DISS-2321

Multiprint Oy Espoo 2007

# Abstract

This thesis deals with the design and hardware realization of the cellular neural/nonlinear network (CNN)-type processors operating on data in the form of black and white (B/W) images. The ultimate goal is to achieve a very compact yet versatile cell structure that would allow for building a network with a very large spatial resolution. It is very important to be able to implement an array with a great number of cells on a single die. Not only it improves the computational power of the processor, but it might be the enabling factor for new applications as well. Larger resolution can be achieved in two ways. First, the cell functionality and operating principles can be tailored to improve the layout compactness. The other option is to use more advanced fabrication technology – either a newer, further downscaled CMOS process or one of the emerging nanotechnologies.

It can be beneficial to realize an array processor as two separate parts – one dedicated for gray-scale and the other for B/W image processing, as their designs can be optimized. For instance, an implementation of a CNN dedicated for B/W image processing can be significantly simplified. When working with binary images only, all coefficients in the template matrix can also be reduced to binary values. In this thesis, such a binary programming scheme is presented as a means to reduce the cell size as well as to provide the circuits composed of emerging nanodevices with an efficient programmability. Digital programming can be very fast and robust, and leads to very compact coefficient circuits. A test structure of a binary-programmable CNN has been designed and implemented with standard 0.18  $\mu$ m CMOS technology. A single cell occupies only 155  $\mu$ m<sup>2</sup>, which corresponds to a cell density of 6451 cells per square millimeter. A variety of templates have been tested and the measured chip performance is discussed.

Since the minimum feature size of modern CMOS devices has already entered the nanometer scale, and the limitations of further scaling are projected to be reached within the next decade or so, more and more interest and research activity is attracted by nanotechnology. Investigation of the quantum physics phenomena and development of new devices and circuit concepts, which would allow to overcome the CMOS limitations, is becoming an increasingly important science. A single-electron tunneling (SET) transistor is one of the most attractive nanodevices. While relying on the Coulomb interactions, these devices can be connected directly with a wire or through a coupling capacitance. To develop suitable structures for implementing the binary programming scheme with capacitive couplings, the CNN cell based on the floating gate MOSFET (FG-MOSFET) has been designed. This approach can be considered as a step towards a programmable cell implementation with nanodevices. Capacitively coupled CNN has been simulated and the presented results confirm the proper operation. Therefore, the same circuit strategies have also been applied to the CNN cell designed for SET technology. The cell has been simulated to work well with the binary programming scheme applied. This versatile structure can be implemented either as a pure SET design or as a SET-FET hybrid. In addition to the designs mentioned above, a number of promising nanodevices and emerging circuit architectures are introduced.

**Keywords:** Integrated Circuits, Cellular Neural/Nonlinear Networks, Cellular Array Processors, CMOS, Nanotechnology, Single-Electron Tunneling

## Preface

This thesis is the result of the research carried out at the Electronic Circuit Design Laboratory (ECDL) of the Helsinki University of Technology during the years 2001-2007. The research was funded by the Academy of Finland within the projects "Integrated Parallel Processors for Future Data Processing and Analyzing Systems" and "Low power biomorphic neural circuits based on floating gate MOS and SET transistors". Also, the financial support from the Jenny and Antti Wihuri Foundation is greatfully acknowledged.

Throughout the years, the working environment in the laboratory has been an amazing mixture of a great inspiration, challenges, continuous learning and relaxing moments of fun. All the staff at ECDL deserve my gratitude for creating such a fantastic atmosphere. However, I would like to name a few persons for their exceptional contribution. First of all, I need to mention Professor Veikko Porra and Dr. Witold Machowski, since without their idea for having a student exchange I wouldn't be writing these words. I want to thank Professor Kari Halonen for providing me with an interesting research topic, and supervising my postgraduate studies that will be crowned with this dissertation. My introduction to the world of CNNs and lots of efforts in organizing this project have been an invaluable contribution of Professor Ari Paasio, who has mentored my early research. Also, I want to express my gratefulness to Dr. Mika Laiho, who became my longtime tutor when Prof. Paasio has got overwhelmed by the Dean's splendor and duties at the University of Turku. It's been a real pleasure to work with Mika, and I've learned from him a lot. Also, my special thanks go to our dear secretary, Helena Yllö, who (so many times) has made my life easier by taking care of practical matters. She's the person I could rely on whenever facing a bureaucracy. I need to acknowledge Väinö Hakkarainen for all the years of being a great roommate and for the superb music we've used to listen to. Also, countless discussions with Dr. Marko Kosunen, Dr. Lauri Koskinen, Dr. Asko Kananen, Mika Länsirinne, Jonne Lindeberg and Mikko Talonen (to list just a few) have been both thoughtful and enjoyable.

For the hard work of pre-examiners, my special thanks go to Professor Stephen Goodnick (Arizona State University, AZ, USA) and Professor Victor Brea (University of Santiago de Compostela, Spain). Their devotion and a number of invaluable comments have helped me to improve this manuscript.

I want to mention my wife Anne and my son Patrik – my pride and joy, a sunshine of my life. I am grateful for their love, support, understanding and indulgence.

All my friends, here in Finland as well as back there in Poland, must be acknowledged for providing me with great social activities, sharing passions and fun.

Finally, I want to thank my parents Irena and Stanisław and my sister Katarzyna for their persistent support, motivation in the moments of doubt, and all the love they filled my life with.

Espoo, 02.06.2007

Jacek Flak

# Contents

|   | Abs  | tract                                        | i   |

|---|------|----------------------------------------------|-----|

|   | Pref | ace                                          | iii |

|   | Pref | 'ace                                         | iii |

|   | Con  | tents                                        | v   |

|   | Sym  | abols and Abbreviations                      | ix  |

| 1 | Intr | oduction                                     | 1   |

|   | 1.1  | Motivation                                   | 1   |

|   | 1.2  | Research Contribution                        | 3   |

|   | 1.3  | Organization of the Thesis                   | 4   |

| 2 | Cell | ular Neural/Nonlinear Networks               | 7   |

|   | 2.1  | Definitions                                  | 7   |

|   |      | 2.1.1 Neural vs. Nonlinear                   | 7   |

|   |      | 2.1.2 Grid Type and Array Dimension          | 8   |

|   |      | 2.1.3 Neighborhood and Interconnection Types | 8   |

|   | 2.2  | Continuous-Time CNN                          | 10  |

|   | 2.3  | CNN Model Modifications                      | 11  |

|   |      | 2.3.1 CNN Universal Machine                  | 11  |

|   |      | 2.3.2 Full Signal Range CNN                  | 11  |

|   |      | 2.3.3 Positive-Range High-Gain CNN           | 11  |

|   |      | 2.3.4 Discrete-Time CNN                      | 12  |

|   |      | 2.3.5 Binary CNN                             | 12  |

| 3 | Har  | dware Realizations of Array Processors       | 13  |

|   | 3.1  | ACE Series Processors                        | 13  |

|   | 3.2  | Near-Sensor Image Processing                 | 14  |

|                                     | 3.3  | SIMD                       | Current-mode Analogue Matrix Processor              | 15 |

|-------------------------------------|------|----------------------------|-----------------------------------------------------|----|

|                                     | 3.4  | Digital                    | I SIMD Processor                                    | 16 |

|                                     | 3.5  | Binary                     | y I/O CNN-UM                                        | 16 |

|                                     | 3.6  | Memo                       | ry-based Approaches to Parallel Processing          | 18 |

|                                     |      | 3.6.1                      | Content Addressable Memory                          | 18 |

|                                     |      | 3.6.2                      | Computational RAM                                   | 19 |

| 4                                   | Bina | ary Prog                   | gramming Scheme                                     | 23 |

|                                     | 4.1  | Motiva                     | ation                                               | 23 |

|                                     | 4.2  | Introdu                    | uction                                              | 24 |

|                                     | 4.3  | Cell M                     | Iodel                                               | 24 |

|                                     |      | 4.3.1                      | Model Definitions                                   | 24 |

|                                     |      | 4.3.2                      | Basic Cell Structure                                | 25 |

|                                     | 4.4  | Templa                     | ate Robustness                                      | 26 |

|                                     | 4.5  | Perform                    | ming Local Logic Operations                         | 28 |

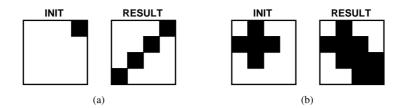

|                                     | 4.6  | Proces                     | sing B-Templates                                    | 29 |

|                                     |      | 4.6.1                      | Neighborhood Threshold Logic                        | 29 |

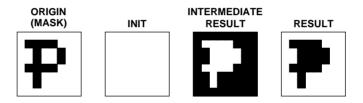

|                                     |      | 4.6.2                      | Processing with the Transient Mask                  | 30 |

|                                     |      | 4.6.3                      | Templates Using Pattern Matching                    | 31 |

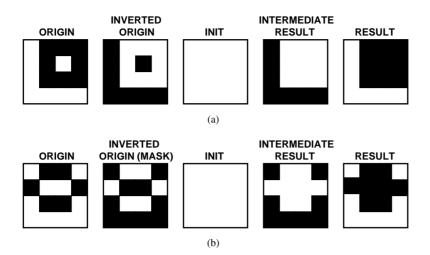

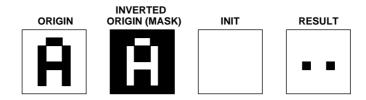

|                                     | 4.7  | Proces                     | sing A-Templates                                    | 31 |

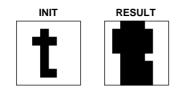

|                                     |      | 4.7.1                      | Computing with the Propagating Wave                 | 31 |

|                                     |      | 4.7.2                      | A-Templates with Positive and Negative Coefficients | 32 |

|                                     | 4.8  | Conclu                     | usions                                              | 32 |

| 5 CMOS Implementation of Binary CNN |      | elementation of Binary CNN | 33                                                  |    |

|                                     | 5.1  | System                     | n Architecture                                      | 34 |

|                                     |      | 5.1.1                      | Cell Model                                          | 34 |

|                                     |      | 5.1.2                      | Cell Design                                         | 36 |

|                                     |      |                            | 5.1.2.1 Computing Kernel                            | 36 |

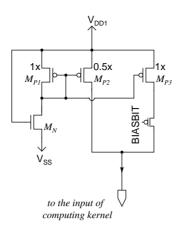

|                                     |      |                            | 5.1.2.2 Coefficient Circuits                        | 38 |

|                                     |      |                            | 5.1.2.3 Bias Circuit                                | 39 |

|                                     |      | 5.1.3                      | Border Cells                                        | 40 |

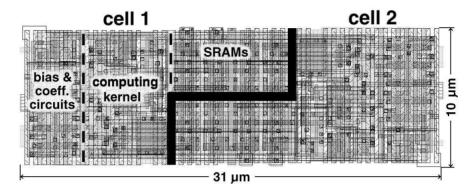

|                                     | 5.2  | Silicon                    | Implementation                                      | 40 |

|                                     |      | 5.2.1                      | Robustness                                          | 40 |

|                                     |      | 5.2.2                      | Layout                                              | 41 |

|                                     | 5.3  | Measu                      | rements                                             | 42 |

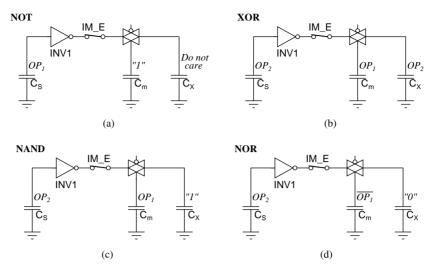

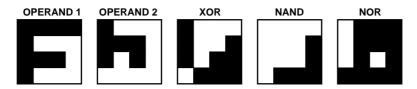

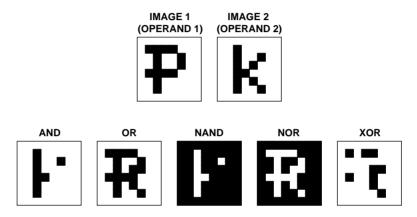

|                                     |      | 5.3.1                      | Logic Operations: NOT, XOR, NAND, NOR               | 42 |

|                                     |      | 5.3.2                      | Processing of Templates                             | 44 |

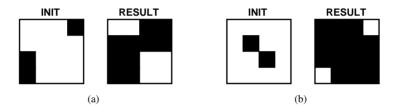

|                                     |      |                            | 5.3.2.1 Wave Propagating A-Templates                | 44 |

|                                     |      |                            |                                                     |    |

|   |      |         | 5.3.2.2 A-Templates With a Fixed State Map 4             | 15 |

|---|------|---------|----------------------------------------------------------|----|

|   |      |         | 5.3.2.3 B-Templates                                      | 16 |

|   |      | 5.3.3   | Speed of Operation                                       | 18 |

|   |      | 5.3.4   | Power Consumption                                        | 18 |

|   | 5.4  | Discus  | ssion                                                    | 19 |

| 6 | Bina | ary CNI | N Based on Floating-Gate MOSFET 5                        | 53 |

|   | 6.1  | Motiva  | ation                                                    | 53 |

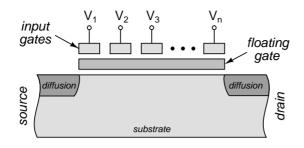

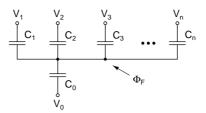

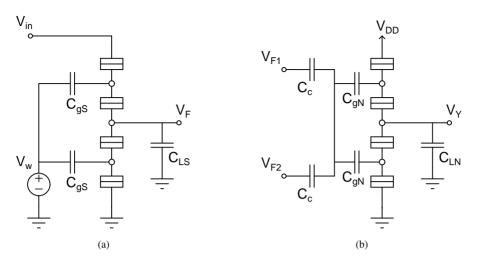

|   | 6.2  | Neuro   | n MOSFET Structure                                       | 54 |

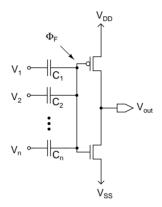

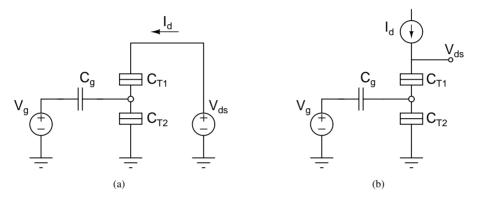

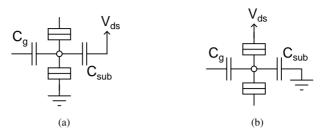

|   | 6.3  | Cell St | tructure                                                 | 55 |

|   |      | 6.3.1   | Coefficient Circuits and Bias                            | 58 |

|   |      | 6.3.2   | Computing Kernel                                         | 58 |

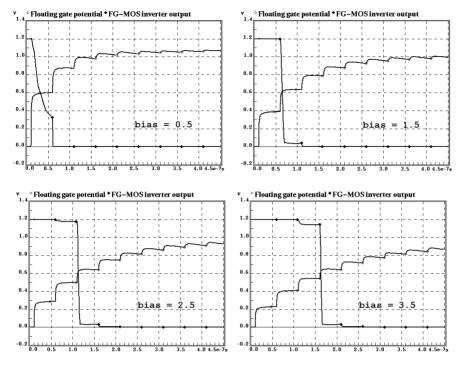

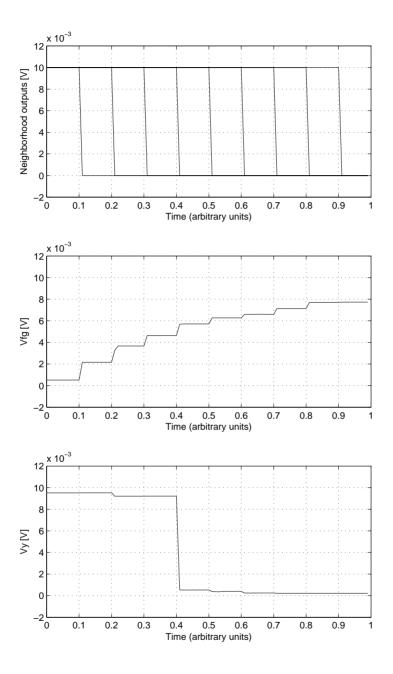

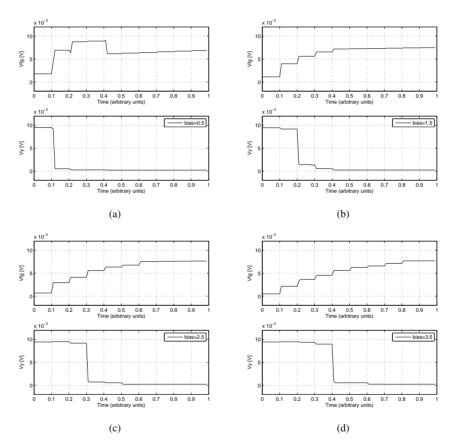

|   | 6.4  | Simula  | ation Results                                            | 59 |

|   |      | 6.4.1   | Cell State vs. Neighborhood and Bias 6                   | 50 |

|   |      | 6.4.2   | Logic Operations                                         | 51 |

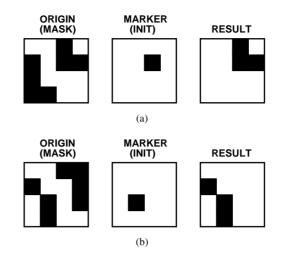

|   |      | 6.4.3   | A-Templates                                              | 52 |

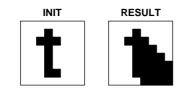

|   |      |         | 6.4.3.1 Simple A-Template: Shadow                        | 52 |

|   |      |         | 6.4.3.2 A-Template With a Fixed State Map: Hole Filler 6 | 52 |

|   |      | 6.4.4   | B-Templates 6                                            | 54 |

|   |      |         | 6.4.4.1 Simple B-Template: Object Increase 6             | 54 |

|   |      |         | 6.4.4.2 Higher Bias Template: Junction Extraction 6      | 54 |

|   | 6.5  | Discus  | ssion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $6$   | 55 |

| 7 | Bina | ary CNI | N Designed for SET Technology 6                          | 67 |

|   | 7.1  | Motiva  | ation                                                    | 57 |

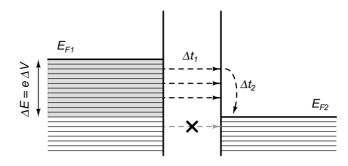

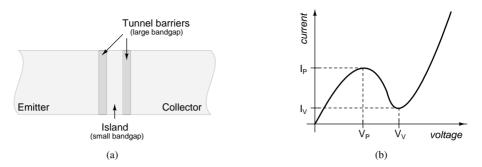

|   | 7.2  | Single  | -Electron Tunneling Technology                           | 58 |

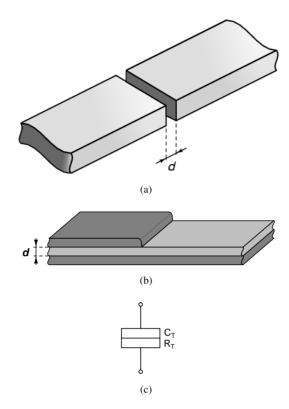

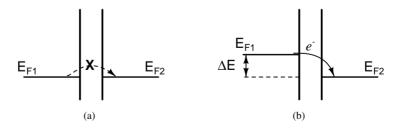

|   |      | 7.2.1   | SET Junction                                             | 58 |

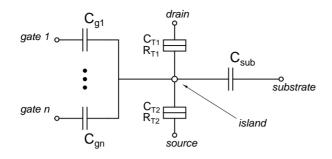

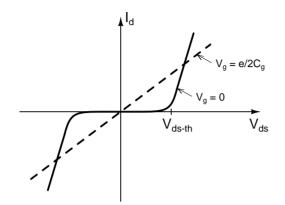

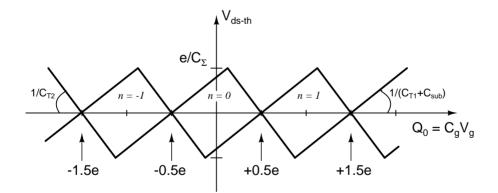

|   |      | 7.2.2   | SET Transistor                                           | 70 |

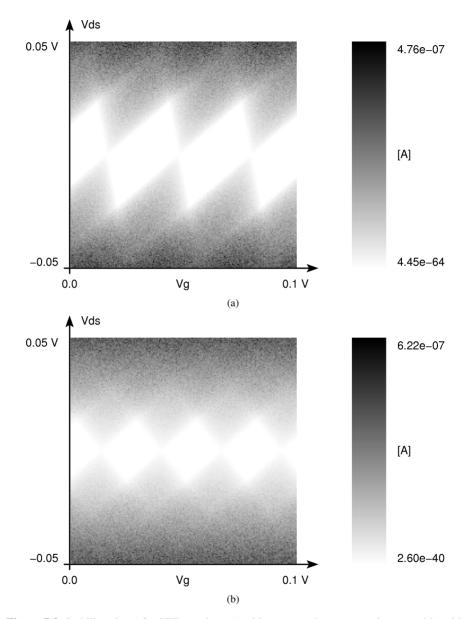

|   |      | 7.2.3   | Operation Regimes                                        | 74 |

|   |      | 7.2.4   | Random Background Charge Effect    7                     | 75 |

|   |      |         | 7.2.4.1 Circumventing the RBC Problem                    | 76 |

|   |      | 7.2.5   | Fabrication                                              | 7  |

|   |      | 7.2.6   | Applications                                             | 78 |

|   |      | 7.2.7   | Discussion                                               | 78 |

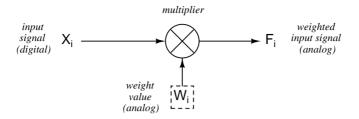

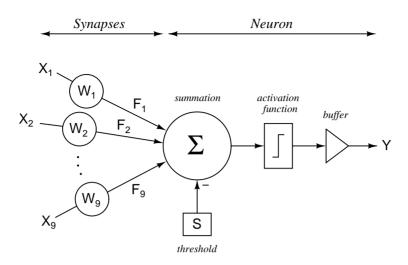

|   | 7.3  | Artific | ial Neural Networks                                      | 30 |

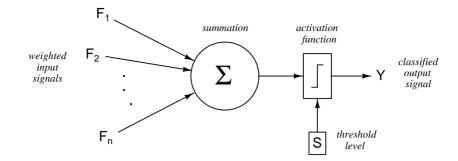

|   |      | 7.3.1   | Components of a Neural Network                           | 80 |

|   |      |         | -                                                        | 30 |

|   |      |         | 7.3.1.2 Neuron                                           | 30 |

|   |      | 7.3.2   |                                                          | 31 |

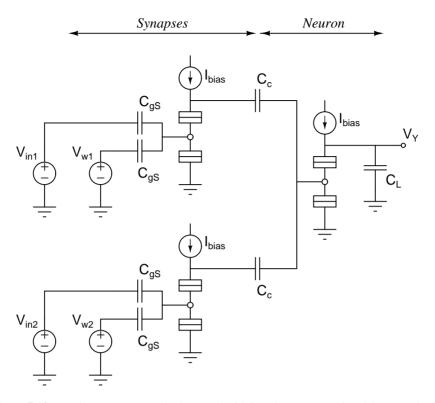

|   | 7.4  | ANN i   | in SET Technology                              | 82  |

|---|------|---------|------------------------------------------------|-----|

|   |      | 7.4.1   | Boltzmann Machine Neuron                       | 82  |

|   |      | 7.4.2   | SET Transistor as a Neural Hardware            | 83  |

|   |      | 7.4.3   | Neural Hardware Based on SET Inverter          | 84  |

|   |      | 7.4.4   | 3IS Cascade as a CNN Cell                      | 85  |

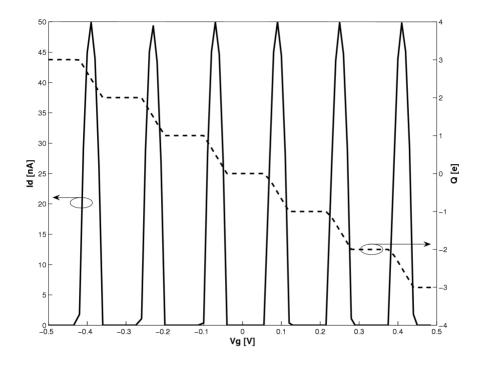

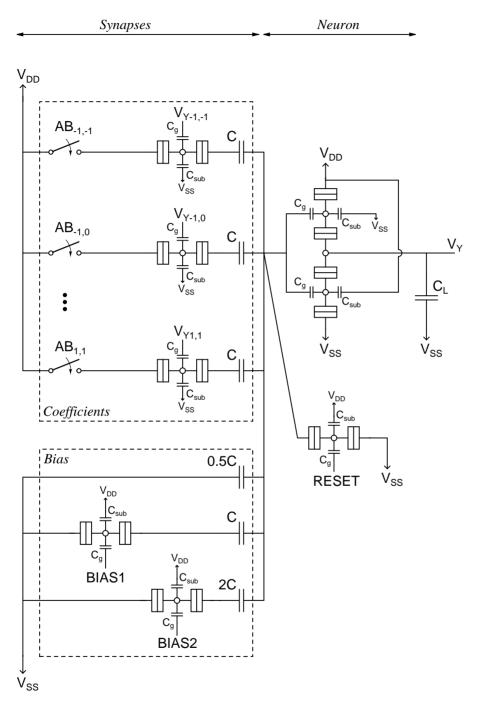

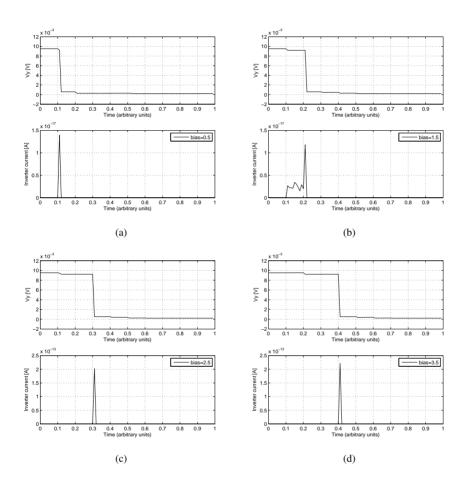

|   | 7.5  | Binary  | Programmable SET-Based CNN Cell                | 86  |

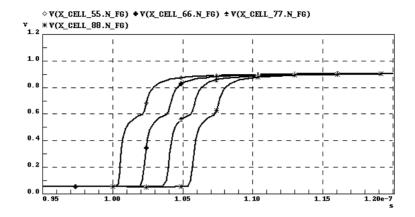

|   | 7.6  | Simula  | ation Results                                  | 87  |

|   | 7.7  | Discus  | ssion                                          | 89  |

| 8 | Oth  | er Pros | pective Nanodevices and Architectures          | 95  |

|   | 8.1  | Emerg   | ing Nanodevices                                | 95  |

|   |      | 8.1.1   | Quantum Dots                                   | 96  |

|   |      | 8.1.2   | Resonant Tunneling Devices                     | 96  |

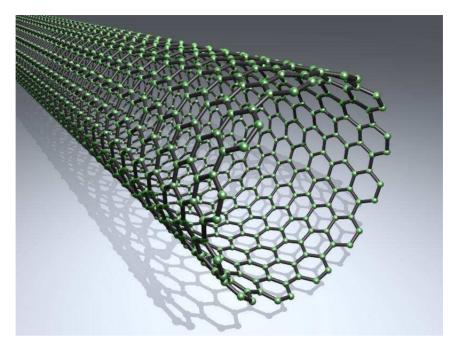

|   |      | 8.1.3   | Carbon Nanotubes                               | 98  |

|   |      | 8.1.4   | Molecular Devices                              | 99  |

|   |      | 8.1.5   | Ferromagnetic Logic Devices                    | 100 |

|   |      | 8.1.6   | Spin Logic Devices                             | 100 |

|   | 8.2  | Novel   | Architectures                                  | 101 |

|   |      | 8.2.1   | Quantum Cellular Automata                      | 101 |

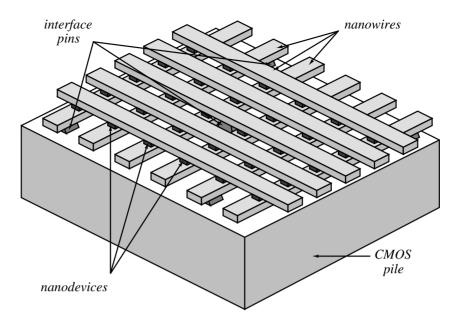

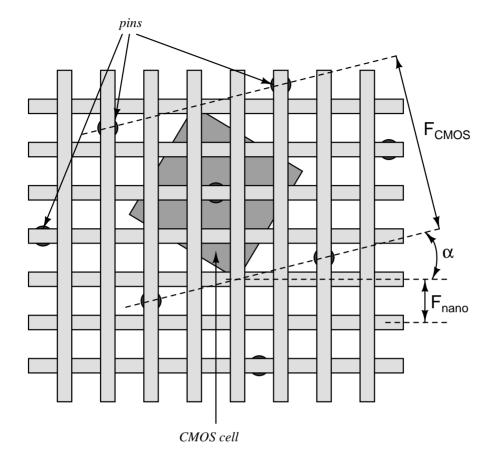

|   |      | 8.2.2   | CMOS-Nanodevice Hybrids                        | 103 |

| 9 | Con  | clusion | s and Future Research                          | 107 |

|   | Bibl | iograpł | ny                                             | 109 |

| A | Bina | ary Tem | iplate Library                                 | 121 |

|   | A.1  | B-Tem   | plates Performing Neighborhood Logic OR        | 121 |

|   | A.2  | B-Ten   | plates Using Transient Mask                    | 122 |

|   | A.3  | B-Ten   | nplates Using Pattern Matching                 | 123 |

|   | A.4  | B-Tem   | plates Using Threshold Logic                   | 124 |

|   | A.5  | A-Ten   | nplates Computing with Propagating Wave        | 125 |

|   | A.6  | A-Ten   | plates with Positive and Negative Coefficients | 126 |

# **Symbols and Abbreviations**

| 1-D                | One dimensional                                              |

|--------------------|--------------------------------------------------------------|

| 3IS                | Three Island Structure                                       |

| ħ                  | reduced Planck's constant                                    |

| $\mu_n$            | mobility of electron                                         |

| $\mu_p$            | mobility of hole                                             |

| $\phi_F$           | floating gate potential                                      |

| τ                  | CNN cell time constant                                       |

| 8                  | arbitrarily small value (disturbance)                        |

| Α                  | CNN feedforward template                                     |

| $A_{k,l}$          | interconnection strength (weight); feedforward template term |

| AB                 | template matrix in binary programming scheme                 |

| $AB_{k,l}$         | interconnection strength (weight); binary template term      |

| В                  | CNN feedback template                                        |

| $B_{k,l}$          | interconnection strength (weight); feedback template term    |

| С                  | unit capacitance                                             |

| $C_{\overline{m}}$ | parasitic gate capacitance used as dynamic memories          |

| $C_C$              | parasitic gate capacitance used as dynamic memories          |

| $C_c$              | coupling capacitance                                         |

| $C_g$              | gate capacitance                                             |

| $C_{i,j}$          | CNN cell at $i^{th}$ row and $j^{th}$ column                 |

| $C_i$            | input coupling capacitance                          |

|------------------|-----------------------------------------------------|

| $C_L$            | load capacitance                                    |

| $C_m$            | parasitic gate capacitance used as dynamic memories |

| C <sub>sub</sub> | substrate capacitance                               |

| $C_S$            | parasitic gate capacitance used as dynamic memories |

| $C_T$            | tunnel capacitance                                  |

| $C_X$            | CNN state capacitor                                 |

| d                | thickness of the tunnel barrier                     |

| е                | electron (particle or charge)                       |

| $E_C$            | Coulomb energy                                      |

| $E_F$            | Fermi level energy                                  |

| $F_i$            | weighted input signal (synapse output)              |

| h                | Planck's constant                                   |

| Ibias            | bias current                                        |

| $I_d$            | drain current                                       |

| k <sub>B</sub>   | Boltzmann's constant                                |

| $L_n$            | length of channel of NMOS                           |

| $L_p$            | length of channel of PMOS                           |

| М                | number of rows in array                             |

| Ν                | number of columns in array                          |

| $N_r$            | Neighborhood of CNN cell                            |

| $R_Q$            | natural quantum unit of resistance                  |

| $R_T$            | tunnel resistance                                   |

| G                |                                                     |

- *S* threshold level for the activation function

- T temperature

- $u_{i,j}$  CNN cell input

| V <sub>DD</sub>    | supply voltage                          |

|--------------------|-----------------------------------------|

| V <sub>ds-th</sub> | threshold value of drain-source voltage |

| $V_{ds}$           | drain-source voltage                    |

| $V_g$              | gate voltage                            |

| V <sub>in</sub>    | input voltage                           |

| $V_i$              | input voltage                           |

| $V_m$              | comparator midpoint value               |

| V <sub>SS</sub>    | ground level voltage                    |

| $V_{th}$           | comparator (inverter) threshold voltage |

| $V_{Tn}$           | NMOS threshold voltage                  |

| $V_{Tp}$           | PMOS threshold voltage                  |

| $V_{w}$            | voltage representing weight value       |

| $V_X$              | voltage representing cell state         |

| $V_Y$              | voltage representing cell output        |

| W <sub>i</sub>     | weight value                            |

| $W_n$              | width of channel of NMOS                |

| $W_p$              | width of channel of PMOS                |

| $x_{i,j}$          | CNN cell state                          |

| $X_i$              | synapse input signal                    |

| Y                  | classified output signal                |

| Yi,j               | CNN cell output                         |

| z                  | CNN bias template                       |

| vMOS               | neuron MOS                              |

| A/D                | Analog-to-Digital                       |

| AER                | Address-Event Representation            |

| aka                | also known as                           |

|                    |                                         |

| ALU       | Arithmetic Logic Unit             |

|-----------|-----------------------------------|

| AND       | logic AND operation               |

| ANN       | Artificial Neural Network         |

| APE       | Analog Processing Element         |

| B/W       | Black and White                   |

| C-SET     | Capacitively coupled SET device   |

| C•RAM     | Computational RAM                 |

| CAM       | Content Addressable Memory        |

| CMOL      | CMOS/nanowire/MOLecular hybrid    |

| CMOS      | Complementary MOS                 |

| CNN       | Cellular Neural/Nonlinear Network |

| CNN-UM    | CNN Universal Machine             |

| CNT       | Carbon NanoTube                   |

| CNTFET    | Carbon NanoTube FET               |

| D/A       | Digital-to-Analog                 |

| DAC       | Digital-to-Analog Converter       |

| DC        | Direct Current                    |

| DRAM      | Dynamic RAM                       |

| DT-CNN    | Discrete-Time CNN                 |

| FET       | Field-Effect Transistor           |

| FG-MOSFET | Floating Gate MOSFET              |

| FSR       | Full Signal Range                 |

| GAPU      | Global Analogic Programming Unit  |

| GLU       | Global Logic Unit                 |

| HI        | logic high signal level           |

| I/O       | Input/Output                      |

|           |                                   |

| I/V    | current-to-voltage (converter)                      |

|--------|-----------------------------------------------------|

| IC     | Integrated Circuit                                  |

| IP     | Internet Protocol                                   |

| ITRS   | International Technology Roadmap for Semiconductors |

| L      | Length of a MOSFET channel                          |

| LLU    | Local Logic Unit                                    |

| LO     | logic low signal level                              |

| LWR    | Line Width Roughness                                |

| MDW    | Moving Domain Wall                                  |

| MIM    | Metal-Insulator-Metal                               |

| MOS    | Metal-Oxide-Semiconductor                           |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor   |

| MWCNT  | Multi-Wall Carbon NanoTube                          |

| N/A    | Not Available                                       |

| NAND   | logic NAND operation                                |

| NDR    | Negative Differential Resistance                    |

| NMOS   | MOSFET with N-type channel                          |

| NOR    | logic NOR operation                                 |

| NSIP   | Near-Sensor Image Processing                        |

| OR     | logic OR operation                                  |

| PE     | Processing Element                                  |

| PMOS   | MOSFET with P-type channel                          |

| PRHG   | Positive-Range High-Gain                            |

| PWL    | PieceWise Linear                                    |

| QCA    | Quantum Cellular Automata                           |

| QCIF   | Quarter Common Intermediate Format                  |

|        |                                                     |

| QD    | Quantum Dot                                 |

|-------|---------------------------------------------|

| R-SET | Resistively coupled SET device              |

| RAM   | Random Access Memory                        |

| RBC   | Random Background Charge                    |

| RC    | Resistor Capacitor                          |

| RIE   | Reactive Ion Etching                        |

| RTD   | Resonant Tunneling Diode                    |

| RTT   | Resonant Tunneling Transistor               |

| SCAMP | SIMD Current-mode Analogue Matrix Processor |

| SE    | South-East (direction)                      |

| SET   | Single-Electron Tunneling                   |

| SFB   | Self FeedBack                               |

| SIMD  | Single-Instruction Multiple-Data            |

| SOI   | Silicon On Insulator                        |

| SRAM  | Static RAM                                  |

| SW    | South-West (direction)                      |

| SWCNT | Single-Wall Carbon NanoTube                 |

| TLG   | Threshold Logic Gate                        |

| W     | Width of a MOSFET channel                   |

| W/L   | Width over Length                           |

| XOR   | logic eXclusive-OR operation                |

|       |                                             |

## Chapter 1

## Introduction

#### **1.1 Motivation**

For decades, the processing of information has been based on high precision computation. This approach has led to a development of digital processors with enormous computing power. However, a number of applications exist, in which the traditional strategy is insufficient. Especially in tasks of real-time image processing, e.g., vision systems, conventional computers are still far behind the neurobiological systems of living organisms. For instance, when a small insect flies, it performs an environment perception and navigation tasks among others. Such a complex computation is done at a fraction of time and power that would take with the advanced digital computer. Obviously, there is a huge gap in terms of the overall robustness, performance, and energy efficiency that engineers need to bridge. Through millions of years the evolution has developed and optimized the functionality and architectures of nervous systems. Therefore, a great lesson on the efficiency in complex computation can be learned from the nature. Studies of the physiological phenomena, on which biological receptors and nervous systems are based, reveal a substantial difference in conceptual and architectural approach to information processing between the systems developed by nature and engineers. In recent years, many endeavors to adapt the strategies known from neurobiology to the electronics have resulted in new theories and paradigms. Among them, the concept of cellular neural/nonlinear network (CNN) [1]-[3] is one to play a crucial role in the development of artificial vision systems [4]-[7].

The traditional information processing has largely been benefiting from a rapid progress in the semiconductor technology. For many years, a gain in computational power has been supported by the continuous down-scaling of CMOS technology. With smaller devices, higher chip densities and higher clock frequencies can be reached, yielding to more powerful processors. Even though the CMOS scaling limitation predicted in the past turned out not to be the ultimate boundary, there definitely are some physical limits beyond which no MOS device will be operational [8],[9]. Alternatively, the skyrocketing costs of fabrication will far exceed the performance improvements of scaled devices<sup>1</sup>. Since CMOS technology has already entered the nanometer scale, quantum effects are increasingly important and at some point will become the dominant phenomena. Therefore, they need to be investigated thoroughly. For the near future, techniques to prevent these effects from destroying the performance of a MOS device are sufficient. However, eventually designers will need ways of employing them instead of trying to avoid them. At a point where the rules of quantum physics become dominant, new devices will be required. Supposedly, such components will rely on different operation principles than MOS transistors, and therefore a new architectural approach will be needed as well. Classical digital designs are not suitable for devices and circuit blocks that lack the large gain, fan-in and fan-out, and worst of all are inherently unreliable. Moreover, traditional architectures become inefficient with scaling CMOS as well. Modern digital circuits as a whole scale down less than MOS transistors themselves due to the growing problem of interconnections. Longer and longer wires introduce larger parasitic components to the circuit. It is also increasingly difficult to route them efficiently. Moreover, the wire width is not scaling down as fast as the MOSFET channel length causing a new density bottleneck. Circuit speed is often limited by the RC delays of the connecting lines rather than by the device switching. This problem gets even worse with emerging nanostructures, due to their inherent low gain and driving capabilities. Hence, more and more attention is brought to the locally-interconnected array-architectures like CNN, which at given circumstances have multiple advantages over the traditional approach.

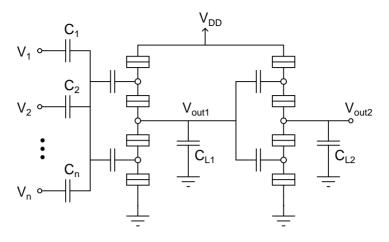

CNN theory allows to describe convolution-based local operations in a convenient way. It also stands for an architectural approach to realize a massively parallel processor. A computing array consists of (usually) identical and locally interconnected processing elements (PE) called cells. The state of a such cell has a nonlinear activation function and its evolution depends on the initial data, control terms and continuous-time spatio-temporal convolutions. The computing power of a CNN substantially depends on the array size. However, the implementation of a large array is a very challenging task. One of the possibilities to increase the cell density is to realize the gray-scale and black-and-white (B/W) image processing parts separately. Since the number of gray-scale operations used in many CNN applications is very limited and the majority of CNN algorithms contain many B/W image processing tasks, a full programmability seems to be needed only for the B/W processing part. Therefore, both

<sup>&</sup>lt;sup>1</sup>Currently, high fabrication costs concern the nanotechnology as well. However, the tergeted nanodevices should have much simpler structures than MOSFETs, and thus would allow the use of alternative cost-effective fabrication processes like, e.g., a self-assembly.

gray-scale and B/W processing cores can be significantly simplified [10]. Reducing the number of analog memories and analog weight multipliers potentially brings down the total chip area as well as power consumption and the time spent for processing (performing B/W operations with general-purpose gray-scale image processor takes much more time and energy). Moreover, such dedicated cores can reach a higher robustness. With a focus on the core for processing data in the form of binary images, a binary-programming scheme has been developed to enable a significant simplification of the coefficient circuits. As the number of analog transistors is minimized, the cell density grows. All elements of the template matrices are limited to binary values. Many operations can be performed with a single binary template. Some more complex tasks are computed as a consecutive evaluation of subtasks, and thus the processor remain versatile. Due to digital programming, the template terms can be loaded fast and the overall performance stays competitive. Moreover, this approach can provide the nanodevice-based implementations with fast and robust programmability. The realization of a binary-programmable CNN in single-electron tunneling (SET) technology, presented in this thesis as a proof of concept, can be a starting point for a future development of programmable architectures for nanotechnology integration.

#### **1.2 Research Contribution**

This thesis proposes a solution to the cell density limitations encountered in the design of CNN hardware. The separation of the gray-scale and the B/W image processing parts of a CNN system provides the means to optimize their implementations. With a focus on the structures for processing B/W images, the minimum programmability requirements, which preserve the cell versatility, have been studied resulting in the proposed binary programming scheme. Based on this approach, novel compact structures of a binary CNN have been developed for extremely dense implementations with CMOS, floating gate MOSFET (FG-MOSFET), and SET technologies. The proposed CMOS realization enables the cell densities previously thought to be impossible to obtain with CMOS technology. The CNN cell based on FG-MOSFET structure illustrates the method for applying the binary programming scheme to effectively control the networks with capacitive interconnections. Following this method, the SET implementation of a binary CNN cell is proposed, which to the best knowledge of the author is the first programmable SET CNN presented so far and one of the most versatile CNN realizations with nanodevices. It is due to the binary programming scheme that the nanostructures can be provided with fast and robust programmability. The material presented in this thesis can be used to assess and develop the programing schemes for architectures based on other emerging nanodevices as well.

The idea of binary programming scheme had been proposed by Prof. Ari Paasio,

and it was further developed by the author, Prof. Paasio, and Dr. Mika Laiho. Cells in all of the presented designs use the positive-range high-gain output-nonlinearity developed by Prof. Paasio. The author's main contribution was in transforming the traditional templates into binary form. The mathematical formulation of the templates and cell modeling was done by Dr. Laiho. The coefficient structures for CMOS implementation as well as the basic architecture concept of a cell were proposed by Prof. Paasio and further developed by the author. The simulations, layout drawing, and test measurements were performed by the author. Structures developed for implementations with FG-MOSFET and SET transistors result from the author's independent research carried out under the guidance of Dr. Laiho and supervision of Prof. Kari Halonen. A majority of the material included within this thesis has already been published or has been submitted for publication [11]-[20].

#### **1.3** Organization of the Thesis

The thesis consists of nine chapters. Chapter 2 introduces the basics of the CNN theory. Definitions and implementation oriented models are given. The importance of B/W image processing as a special subclass of CNN operations is emphasized.

Chapter 3 presents different approaches to the implementation of parallel imageprocessing. A selection of hardware realizations of array processors are described to give a view on the prior state-of-the-art.

The binary programming scheme is introduced in Chapter 4. The basic rules for designing the binary templates are given, and a selection of examples are used to form their classification.

Chapter 5 is focused on the CMOS implementation of a binary CNN. System architecture and functionality, cell circuit and operating principles are presented. A brief analysis of the robustness is given and a number of implementation issues are discussed. The measurement results of the fabricated chip are shown as well.

Chapter 6 briefly introduces the concept of the neuron MOSFET (vMOS) structure, i.e. the multi-input floating gate MOSFET (FG-MOSFET). Next, the FG-MOSFET implementation of a binary-programmable CNN is depicted. This design can be considered as a step toward a programmable CNN implementation with nanodevices. It allows for a conceptual development and tests of the capacitive couplings with ON/OFF programmability in the well known MOS technology. The designed cell structure is presented, and the simulation results of an  $8 \times 8$  network are shown.

Chapter 7 is dedicated to the binary CNN implemented with SET technology. First, the basic features of the SET technology are introduced. Then, basics of artificial neural networks (ANN) and prior state-of-the-art SET ANN designs are presented. Finally, a structure of a binary-programmable CNN cell designed for implementation

either with SET transistors only or as a SET-FET hybrid is depicted and simulation results are shown.

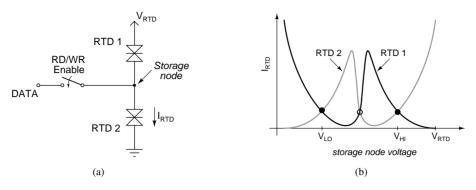

Chapter 8 constitutes a compact review of other promising nanodevice and architecture concepts. Resonant tunneling diode (RTD) as a computing device is described in more detail due to its higher degree of maturity. A number of other device concept are shown to give a broader view on this exciting research field. Additionally, the interesting idea of quantum cellular automata (QCA) as an alternative computing approach and CMOS-nanowire-MOLecular (CMOL) hybrid architecture, which combines the standard CMOS logic and the processing array built with nanodevices, are presented.

Finally, Chapter 9 concludes the thesis and gives some projections of what the further research could be focused on.

This page is intentionally left blank.

### Chapter 2

# Cellular Neural/Nonlinear Networks

The Cellular Neural/Nonlinear Network (CNN) theory [1] describes an analog parallel processing paradigm. Its hardware implementation is potentially capable of very high speed computation, while a low power consumption is maintained. A CNN can obtain this due to its massively parallel architecture. The interconnected processors, called cells, are arranged in a regular array. Each cell evaluates a global instruction on its own local data. Therefore, a CNN can be classified as a single-instruction multiple-data (SIMD) type processor. Such an operating mode is naturally suitable for image processing, where each cell corresponds to a pixel of an image.

#### 2.1 Definitions

A collection of basic definitions regarding the CNN are given in this section. However, some of these terms are general and can be used in describing other types of array processors as well.

#### 2.1.1 Neural vs. Nonlinear

The term "neural" is often used to describe the network behavior, which can mimic a biological nervous system, while the term "nonlinear network" has a more general meaning. However, the difference between the "neural" and the "nonlinear" network could also refer to how the interconnection weights are obtained. If the weights are defined by a learning algorithm (adaptation process) implemented within the system, we talk about a "cellular neural network". Otherwise, i.e. weights are programmed to the predefined values, it is a "cellular nonlinear network".

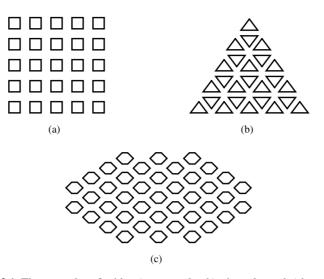

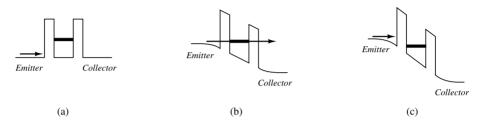

Figure 2.1 The examples of grids: a) rectangular, b) triangular and c) hexagonal.

#### 2.1.2 Grid Type and Array Dimension

The processing elements of CNN are locally interconnected and organized into oneor two-dimensional grid. Higher dimensions are theoretically possible but not suitable for integration. Usually, the cells form a regular rectangular array. However, that is not the only possible layout. Cells can also be arranged in other grids, such as hexagonal or triangular. These examples are shown in Figure 2.1. In this thesis, only the rectangular arrangement is used. To identify an individual cell within the  $M \times N$ sized array, a symbol  $C_{i,j}$  is used to denote a cell in the  $i^{th}$  row and  $j^{th}$  column;  $i \in [1, M]$ and  $j \in [1, N]$ .

#### 2.1.3 Neighborhood and Interconnection Types

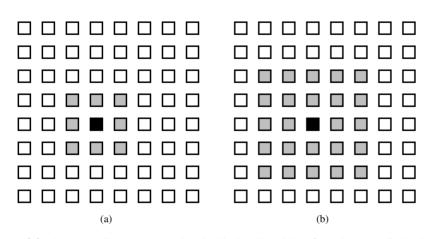

A cell within a CNN can have different types of neighborhoods and interconnections. The neighborhood of a cell defines the distance of the furthermost connections. Figure 2.2 presents examples of the 1- and 2-neighborhoods in a rectangular grid.

A cell is not necessarily connected to all of the neighboring cells. For instance, a cell in a rectangular grid can be 4- or 8-connected with the closest neighbors, as shown in Figure 2.3. Furthermore, an application may exist where only the cells at a certain distance within the neighborhood can be of interest. In case of a 3-neighborhood, a particular cell can interact with the cells at a distance of, say, 1 and 3 without dealing with the cells in between, i.e. at a distance of 2. An example of such a specific case can be found in Reference [21].

Figure 2.2 The gray cells are connected to the black cell, and thus form the a) 1-neighborhood, or b) 2-neighborhood.

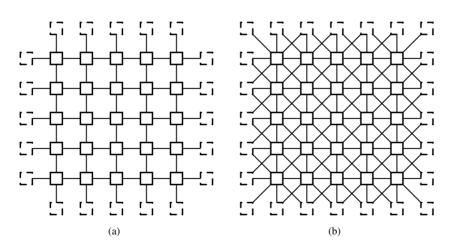

**Figure 2.3** The CNN cells arranged in the a) 4-connected and b) 8-connected 1-neighborhood. Dashed line indicates that a cell is a border cell.

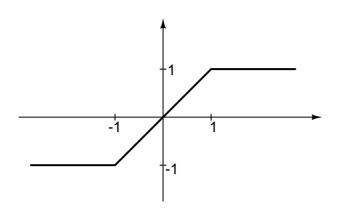

Figure 2.4 CNN cell output nonlinearity

#### 2.2 Continuous-Time CNN

Each cell in the array has a state and a constant input. The state of a cell is determined by the inputs and outputs of the directly connected neighborhood cells. All of these contribute to define the cell output. The standard CNN dynamics can be described with the state equation [1]

$$\frac{dx_{i,j}}{dt} = -x_{i,j} + \sum_{C_{k,l} \in N_r(i,j)} A(i,j;k,l) \cdot y_{k,l} + \sum_{C_{k,l} \in N_r(i,j)} B(i,j;k,l) \cdot u_{k,l} + z$$

(2.1)

where  $x_{i,j}$  is the cell state,  $u_{k,l}$  is the input and  $y_{k,l}$  is the output of each cell  $C_{k,l}$  within the neighborhood  $N_r(i, j)$  of the cell  $C_{i,j}$ . A and B are the feedback and feedforward templates, respectively. These templates are the collections of coefficient weights, which determine the strength of each interconnection between the cell  $C_{i,j}$  and its neighborhood. Finally, z determines the operating point of the cell and is called a bias template. The cell output has nonlinear activation function (relation between  $x_{i,j}$ and  $y_{i,j}$ ), usually in the form of piecewise linear (PWL) sigmoid as shown in Figure 2.4 and given by

$$y_{i,j} = f(x_{i,j}) = \frac{1}{2}(|x_{i,j} + 1| - |x_{i,j} - 1|).$$

(2.2)

If the feedback and feedforward templates have coefficients set identical for each cell regardless of its position in the network, the templates are space invariant. In such a case, assuming the 1-neighborhood, these templates take the form of

$$A = \begin{bmatrix} A_{-1,-1} & A_{0,-1} & A_{1,-1} \\ A_{-1,0} & A_{0,0} & A_{1,0} \\ A_{-1,1} & A_{0,1} & A_{1,1} \end{bmatrix} \quad B = \begin{bmatrix} B_{-1,-1} & B_{0,-1} & B_{1,-1} \\ B_{-1,0} & B_{0,0} & B_{1,0} \\ B_{-1,1} & B_{0,1} & B_{1,1} \end{bmatrix} \quad z.$$

(2.3)

So, only 19 terms are required. An operation performed by a CNN is determined by programming these terms. The matrices A and B are called "cloning templates" and z is called bias template or threshold. The center element of the cloning template matrix represents a self-feedback term. A number of CNN templates with the names describing the corresponding network-operation have already been proposed [22].

#### 2.3 CNN Model Modifications

#### 2.3.1 CNN Universal Machine

The original CNN has been supplemented by a number of additional functionalities resulting in the CNN Universal Machine (CNN-UM) [23]. The set of cells' new features include Boolean logic, control logic, and memories (both analog and digital). Moreover, the global analogic programming unit (GAPU) comprising program registers, configuration registers, etc. has been added to the system. These extensions enable algorithmic operations consisting of several templates and logic operations.

#### 2.3.2 Full Signal Range CNN

Even though the CNN theory is a powerful tool for many applications operating on images, its realization on silicon is a challenging task. Therefore, designers have proposed some implementation-oriented simplifications, e.g., the full signal range (FSR) model [24], which truncates the cell state between two saturation values: -1 and 1. In this way, the cell state and cell output become equivalent. The employment of the FSR model has led to the realization of a CNN-UM with  $128 \times 128$  cells [6].

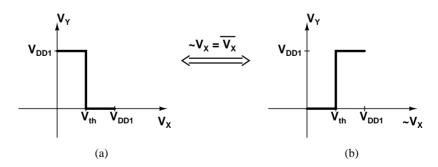

#### 2.3.3 Positive-Range High-Gain CNN

Positive-range high-gain CNN [25], [26] is another interesting simplification of the original CNN model. The output nonlinearity is modified to

$$y_{i,j}(t) = f(x_{i,j}(t)) = \begin{cases} 0, & x_{i,j}(t) < -\varepsilon \\ 1, & x_{i,j}(t) > \varepsilon \end{cases}, \quad 0 < \varepsilon \ll 1,$$

(2.4)

resulting in a step function. The cell input and output (I/O) become binary, while the template terms remain continuously valued. As a consequence of the analog design being simplified, yielding a more compact layout and improved reliability, gray-scale operations are no longer possible with binary I/O. Therefore, a part of the functionality of the network is lost.

#### 2.3.4 Discrete-Time CNN

A Discrete-Time CNN (DT-CNN) [27] has continuously valued inputs and weights while its output is bipolar. It can be realized with either analog or digital implementation. In a digital DT-CNN the state can be updated through a variety of digital integration methods.

#### 2.3.5 Binary CNN

The general purpose approach to CNN implementation, which combines the capability of processing both black and white (B/W) and gray-scale images, is easy to model with the CNN theory, but challenging to realize. The large number of in-cell multipliers extorts a large cell size. Moreover, the coefficient circuits are scaled for a precision required in analog computation, and thus their power consumption and speed are not optimized for processing binary images. An alternative approach is to separate the B/W and the gray-scale processing parts and optimize their implementations.

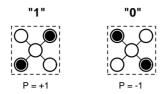

Binary CNN takes a B/W image as an input and yields a B/W result. The B/W data processing is an important class of CNN operations covering a wide range of applications [22]. In fact, most of the proposed templates handle mainly binary data. It is also an integral part of many algorithms based on sequential execution of templates and Boolean logic functions.

A CNN implementation dedicated for B/W image processing can benefit from the programmability of template terms reduced to binary values  $\{0,1\}$ . The coefficient circuits, thus cell structure, can be significantly simplified resulting in a very compact layout. Additionally, the power dissipation is significantly reduced. The limitation of the network functionality due to one-bit programmable template terms is not severe. More complex templates can be split into sequentially executed simple subtasks and the processor remains versatile. Moreover, since the weights are binary values, the reprogramming can be very fast and robust. Therefore, the overall performance can be competitive. An array with an extremely high spatial resolution can be implemented on a single chip for low-power, high frame-rate applications.

### **Chapter 3**

# Hardware Realizations of Array Processors

This chapter presents a selection of the state-of-the-art hardware realizations of array processors. These chips are described to broaden the view on this research field as well as to give a context in the discussion of motivation for the approach proposed later in this thesis.

#### **3.1 ACE Series Processors**

The appealing features of the CNN paradigm [1]-[3] have served as a driving force in forming an active research field of CNN hardware realizations. Despite years of development, the CNN hardware design remains challenging, and alternative approaches are considered. The series of  $ACE^1$  processors [4]-[6] is an attempt to efficiently implement a network that would resemble the CNN model. The largest and the most advanced processor in this series, codenamed ACE16k, is a hardware realization of a CNN-UM with 128 × 128 cells. It combines image acquisition with processing capabilities. In addition, versatile programming makes ACE16k an attempt to obtain a vision system on a chip [6]. Each cell in the array incorporates a reconfigurable optical input module, in which the user can select among two types of photodiodes and a phototransistor. Moreover, either a normal linear integration or a logarithmic compression sensing mode can be used. In addition to an optical sensor, each processing element (PE) includes:

• a local analog memory (LAM) with a capacity for 8 gray-scale pixel values with an 8-bit resolution,

<sup>&</sup>lt;sup>1</sup>ACE is the name of a family of CNN chips.

- a local logic unit (LLU) consisting of a programmable two-input one-output logic operator,

- a resistive grid module that allows for continuous-time diffusion in a resistivegrid like manner,

- an address event downloading module to simplify the information extraction from B/W images (instead of images, the addresses of active array locations are provided<sup>2</sup>),

- a configurable bank of analog multipliers and adders for interaction with other cells in the neighborhood,

- local masks for conditional execution of certain operations upon a locally defined value.

The analog core (array) is complemented by 128 A/D and 128 D/A data converters (one of each per array column), instructions memory, a memory for convolution masks and references with 24 digital-to-analog converters (DACs), and control circuits.

ACE16k is a general purpose SIMD-type processor that can operate on binary and gray-scale data. Despite the fact that only local cell interconnections are available, operations with a larger region of influence can be computed by means of the asynchronous information propagation.

#### 3.2 Near-Sensor Image Processing

Another very interesting approach to realizing array-type image processors is the concept of near-sensor image processing (NSIP) [29]-[31]. Unlike the ACE chips, the NSIP implementation does not try to realize any predefined mathematical model. Instead, the functionality of a PE is based on functional and hardware-oriented requirements. Since a clear contradiction exists between the PE complexity and a high spatial resolution, a combination of a nondestructive photodiode readout and a binary image processing is proposed as a tradeoff solution. The proposed structure can perform local and global binary operations. Local operations include Boolean logic functions as well as interactions with the four nearest neighbors (towards principal compass points). Global operations (e.g., threshold, smallest circumscribing rectangle, selecting one of many objects) are handled by a global logic unit (GLU), which provides the asynchronous propagation of binary data over the array and thus working in parallel on the entire image. Due to a nondestructive sensor readout, the processor can also perform

<sup>&</sup>lt;sup>2</sup>Event-based communication is becoming increasingly important. A recent example is the address-event representation (AER) protocol that has been developed for efficient communication in multichip neuromorphic systems [28].

a number of simple gray-scale operations by, for example, comparing in time the evolution of sensor outputs at different pixel locations. However, the results are always binary. Since the gray-scale values are coded as bit sequences in time, more complex gray-scale operations require an algorithm with extensive number of steps or even become impossible to perform. Additionally, a limited amount of in-cell memories restricts the array programmability, but NSIP can be considered as an image processor for certain simple applications.

#### 3.3 SIMD Current-mode Analogue Matrix Processor

The SIMD Current-mode Analogue Matrix Processor (SCAMP) series is a very interesting example of realizing a general-purpose vision chip [32]-[34]. The implementation consists of an array of cells combining an image sensor with processing capabilities for analog operations. Each cell, called analog processing element (APE), contains a photodetector, a comparator with activity-flag latch, nine registers (eight general-purpose ones and one used for exchanging data with the nearest neighbors), and I/O circuits. The photodetector circuit uses an n-type diffusion diode and can operate in either linear integration mode or in continuous-time log-compression mode. The registers are designed using switched-current technique (compact memory cells). In this way, an additional dedicated circuitry such as arithmetic logic unit (ALU) is not needed to perform the arithmetic operations. Instead, the basic operations (inversion, addition, division, etc.) are executed in the registers and analog bus. Each register can store a gray-scale pixel value or a variable with 7 bits of accuracy. The local I/O register allows for data exchange with only one neighboring APE at a time. Moreover, connections are possible towards cardinal directions only. Therefore, examining the pixel values of multiple neighbors requires a time-domain multiplexing. As the computing speed is traded for silicon area, a very compact APE and arrays with reasonably high spatial resolutions can be achieved. However, operations relying on the asynchronous propagation of information throughout the array are no longer possible. To overcome this limitation, a new architecture for cellular image processor has recently been proposed, which allows for both synchronous and asynchronous operation modes [35]. Additionally, the SCAMP chip is equipped with simple and robust digital control/programming.

An interesting feature of SCAMP chips is the flexible global readout architecture [36] designed to enhance global communication and data extraction. The addressing is extended by the capability of having *don't care* bits in the address word. Therefore, a number of rows/columns in the array can be addressed simultaneously. This enables addressing groups of APEs in the array (block section of an image or periodic pixel-locations) in addition to single APE and entire array selections. Such a flexible

readout is useful in performing certain global operations. For instance in the binary readout mode, a logic OR can be computed on the selected group. In the analog readout mode, a global summation is performed. Moreover, this addressing scheme allows for calculating global image descriptors (pixel counts, histograms, etc.), object coordinate extraction, multiresolution image processing, and control of iterative procedures. It can be also used together with a global input, e.g., to replace a local value in selected APEs with a global one.

#### 3.4 Digital SIMD Processor

An image processor performing a single instruction on multiple data can also be realized with digital circuits only. The implementation proposed in references [37] and [38] has an array of  $64 \times 64$  processing elements, column adders as well as column and row shift registers. Each PE in the array occupies  $67.4 \times 67.4 \,\mu\text{m}^2$  on a 0.35  $\mu\text{m}$ CMOS process. The vision system is completed by an off-chip real-time controller and a DAC. Each PE consists of a photodetector with readout circuit, a bit-wise local RAM and a bit-serial ALU composed of a full adder combined with I/O multiplexers and carry register. The ALU has two binary inputs and executes a logical or arithmetic operation. Different types of image processing tasks can be performed as a sequence of such single-bit operations. The PE can also act as an analog-to-digital converter (ADC), which utilizes a software-controlled conversion of pixel illumination to digital pixel values. Additionally, each PE can communicate with its four neighbors at cardinal directions for spatial image processing.

Interestingly, by keeping the output latches transparent, adjacent PEs can be joined into blocks and treated as a single logic circuit. Each PE in such a block has two functions. It can be used as a pixel of an image or as a bit in a word, which provides effective memory use. The PE-joining feature enables the obtained blocks to execute global cumulative operations such as global summation and global OR, or multi-bit addition. This architecture can also emulate the column-parallel processor by chaining PEs in columns. Moreover, self-generated PE chains are possible based on the results from image processing.

#### 3.5 Binary I/O CNN-UM

An alternative approach to the hardware realization of a CNN-UM has been proposed [25], in which the cells are based on the positive-range high-gain (PRHG) CNN model. A revised version of this design resulted in a standardized QCIF resolution ( $176 \times 144$  cells) CNN-UM for very low bit-rate video coding systems [39]. An algorithm for

such applications of CNN has been proposed in [40]. The observation that a dominant portion of this algorithm relies on manipulating B/W images explains the design focus on the B/W image processing part. Additional motivation comes from the fact that some of the required gray-scale operations are not implemented in any CNN hardware so far, and thus a separate design dedicated for such operations is assumed. In this approach, each PE consists of:

- a comparator in form of a CMOS inverter to realize the cell output nonlinearity,

- synapse multipliers (fully-connected first-order neighborhood) based on a threetransistors structure (one for each positive and negative coefficient, plus a control switch),

- four local memories for storing intermediate results (the number is due to the algorithm of [40]),

- a memory controlling unit, which provides a cell-level buffer for global OR operation, memory I/O control as well as refreshing or inverting the memory content,

- programmable local logic structure,

- a cell I/O circuit with buffer and a number of control switches.

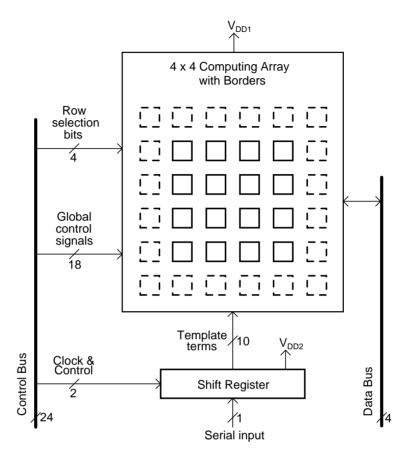

In addition to the QCIF-sized processing array, the chip contains a ring of constant border cells, DACs, a block of I/O buffers for driving the pads, row selection unit for addressing purposes, and a global OR evaluation block. While the PRHG CNN model limits the cell state to a single-bit value, the template coefficients remain analog with 6-bit programmability (5 magnitude bits and the sign) and the bias term is controlled with 9 bits. To increase the speed and reliability these analog values are generated by the on-chip DACs. The converters comprise a 6-bit coefficient memory (9 bits for bias term), binary weighted current sources, current steering switches, I/V converters for P- and N-type device in synapse, and buffers (over 25000 transistor gates load each voltage-line). The block of I/O buffers incorporate multiplexing of the 16-bit incoming data to a 176-bit wide image row for writing the initial values to the array.

Unlike the SCAMP or ACE16k chip, this implementation is not a general purpose image processor due to the lack of capabilities for gray-scale data processing. Neither, it belongs to the class of vision systems as the cell design does not incorporate any optical sensor. However, this limited functionality and novel design techniques allowed to increase the cell density to over 3000 cells/mm<sup>2</sup>, a significant step towards arrays with a large spatial resolution.

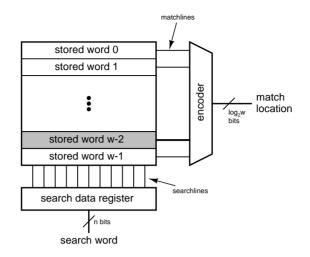

Figure 3.1 Conceptual view of a content-addressable memory containing w words. Shaded box indicates the location (w - 2) with data matching the search word [41].

#### 3.6 Memory-based Approaches to Parallel Processing

This section presents two very interesting methods of exploiting the regular structure of a memory for implementation of parallel data processing – the content addressable memory and the computational RAM. Although, they are not directly related to the CNN paradigm, they offer properties (parallel search/write, bit-serial processing) that might be considered as useful extensions of the CNN functionality.

#### 3.6.1 Content Addressable Memory

Content addressable memory (CAM) [41] can be regarded as a hardware search engine that can be much faster than algorithmic approaches for search-intensive applications. It is composed of a conventional memory (usually SRAM) with added comparison circuitry that enable performing a complete search operation in a single clock cycle, as shown in Figure 3.1. The search operation takes a data word as input and returns the address to a memory location containing the matching data. In case of multiple hits, the priority encoder selects the highest priority matching location.

The primary commercial application of CAMs is to classify and forward Internet protocol (IP) packets in network routers. However, if a CAM architecture is complemented with a parallel write function, it becomes a promising candidate for a compact hardware realization of a highly parallel image processing system with high data throughput. An example of such a processor is presented in [42]. The system consists of a chip controller and 32 CAM blocks, each with 512 words. The adjacent blocks are connected by an 8-bit horizontal bus and 1-bit vertical bus. Since these buses are also

Figure 3.2 Integration of PEs within a basic DRAM structure [43].

distributed outside the chip, a larger CAM array can be obtained by using several chips. This processor can handle  $128 \times 128$  pixels in parallel, and perform two-dimensional SIMD-type processing including global data operations. Various advanced functions such as bidirectional hit-flag shift, block read/write, and hit-flag counting are implemented in the chip.

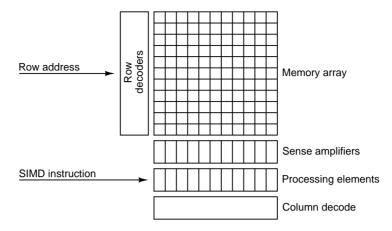

#### 3.6.2 Computational RAM

The computational RAM (C•RAM) architecture [43] is an attempt to implement processing elements within a memory chip. The motivation comes from the appealing idea of utilizing the very high internal bandwidth of a memory. This can be achieved only through a tight integration of logic and memory. For example, a pitch-matched PE can be placed at each column of a memory, as shown in Figure 3.2. In this way, the capabilities of a conventional DRAM chip are extended to the functionality of a SIMD-type processor with distributed, nonshared and uniformly addressed memory. It is worth noting that this extension can be obtained at the cost of only slightly increased area and power consumption.

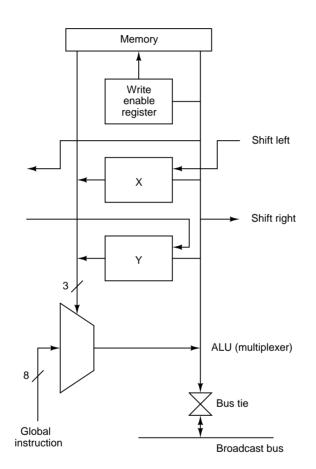

Figure 3.3 presents the structure of a C•RAM processing element which supports bit-serial computation. It consists of an ALU based on an 8-to-1 multiplexer, and three registers. The ALU can perform a Boolean operation of three inputs coming from X and Y registers and memory. The result can be written back to either the memory or the X, Y or write-enable register. The X and Y registers can also act as destinations for left and right shift operations, providing the means for communication with neighboring PEs. The write-enable register is used for conditional writing to the memory. The bidirectional bus transceiver drives or receives from the broadcasting bus. During communication operations, the ALU is used to route signals.

Figure 3.3 A simple processing unit for C•RAM implementation [43].

The C•RAM chips can be applied in fields of e.g., image processing, computer graphics, databases or even a real-time video-processing [44], [45]. However, this architecture does not allow for pixel-parallel computation since only one PE per memory column and not per memory cell (pixel) is available.

This page is intentionally left blank.

## Chapter 4

# **Binary Programming Scheme**

In this chapter, a new approach to control the function performed by a CNN – the binary programming scheme is described. With minimum hardware requirements, this scheme provides a processor with sufficient versatility to perform all black-and-white (B/W) operations proposed so far. The basic cell model is presented and template robustness issues are discussed. Based on the properties, the templates are classified into groups and the guidelines for template design are presented. The library of binary templates is given in Appendix A. This chapter is based on Reference [20]. However, the model cell structure described here differs somewhat from the version proposed in [20], as to keep a better correspondence with the implementations presented in the following chapters. Examples of template processing with images used in simulations as well as the analysis of memory usage in template evaluation can be found in [14], [20].

## 4.1 Motivation

The hardware realization of a cellular nonlinear network (CNN) can significantly benefit from the separation of B/W and gray-scale image processing parts as it allows for their optimization. In turn, the areal density, power consumption, and/or speed of operation can be improved. A great example of such optimization is the positive-range high-gain CNN dedicated for processing B/W data [25], [26]. In this model, the output nonlinearity takes the form of a threshold function resulting in binary cell output. However, the coupling weights remain analog, i.e. real numbers (positive and/or negative). It is a real challenge to perform fast programming of analog weights since their values need to be accurately settled before use. The coefficient circuits are seen as large capacitive loads attached to the weight lines, and thus slow down the programming due to RC delays. Reference [10] proposed that the multiplier coefficients are reduced to binary values as well. In this way, the coefficient circuits, and thus the cell structure, can be further simplified, resulting in a very compact layout. That enables a single chip implementation of an array with extremely high spatial resolution. At the same time, a very fast reprogramming of the weights comes as a consequence of toggling the bit lines with minimum load capacitance.

## 4.2 Introduction

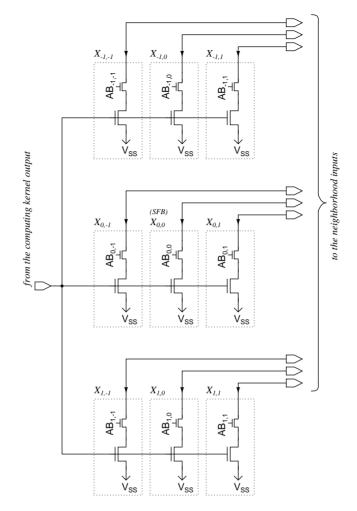

It is an interesting observation that most templates handling B/W images can be modified so that all of the terms are 1-bit values. The more-complex templates, which cannot be directly transformed into one binary template, need to be divided into a set of 2 or 3 subtasks (binary templates) run successively. Such a division can be done by, e.g. separating the positive template terms from the negative ones. The result of each subtask is either used as an initial state for the following one or it is stored in a local memory of a cell to be later combined with others (by means of Boolean logic operations) into the final result. In this programming scheme, also the threshold value is programmed digitally with 2 bits. Interestingly, in the binary programming scheme there is no need for a separate control matrix B and a feedback matrix A as in a classical CNN template. They are replaced with just one template matrix AB, which contains the elements of either A or B template matrix depending on the type of operation. Selecting the type of operation is done with a dedicated global control signal. Therefore, programming the template becomes as simple as loading 12 bits (9 for template terms, 2 for bias, and 1 for choosing the type of template). Obviously, toggling the digital lines can be fast (in the order of a few nanoseconds) and leads to competitive evaluation times of the multiple template algorithms.

### 4.3 Cell Model

#### 4.3.1 Model Definitions

In the presented model,  $x_{i,j}$  denotes the state of a cell in the  $i^{th}$  row and  $j^{th}$  column of an  $M \times N$  array ( $i \in [1, M]$ ,  $j \in [1, N]$ ) and is determined as follows:

$$\begin{array}{rcl} x_{i,j}(t) &=& y_{i,j}(0) & \text{if} \quad e_{i,j} + M_{-}E = 2 \\ x_{i,j}(t) &=& \overline{y_{i,j}(0)} & \text{if} \quad e_{i,j} + IM_{-}E = 2 \\ C_X \cdot dx_{i,j}(t)/dt &=& \sum_{k,l} [AB_{k,l} \cdot yu_{i,j;k,l}(t)] - z \quad \text{else} \end{array}$$

(4.1)

where  $k \in [-1, 1]$ ,  $l \in [-1, 1]$ ,  $y_{i,j}(0)$  is the initial cell output  $(\overline{y_{i,j}(0)}$  is its inverse),  $e_{i,j}$  is a transient-mask control-value, and  $C_X$  is a state capacitance. The variables  $M_-E$  and  $IM_-E$  control (enable) the normal and the inverted mask operation. They have

binary values and only one of them can be active at a time  $(M_{-}E + IM_{-}E \le 1)$ . For  $(M_{-}E + IM_{-}E) \cdot e_{i,j} = 1$ , the transient mask is active and the cell state is forced to the initial cell output  $y_{i,j}(0)$  or its inverse  $\overline{y_{i,j}(0)}$ . Otherwise, the transient mask is inactive and the cell state evaluates. The inverted mask operations are not available when processing an A-template. The term  $y_{u_{i,j};k,l}(t)$  is the neighborhood contribution defined as

$$yu_{i,j}(t) = u_{i,j} \quad \text{if} \quad A_{-}B = 0 yu_{i,j}(t) = y_{i,j}(t) \quad \text{if} \quad A_{-}B = 1$$

(4.2)

where  $A_B$  is a binary value controlling the template type selection. For  $A_B = 1$  an A-template and for  $A_B = 0$  a B-template is being processed. The term  $u_{i,j}$  is the cell input loaded before a B-template is selected with  $A_B$ . Upon  $A_B$ , terms  $AB_{k,l}$  are elements of either a feedback matrix A or a control matrix B. The coefficients  $AB_{k,l}$  can be independently programmed to be either 0 or 1. The negative bias term z defines the threshold of comparison and can be set to four different values: 0.5, 1.5, 2.5 and 3.5. It should be noticed that this bias programmability is sufficient, since any operation requiring threshold larger than 3.5 can be performed with inverted images. The cell model uses a unity step function as the output nonlinearity, and the relationship between the state and output takes the form

$$y_{i,j}(t) = f(x_{i,j}(t)) = \begin{cases} 0, & x_{i,j}(t) < V_m - \varepsilon \\ 1, & x_{i,j}(t) > V_m + \varepsilon \end{cases}, \ 0 < \varepsilon \ll 1$$

(4.3)

where  $\varepsilon$  represents an arbitrarily small disturbance, and  $V_m$  is a comparator midpoint value. The introduction of  $V_m$  (for comparison, see Equation (2.4)) makes the model more universal and at the same time more accurate for hardware realizations, since usually  $V_m \neq 0$  unless complementary supply voltages are used in the cell circuit.

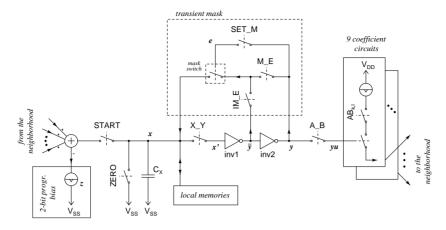

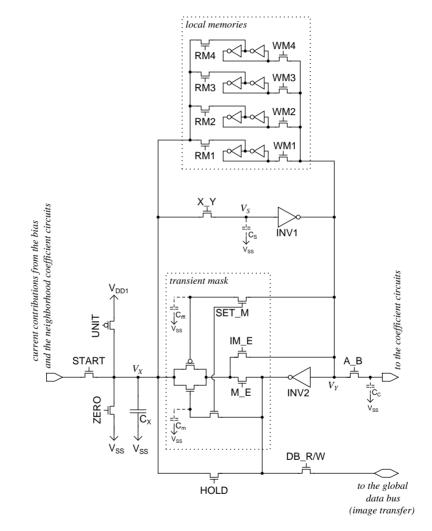

#### 4.3.2 Basic Cell Structure

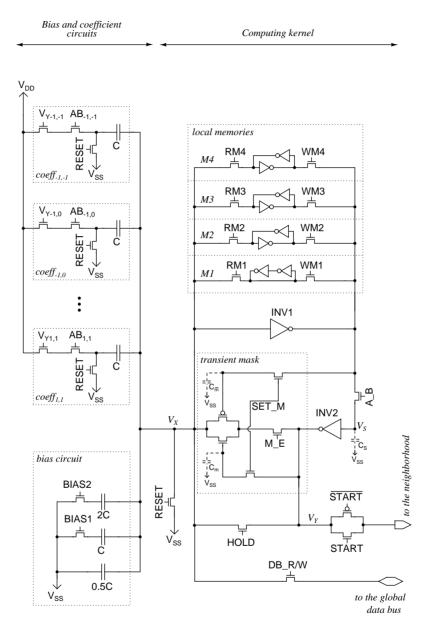

The concept cell structure implementing the proposed model is sketched in Figure 4.1. It is just one of many possible realizations. As in most CNN hardware designs, cells interact with each other using currents. Such a technique is very suitable for a CMOS implementation. However, the cell model allows for alternative approaches that would fit best a specific technology and/or application.

The presented cell structure consists of a programmable negative bias, a state capacitance, and a pair of cascaded inverters working as a comparator and providing the desired output nonlinearity. The structure also includes local memories, 9 coefficient circuits and a number of switches partially grouped in a transient mask block. The switches in the figure are drawn in a position for unset control signal (logic LO). Additionally, it is assumed that nodes marked as x, x', e, and yu can be utilized as dynamic

**Figure 4.1** Cell structure implementing functionality required for binary programming scheme. For clarity, the I/O parts (image acquisition, data transfer) are omitted as implementation/application specific and irrelevant to the programmability model description.

memories. The values of x', e, and yu are stored using parasitic capacitances.

The signal *START* is used to initiate the template evaluation by connecting the neighborhood contribution and the negative bias to the cell input. The control signal *ZERO* sets the cell state to LO. The signal *SET\_M* is used to program the transient mask by writing *y* to *e*. The control signal  $X_Y$  enables the nodes x' and *y* to follow the cell state *x*. For inverted mask operations this signal is unset. When the mask is active the cell state is forced to the value stored at the node x', i.e. y(0) because the inverters *inv*1 and *inv*2 are strong enough to override the contribution from neighborhood and bias. All other signals reflect exactly the corresponding variables described in the previous section.

## 4.4 Template Robustness