N. Chekurov, M. Koskenvuori, V.-M. Airaksinen, and I. Tittonen, Atomic layer deposition enhanced rapid dry fabrication of micromechanical devices with cryogenic deep reactive ion etching, Journal of Micromechanics and Microengineering, 17, pp. 1731-1736 (2007).

© 2007 Institute of Physics Publishing

Reprinted with permission.

http://www.iop.org/journals/jmm http://stacks.iop.org/jmm/17/1731

# Atomic layer deposition enhanced rapid dry fabrication of micromechanical devices with cryogenic deep reactive ion etching

N Chekurov $^{1,3}$ , M Koskenvuori $^{1,3}$ , V-M Airaksinen $^{2,3}$  and I Tittonen $^{1,3}$

- <sup>1</sup> Micro and Nanosciences Laboratory, Micronova, Helsinki University of Technology, Espoo, Finland

- <sup>2</sup> Micro and Nanofabrication Centre MINFAB, Micronova, Helsinki University of Technology, Espoo, Finland

- <sup>3</sup> Center for New Materials, Helsinki University of Technology, Espoo, Finland

E-mail: nikolai.chekurov@tkk.fi, mika.koskenvuori@tkk.fi, veli-matti.airaksinen@tkk.fi and ilkka.tittonen@tkk.fi

Received 28 May 2007 Published 30 July 2007 Online at stacks.iop.org/JMM/17/1731

## Abstract

A fast, dry microfabrication process combining atomic layer deposition, electron beam lithography and cryogenic deep reactive ion etching is presented. The process exploits the extremely high selectivity of atomic layer deposited amorphous Al<sub>2</sub>O<sub>3</sub> (alumina) to silicon in cryogenic etching by using an ultra-thin ( $t \leq 5$  nm) Al<sub>2</sub>O<sub>3</sub> film as a mask. The process rules and limitations are carefully analyzed and a thorough understanding of the limiting factors is reached, and the effect of the limitations on the critical output current of a dc-biased clamped–clamped beam is studied. To test the process, multiresonant tuning fork resonators are fabricated and found to exhibit  $Q \approx 8000$  at  $f_r \approx 11.4$  MHz. Both values are the highest reported for resonators fabricated with the dry process and comparable with values achieved with existing silicon micromachining processes.

(Some figures in this article are in colour only in the electronic version)

### 1. Introduction

Usually MEMS fabrication aims for mass production producing a large number of components simultaneously, but at the cost of a longer lead-in time to start the batch fabrication. For industrial scale production this is reasonable but for research purposes where small batches of devices are needed in short time scales, this is far from optimum. For capacitive, bulk micromachined devices, the time consumption comes typically from the fabrication of contact masks prior to the device fabrication and the need to use different instruments for different etching processes: dry etching for the device and coupling gap formation, and wet etching for the release of moving parts. One important application area for capacitive

MEMS is in the RF-signal processing, where high-frequency resonators are projected to replace conventional electronics for various tasks [1].

High-frequency resonators are typically from a few to a few tens of micrometers in size and define resonance frequencies that are from a few to hundreds of MHz. For operation, the devices are often actuated by electrostatic forces over a narrow air gap. To reach a proper coupling and practically realizable impedance matching, the coupling gaps should preferentially be in the range of  $100 \le d \le 1000$  nm in width. The fabrication of such devices requires a reproducible release etch which is a critical step in all wet fabrication methods. In the following we investigate a dry fabrication sequence that features atomic layer deposited (ALD) thin films

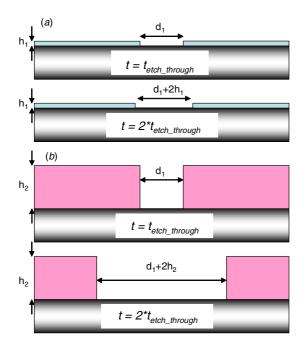

**Figure 1.** Due to the ultra-thin layers used, the etching of the openings to the mask layer is very tolerant to over-etching. (a) For thin layers (the thickness of the mask is much smaller than the smallest dimensions to be fabricated, i.e.  $h_1 \ll d_1$ ) even when the etching time is doubled, the opening is widened very little when compared with (b) where the thickness of the masking layer is in the order of the smallest fabricated dimension, i.e.  $h_2 \approx d_1$ .

as a hard mask, and cryogenic inductively coupled plasma (cryo-ICP) as etchant in the patterning and release of MEMS devices. The sequence is especially suitable for research purposes. (i) With this process it is possible to design and fabricate a small number of released structures in a time scale of only a few hours. (ii) No thick masking layers are necessary; therefore small enough features can be fabricated.

The extremely high selectivity of Al<sub>2</sub>O<sub>3</sub> (alumina) to silicon (1:70 000) in cryogenic (T < -110 °C) etching [2] makes Al<sub>2</sub>O<sub>3</sub> an excellent hard mask for deep reactive ion etching (DRIE). With selectivity this high, a mask only a few angstroms thick ( $t \le 0.3 \text{ nm}$ ) is required for etching a thickness, h, which is defined by the processed structure (typically 1  $\mu$ m  $\leq h \leq 20 \mu$ m). However, due to the nature of the atomic layer deposition technique, a minimum of ten deposition cycles ( $t_{ox} \ge 0.9 \text{ nm}$ ) are needed in order to grow pin-hole-free and mechanically strong films [2]. The minimum thickness of the film can also be affected by the undercutting of the mask [2]. Especially with the increased etching times, despite the anisotropic etching process, the silicon directly underneath the oxide will be etched and if too thin films are applied as masks, this could lead to the deterioration of the mask. Thus, the minimum thickness of ALD grown masks is a few nanometers.

As the mask thickness ( $t_{ox} \le 5$  nm) is very small compared to the smallest desired feature size (d) the hard mask etching becomes a non-critical step; even a significant over-etching causes at most only a few nanometer broadening of the gaps (figure 1). In addition, the removal of this thin hard mask layer may not be necessary at all.

The cryo-DRIE (cryogenic deep reactive ion etching) [3] gives the possibility of taking advantage of the high selectivity of alumina to silicon in deep silicon etching. In contrast, previously reported dry fabrication processes have utilized the Bosch process [4] and thick photoresist as a mask for silicon and release etching. In this way accelerometers [5], resonators with eigenfrequencies in the kHz range [6, 7] and switching devices [8] have been fabricated.

In the following a fast dry fabrication process for released MEMS devices with narrow capacitive coupling gaps is presented. The purpose of this paper is to show that besides using a thick photoresist and the Bosch ICP with protective polymer layers for the etching of silicon, the dry fabrication process utilizing atomic layer deposited (ALD) ultra-thin aluminum oxide (Al $_2$ O $_3$ ) masking and cryo-DRIE for etching of the vertical coupling gaps and for the final release of devices can be used. Another novel contribution is the analysis of different non-idealities due to the dry release etch. This study is concluded by analyzing the maximum current attainable from a clamped–clamped beam resonator used in frequency reference application.

# 2. Al<sub>2</sub>O<sub>3</sub> deposition

The deposition of the thin alumina mask was done with Beneq TSF-500 ALD-reactor with trimethyl aluminum (TMA) as a metal precursor and water as the oxygen precursor. The ALD process consists of identical cycles of deposition, each cycle consisting of consecutive pulses of both precursors with a nitrogen purging pulse after each precursor. As a result, one monolayer of the material is deposited during each cycle. In practice, at the beginning of the process, the film growth is highly nonlinear and can result in separate islands rather than continuous layers during the first few cycles [9, 10], but it has been shown that the layers are continuous already after 10-15 cycles [2, 10]. In this work, the cycle time used was 2.0 s and the rate of the growth was measured to be 0.88 Å/cycle at the deposition temperature of T = 220 °C. The mask was deposited on a planar wafer, but due to the conformal nature of the ALD deposition, even more complex and non-planar structures fabricated beforehand on the wafer could be protected from the DRIE with an Al<sub>2</sub>O<sub>3</sub> film.

# 3. Fabrication process and design rules

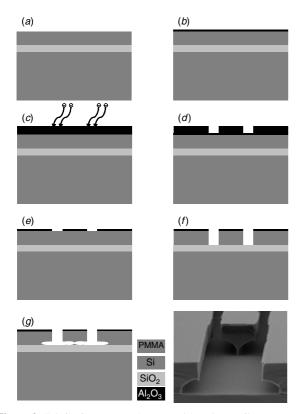

The process is based on the use of SOI (silicon-on-insulator) wafers (figure 2(a)). In the first stage an ultra-thin ( $t_{Al_2O_3}$  = 4 nm)  $Al_2O_3$  layer is deposited with ALD (figure 2(b)) which is covered with PMMA. The PMMA is exposed with electron beam (E-beam) lithography, allowing very high resolution without any pre-fabricated physical photomask (figures 2(c) and (d)). The alumina is etched with reactive ion etching (RIE) to form a hard mask for the etching of silicon; also the PMMA is removed in RIE with oxygen plasma (figure 2(e)). Finally, anisotropic cryo-DRIE is used to etch the vertical trenches defined by the masking  $Al_2O_3$  layer (figure 2(f)). When the etching reaches the buried oxide (BOX) *notching* takes place leading to isotropic etching of silicon on the buried oxide—silicon interface [11]. When etching is continued the notching effect causes a release of the devices, thus removing

**Figure 2.** Fabrication process (not to scale) and a cantilever resonator with etching stopped just prior to the release. (a) SOI wafer. (b)  $Al_2O_3$  film is deposited using atomic layer deposition (ALD). (c) PMMA is spun on alumina and exposed by E-beam. (d) PMMA is developed. (e) Alumina is etched by reactive ion etching (RIE) to form a hard mask for silicon etching. Also the PMMA layer is removed in oxygen plasma. (f) Silicon is etched in cryo-DRIE with alumina as hard mask to define the structures. (g) When the etching is continued after reaching the buried oxide, notching releases the device. Steps (e)—(g) can be performed in the DRIE in one run. It is evident from the figure that the widths of the openings in step (e) are very tolerant to over-etching.

the need for a wet release etch and the complicated drying of the etchant (figure 2(g)). The total processing time is typically less than 4 h.

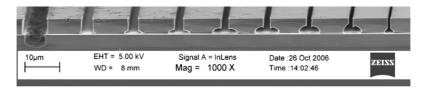

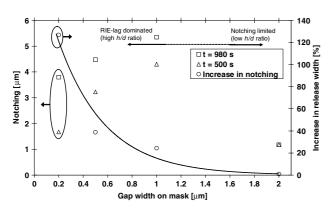

Rigorous tests considering etching times, temperatures and etch/cool cycles were carried out to determine the optimum recipe to combine the maximized notching and minimized widening of the gap. For these tests an SOI wafer with a  $h=4~\mu m$  thick device layer was used. Ten trenches with a length  $L_{\rm tr}=500~\mu m$  and width  $d=[5, 2, 1.7, 1.5, 1.2, 1, 0.7, 0.5, 0.2, 0.1] <math>\mu m$  were etched with the process and the cleaved cross-section was carefully analyzed with a scanning electron microscope (SEM). Figure 3 shows an SEM

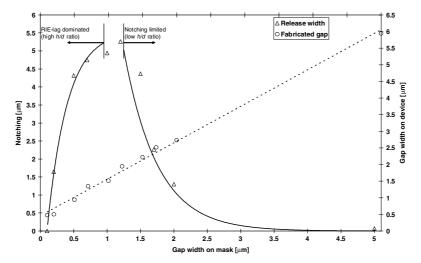

image of a result of such a test. The analyzed results plotted in figure 4 reveal that for each case, there is an optimum gap for the maximized release. Figure 4 also shows that features with width up to  $w=5~\mu m$  can be released while still maintaining the coupling gaps below  $d<1.5~\mu m$ .

The limiting factors for the release width can be seen from figure 4. For wide gaps, the notching effect becomes weak and totally vanishes when  $h/d \approx 1$ . This is in agreement with the other published results [12]. As figure 5 shows, in this parameter region, the notching cannot be further increased by increasing etching time. However, for higher h/d ratios (i.e. for lower d) the notching is remarkably increased at longer etching times, which is a clear indication that the governing reason for the limited notching here is the RIE-lag [13], meaning that structures with higher h/d ratios etch slower. The figure also shows that narrower gaps can be utilized with increased etching time

#### 4. Discussion

#### 4.1. Fabricated devices

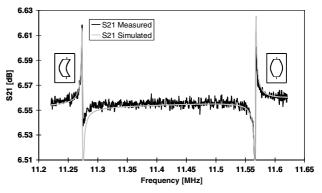

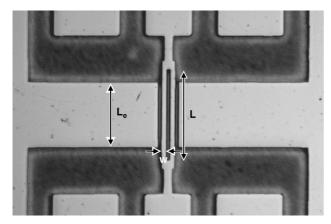

In order to test the process, several resonators were fabricated and characterized. The processed devices include cantilever and DETF (double-ended-tuning-fork) resonators (figure 6) with eigenfrequencies  $f_r > 10$  MHz. Figure 7 shows an electrical measurement of the  $S_{21}$  parameter of the component with design values of  $L = 38 \, \mu \text{m}$ ,  $w = 2.5 \, \mu \text{m}$  and  $d = 1 \, \mu \text{m}$ . For a detailed simulation of the results, these values were replaced by actual parameters extracted from SEM image. The Q-factor (Q) and electrical parameters were fitted using a circuit simulator [14]. The best fit was reached with  $Q \approx 8000$ , which is the highest reported value for the resonant devices fabricated with dry processes. This Q-value is also comparable to tuning fork resonators fabricated using conventional SOI micromachining [15].

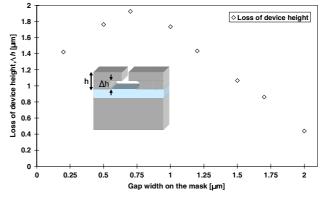

#### 4.2. The effect of notching on the device height

As the device release is done through the device layer silicon, the release changes the final device height. This parameter is usually omitted in the publications, but as can be seen below it has a role in capacitively coupled devices where it directly affects the coupling capacitance. The parameter comes into play when for example frequency reference (oscillator) applications are considered where the maximum output current is an interesting figure.

For a beam vibrating sinusoidally between dc-biased electrodes, the current generated can be written as

$$i = \eta \omega_r x,\tag{1}$$

**Figure 3.** Side profile of the etched structure reveals the notching effect. The widths of the gaps from left to right are  $d = [5, 2, 1.7, 1.5, 1.2, 1, 0.7, 0.5, 0.2] \mu m$ .

Figure 4. The horizontal axis shows the designed gap width on the mask. The circles (O) and dotted line indicate the actual fabricated coupling gap. The width of the released area is shown in triangles ( $\Delta$ ) with solid lines as exponential fits to the measured data. The release width for narrow gaps ( $d < 1 \mu m$ , i.e. high h/d ratio) can be increased by increasing the etching time as the limiting factor is the RIE-lag. From this figure straightforward design rules can be extracted.

**Figure 5.** Two etchruns with different time (squares ( $\square$ ) and triangles ( $\Delta$ )) reveal that the release width in the RIE-lag limited area (high h/r ratio) can be improved by increased etching time while in the notching limited region (low h/r ratio) this is not the case.

**Figure 7.** Measured and simulated  $S_{21}$  responses of a fabricated resonator. The two eigenfrequencies of the resonator indicate modes where the beams move either in-phase or in anti-phase.

**Figure 6.** Optical image of a fabricated and measured tuning fork resonator. The letters L and w denote the length and the width of the resonating beams, respectively.  $L_c$  is the length of the electrode.

**Figure 8.** As the release is done through the device layer silicon, also the height of the final device is affected, as can be seen from the inset. The diamonds  $(\lozenge)$  show the loss of device height,  $\Delta h$ , as a function of the designed gap width, d. For the capacitively coupled systems, the coupling capacitance is directly proportional to the final device height  $(h - \Delta h)$ .

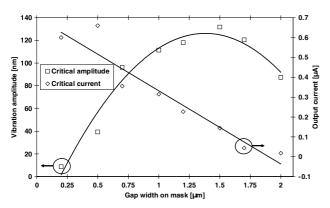

Figure 9. The calculated maximum amplitude of vibration ( $\square$ ) determined by the mechanical nonlinearity of the clamped–clamped beam fabricated with the proposed process and the maximum output current ( $\lozenge$ ) calculated from the maximum vibration amplitude and the dimensions of the fabricated beams.

where  $\omega_r$  is the resonance frequency of the device, x is the amplitude of vibration and  $\eta$  is the electomechanical coupling constant that can be written as

$$\eta \approx U_{\rm dc} \cdot \frac{C_0}{d} = U_{\rm dc} \frac{\varepsilon_0 \cdot h \cdot L_e}{d^2}.$$

(2)

The frequency of the first eigenmode for a clamped-clamped beam can be calculated as

$$\omega_r = 2\pi \cdot 1.03 \cdot \sqrt{\frac{E}{\rho}} \frac{w}{L^2}.$$

(3)

If we assume that the width of the resonator, w, is determined by the notching (figure 3), the resonance frequency can be kept constant by varying the length of the beam, L, as

$$L = \sqrt{2\pi \cdot 1.03 \cdot \sqrt{\frac{E}{\rho} \frac{w}{\omega_r}}}.$$

(4)

From (2) and (3) it is evident that the loss of device height due to the notching affects the maximum current output, but does not have an effect on the resonance frequency of the device.

If we assume that the length of the signal pick-up electrode  $L_e$  is 0.75·L, the coupling constant  $\eta$  can be written as

$$\eta = U_{\rm dc} \cdot \frac{\varepsilon_0 \cdot h \cdot 0.75}{d^2} \sqrt{2\pi \cdot 1.03 \cdot \sqrt{\frac{E}{\rho}} \frac{w}{\omega_r}}.$$

(5)

The critical vibration amplitude (amplitude, after which the response of the resonator becomes nonlinear) for a clamped–clamped beam can be assumed to be limited by the mechanical nonlinearity. Therefore, an approximation for the

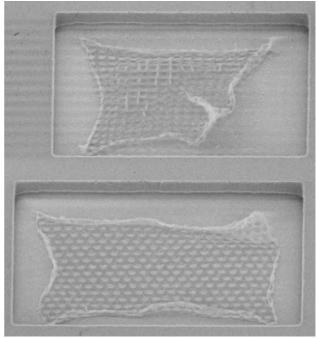

**Figure 11.** Masking  $Al_2O_3$  film is revealed after etching away a larger area of silicon under the film. The areas of the rectangles are  $40 \times 40 \ \mu m^2$  and  $40 \times 50 \ \mu m^2$ , respectively. The films are curled, but are otherwise intact.

maximum (=critical) amplitude,  $x_c$ , can be calculated from [16]

$$x_c = a\sqrt{\frac{1}{|k_2|Q}},\tag{6}$$

where Q is the mechanical quality factor,  $a = \sqrt{32/9\sqrt{3}}$  and  $k_2$  is the nonlinear spring constant of the second order and that can be approximated as [16]

$$k_2 = \frac{0.767}{w^2}. (7)$$

Inserting (7) into (6) and resulting (6) and (5) into (1) we can write for the critical output current

$$i_c = B \frac{h \cdot \sqrt{w^3}}{d^2},\tag{8}$$

which can be seen to be affected by all the three parameters considered. The coefficient B collects the fabrication independent constants

$$B = 2.18 \cdot U_{\rm dc} \cdot a \cdot \varepsilon_0 \cdot \sqrt{\frac{\omega_r}{Q}} \cdot \sqrt[4]{\frac{E}{\rho}}.$$

(9)

The loss of device height,  $\Delta h$ , due to the notching is plotted in figure 8. Due to the thin device layer  $(h = 4 \mu m)$

Figure 10. To characterize the uniformity of the notching in the lateral and vertical directions, 16 parallel trenches with  $d = 1 \mu m$  were etched. Due to the successful release of the narrowest bridges they were removed during the cleaving.

used in the study, the ratio  $\Delta h/h$  can be in the order of  $\Delta h/h \approx 0.5$  leading to decreased capacitive coupling. However, with thicker device layers ( $h \geqslant 10~\mu \text{m}$ ) the effect is not so severe. Assuming Q=8000,  $U_{\text{dc}}=100~\text{V}$  and beam in the [1 0 0] crystal direction (E=130~GPa and  $\rho=2330~\text{kg m}^{-3}$ ) with the resonance frequency  $\omega_r=2\pi\cdot 13~\text{MHz}$ , we can calculate the maximum vibration amplitude in the limit of the linear regime and the resulting critical output current as a function of the designed gap width (figure 9).

Quantitatively the above is valid only for clampedclamped-type resonators where the limiting factor is the mechanical nonlinearity, but qualitatively it clearly illustrates the importance of a thorough characterization of parameters that are affected when utilizing the dry etching in the release of micromechanical devices.

## 4.3. Uniformity

Because the exposure of the device is done via the E-beam, the processing area is limited by E-beam writing to 1 mm  $\times$  1 mm. In addition, due to the low exposuring speed, the process allows fabrication of a few devices at a time. In order to characterize the uniformity of the process within the relevant area, 16 parallel trenches with design dimension  $d=1~\mu m$  were fabricated with varying distances to each other and the loss of device height,  $\Delta h$ , and the notching width, w/2, were measured from the trenches. However, due to the proximity of some of the trenches, the beam in between was released and removed during the cleaving (figure 10) resulting in 21 measurable trenches. The average values were  $2 \cdot w = 4.86~\mu m$  and  $h = 1.65~\mu m$  with standard deviations  $\sigma_w = 0.24~\mu m$  and  $\sigma_{\Delta h} = 0.1~\mu m$  that include the inaccuracy of the measurement from SEM images.

## 5. Conclusions

Figure 11 shows clearly the tolerance of the  $Al_2O_3$  mask toward the etching of silicon. Here, the etching of the larger areas is tested and the remains of the  $Al_2O_3$  mask can be seen at the bottom of the rectangles. The films are curled, but are otherwise intact even though the device layer underneath them is completely etched away. The areas of the rectangles are  $40 \times 40 \ \mu m^2$  and  $40 \times 50 \ \mu m^2$  for the top and bottom one, respectively.

A rather high *Q*-value indicates that the process is capable of producing high quality micromechanical devices. The use of the dry process described is not limited to the fabrication of microresonators, but is suitable for all kinds of devices where released micromechanical features are needed. These include sensors, RF-MEMS components and optical switches. The high selectivity in cryogenic etching combined with the atomic layer deposited mask layer easily allows the fabrication using even thicker device layers than presented in the paper, which even further increases the electromechanical coupling.

# Acknowledgments

The work is financially supported by TEKES, the foundations of Jenny and Antti Wihuri and Magnus Ehrnrooth and the Finnish Academy of Science and Letters.

#### References

- [1] Nguyen C T-C 2001 Dig. of Papers, Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (Ann Arbor) p 23

- [2] Grigoras K, Sainiemi L, Tiilikainen K, Säynätjoki A, Airaksinen V-M and Franssila S 2007 J. Phys.: Conf. Ser. 61 369–74

- [3] Murakami K, Wakabayashi Y, Minami K and Esashi M 1993 Proc. IEEE MEMS' 93 (Ft. Lauderdale) p 65

- [4] Bosch GbmH R B 1994 US Patent 4855017, Germany Patent 4241045CI

- [5] Iliescu C and Miao J 2003 Electron. Lett. 39 658-9

- [6] Docker P T, Kinnell P and Ward M C L 2003 J. Micromech. Microeng. 13 790–4

- [7] Zhang W, Zhang W, Turner K and Hartwell P G 2004 Proc. IMECE04 (Anaheim) Paper no. 61140

- [8] Haobing L and Chollet F 2006 J. Microelectromech. Syst. 15 541–7

- [9] Puurunen R L 2005 J. Appl. Phys. 97 121301

- [10] Puurunen R L et al 2004 J. Appl. Phys. **96** 4878–89

- [11] Arnold J C and Sawin H H 1991 J. Appl. Phys. 70 5314-7

- [12] Kiihamäki J 2005 Fabrication of SOI micromechanical devices Doctoral Dissertation Helsinki University of Technology p 39

- [13] Chung C K 2003 J. Micromech. Microeng. 14 656-62

- [14] Aplac RF Design Tool AWR-APLAC Corp. Available at www.aplac.com

- [15] Alastalo A T, Koskenvuori M, Kiihamäki J and Seppä H 2004 Proc. EuMW2004 (Amsterdam) p 1297

- [16] Kaajakari V, Mattila T, Oja A and Seppä H 2004 J. Microelectomech. Syst. 13 715–24