Matti Järvisalo and Tommi Junttila. 2008. Limitations of restricted branching in clause learning. Constraints, to appear, 29 pages.

© 2008 by authors and © 2008 Springer Science+Business Media

Preprinted with permission.

# Limitations of Restricted Branching in Clause Learning

Matti Järvisalo · Tommi Junttila

Abstract The techniques for making decisions, that is, branching, play a central role in complete methods for solving structured instances of constraint satisfaction problems (CSPs). In this work we consider branching heuristics in the context of propositional satisfiability (SAT), where CSPs are expressed as propositional formulas. In practice, there are cases when SAT solvers based on the Davis-Putnam-Logemann-Loveland procedure (DPLL) benefit from limiting the set of variables the solver is allowed to branch on to so called input variables which provide a strong unit propagation backdoor set to any SAT instance. Theoretically, however, restricting branching to input variables implies a super-polynomial increase in the length of the optimal proofs for DPLL (without clause learning), and thus input-restricted DPLL cannot polynomially simulate DPLL. In this paper we settle the case of DPLL with clause learning. Surprisingly, even with unlimited restarts, input-restricted clause learning DPLL cannot simulate DPLL (even without clause learning). The opposite also holds, and hence DPLL and input-restricted clause learning DPLL are polynomially incomparable. Additionally, we analyze the effect of input-restricted branching on clause learning solvers in practice with various structured real-world benchmarks.

**Keywords** propositional satisfiability, branching heuristics, clause learning, DPLL, proof complexity, problem structure, backdoor sets

E-mail: matti.jarvisalo@tkk.fi, tommi.junttila@tkk.fi

This is an extended version of a paper [27] presented at the 13th International Conference on Principles and Practice of Constraint Programming (CP 2007) in Providence, RI, USA. The first author gratefully acknowledges financial support from Helsinki Graduate School in Computer Science and Engineering, Academy of Finland (grants #211025 and #122399), Emil Aaltonen Foundation, Jenny and Antti Wihuri Foundation, Foundation of Technology TES, and Nokia Foundation. The second author gratefully acknowledges the financial support from Academy of Finland (grant #112016).

#### 1 Introduction

Modern complete satisfiability (SAT) solvers (such as [39,40,22,18] among others) provide an efficient way of solving various real-world problems as propositional satisfiability. Typical SAT solvers aimed at solving such structured problems are based on the conjunctive normal form (CNF) level *Davis-Putnam-Logemann-Loveland* procedure (DPLL) [17, 16] and incorporate techniques such as *intelligent branching heuristics*, *randomization* and *restarts* [23], and *clause learning* [39] for boosting search efficiency.

Branching heuristics, that is, deciding on which variable to next set a value during search, play an important role in the efficiency of complete SAT methods aimed at solving typically very large real-world problem instances. Intuitively, the inherent structure of the problem domain is reflected in individual variables in the SAT encoding, and making decisions on structurally irrelevant variables may have an exponential effect on the running times of SAT solvers.

In SAT-based approaches to structured problems such as bounded model checking [10] and automated planning [33], the CNF encoding is often derived from a transition relation, where the behavior of the underlying system is dependent on the *input*—initial state, nondeterministic choices due to external control, et cetera—of the system. Empirical case studies [14, 20, 45, 19] have shown that, in some cases, SAT solvers benefit from restricting the variables the solver is allowed to branch on to so called *input* (or *independent*) *variables*, corresponding to the input of the underlying system. By noticing that the system behavior is determined by its input, it is in fact the case that all variables in the SAT encoding of the system can be assigned through unit propagation once all input variables have been assigned values. In other words, the set of input variables is a *strong unit propagation backdoor set* [51]—although possibly not of *minimum* cardinality. Hence DPLL remains complete even if branching is restricted to the set of input variables alone. Intuitively, this drops the raw search space size from  $2^N$  to  $2^I$  with  $I \ll N$ , where I and N are the number of input variables and all variables in the CNF encoding, respectively.

From another point of view to the effects of different techniques for branching, one can investigate the *best-case* performance of SAT algorithms through *proof complexity* [13], by studying the relative power of their underlying inference systems (or *proof systems*) in terms of the shortest existing proofs in the systems. For two proof systems, S and S', we say that S' (*polynomially*) *simulates* S if, for all infinite families  $\{F_n\}$  of unsatisfiable CNF formulas, there is a polynomial that bounds for all  $F_n$  the length of the shortest proofs in S' w.r.t. the length of the shortest proofs in S. If S' simulates S and vice versa, then S and S' are *polynomially equivalent*. If S' cannot simulate S and vice versa, then S and S' are *incomparable*. From the practical point of view, if S' cannot simulate S, we know that any implementation of S' can suffer a notable decrease in efficiency compared to implementations of S. For example, through a formal characterization of DPLL with clause learning, called CL, Beame et al. [9] show that CL can provide superpolynomially shorter proofs than DPLL, and thus DPLL cannot simulate CL.

Considering restricting branching in DPLL algorithms to input variables, a natural question to ask is *whether the power of the underlying inference systems of* DPLL-*based solvers is affected by the input-restriction*. For DPLL without clause learning, this question is answered in [29]: input-restricted DPLL cannot simulate DPLL.

In this paper we settle the case of input-restricted CL: it turns out that input-restricted CL cannot simulate CL. This implies that all implementations of clause learning DPLL, even with optimal heuristics, have the potential of suffering a notable efficiency decrease if branching is restricted to input variables. In fact, we show that even with unlimited restarts

and the ability to create conflicts at will, input-restricted CL cannot even simulate the basic DPLL without clause learning. This is surprising, since the unrestricted version of this variant of CL can efficiently simulate (general) Resolution [9], being thus very powerful compared to DPLL. Additionally, we evaluate the effect of input-restricted branching on clause learning with various structured real-world benchmarks, with possible explanations for the reasons why input-restricted branching can in fact hinder the efficiency of typical clause learning solvers.

As preliminaries, in Section 2 we define Boolean circuits, which we use for representing general propositional formulas, and discuss their relation to CNF formulas. We then review the Resolution proof system and characterizations of DPLL and CL, and discuss known results concerning their relative efficiency (Section 3). Section 4 concentrates on the tight correspondence between a constrained Boolean circuit and its CNF translation from the viewpoint of DPLL and clause learning, which is of value in presenting the theoretical results of this work. The main theoretical and experimental contributions of this paper are presented in Sections 5 and 6, respectively.

#### 2 Propositional Satisfiability and Constrained Boolean Circuits

In this section we review basic concepts related to propositional satisfiability and define constrained Boolean circuits which we use as the representation form for structural formulas. We also discuss the relationship between constrained Boolean circuits and clausal propositional (CNF) formulas, and present the translation from constrained Boolean circuits to CNF which is applied in this work.

#### 2.1 Propositional Satisfiability

Given a Boolean variable x, there are two *literals*, the positive literal, denoted by x, and the negative literal, denoted by  $\neg x$ , where  $\neg$  is the logical negation (not). As usual, we identify  $\neg \neg x$  with x. A *clause* is a disjunction ( $\lor$ , or) of distinct literals and a CNF formula is a conjunction ( $\land$ , and) of clauses. When convenient, we view a clause as a finite set of literals and a CNF formula as a finite set of clauses; e.g. the formula  $(a \lor \neg b) \land (\neg c)$  can be written as  $\{\{a, \neg b\}, \{\neg c\}\}$ . The sets of variables appearing as positive and negative literals in a CNF formula F are denoted by  $\mathsf{vars}^+(F)$  and  $\mathsf{vars}^-(F)$ , respectively, and the set of variables by  $\mathsf{vars}(F)$ ; for a clause F,  $\mathsf{vars}(F)$ ,  $\mathsf{vars}(F)$ , and  $\mathsf{vars}(F)$  are defined similarly.

Given a CNF formula F, a (partial) assignment for F is a (partial) function  $\tau$ : vars $(F) \rightarrow \{\mathbf{t}, \mathbf{f}\}$ , where  $\mathbf{t}$  and  $\mathbf{f}$  stand for true and false, respectively. With a slight abuse of notation, if  $\tau(x) = v$ , then  $\tau(\neg x) = \neg v$ , where  $\neg \mathbf{t} = \mathbf{f}$  and  $\neg \mathbf{f} = \mathbf{t}$ . A clause is satisfied by  $\tau$  if it contains at least one literal l such that  $\tau(l) = \mathbf{t}$ . If  $\tau(l) = \mathbf{f}$  for every literal l in a clause, the clause is falsified by  $\tau$ . An assignment  $\tau$  satisfies a CNF formula it satisfies every clause in the formula. A formula is satisfiable if there is an assignment that satisfies it, and unsatisfiable otherwise.

# 2.2 Constrained Boolean Circuits

The correspondence between system input of a real-world problem and propositional variables in a CNF encoding is not evident. However, in SAT-based approaches, direct CNF

encodings of a problem domain are rarely used: the problem at hand is typically encoded with a general propositional formula  $\phi$ , which is then translated into an equi-satisfiable CNF formula by introducing additional variables for the sub-formulas of  $\phi$ . Boolean circuits (see e.g. [42]) offer a natural way of presenting propositional formulas in a compact DAG-like structure with *sub-formula sharing*, which helps in lowering the number of additional variables needed. Additionally, the system input of the original problem is presented by *input gates* in Boolean circuits.

A Boolean circuit over a finite set G of gates is a set  $\mathscr C$  of equations of form  $g := f(g_1, \ldots, g_n)$ , where  $g, g_1, \ldots, g_n \in G$  and  $f : \{\mathbf f, \mathbf t\}^n \to \{\mathbf f, \mathbf t\}$  is a Boolean function, with the additional requirements that (i) each  $g \in G$  appears at most once as the left hand side in the equations in  $\mathscr C$ , and (ii) the underlying directed graph

$$\langle G, E(\mathscr{C}) = \{ \langle g', g \rangle \in G \times G \mid g := f(\dots, g', \dots) \in \mathscr{C} \} \rangle$$

is acyclic. If  $\langle g',g\rangle \in E(\mathscr{C})$ , then g' is a *child* of g and g is a *parent* of g'. Similarly, if there is a non-empty path from a gate g' to a gate g in  $\langle G, E(\mathscr{C})\rangle$ , then g' is a *descendant* of g. If  $g:=f(g_1,\ldots,g_n)$  is in  $\mathscr{C}$ , then g is an f-gate (or of type f), otherwise it is an *input gate*. A gate with no parents is an *output gate*. A (partial) assignment for  $\mathscr{C}$  is a (partial) function  $\tau:G\to \{\mathbf{f},\mathbf{t}\}$ . An assignment  $\tau$  is *consistent* with  $\mathscr{C}$  if  $\tau(g)=f(\tau(g_1),\ldots,\tau(g_n))$  for each  $g:=f(g_1,\ldots,g_n)$  in  $\mathscr{C}$ . Note that a circuit with I input gates has  $2^I$  consistent assignments.

A constrained Boolean circuit  $\mathscr{C}^{\tau}$  is a pair  $\langle \mathscr{C}, \tau \rangle$ , where  $\mathscr{C}$  is a Boolean circuit and  $\tau$  is a partial assignment for  $\mathscr{C}$ . With respect to a  $\langle \mathscr{C}, \tau \rangle$ , each  $\langle g, v \rangle \in \tau$  is a constraint, and g is constrained to v if  $\langle g, v \rangle \in \tau$ . An assignment  $\tau'$  satisfies  $\mathscr{C}^{\tau}$  if (i) it is consistent with  $\mathscr{C}$ , and (ii) it respects the constraints in  $\tau$ , meaning that for each gate  $g \in G$ , if  $\tau(g)$  is defined, then  $\tau'(g) = \tau(g)$ . If some assignment satisfies  $\mathscr{C}^{\tau}$ , then  $\mathscr{C}^{\tau}$  is satisfiable and otherwise unsatisfiable.

In the following, we will apply the following Boolean functions as gate types. Notice that this set of is sufficient for representing all Boolean functions, and on the other hand, enough for describing the constructions applied in this paper in an intuitive way.

- NOT(g) evaluates to **t** if and only if g evaluates to **f**.

- $OR(g_1,...,g_n)$  evaluates to **t** if and only if at least one of  $g_1,...,g_n$  evaluates to **t**.

- AND $(g_1, \ldots, g_n)$  evaluates to **t** if and only if all  $g_1, \ldots, g_n$  evaluate to **t**.

- XOR $(g_1, g_2)$  evaluates to **t** if and only if exactly one of  $g_1, g_2$  evaluates to **t**.

*Example 1* A Boolean circuit  $\mathscr{C}^{\tau}$  and its graphical representation are shown in Figure 1. The circuit models a full-adder with the constraint that the carry-out bit  $c_1$  is  $\mathbf{t}$ . A satisfying truth assignment for the circuit is  $\tau' = \{\langle c_1, \mathbf{t} \rangle, \langle t_1, \mathbf{t} \rangle, \langle o_0, \mathbf{f} \rangle, \langle t_2, \mathbf{f} \rangle, \langle t_3, \mathbf{t} \rangle, \langle a_0, \mathbf{t} \rangle, \langle b_0, \mathbf{f} \rangle, \langle c_0, \mathbf{t} \rangle \}$ .

**Fig. 1** A constrained Boolean circuit  $\mathscr{C}^{\tau}$  and its graphical representation.

For notational convenience, when well-defined, the *join* of two constrained circuits,  $\mathscr{A}^{\tau} = \langle \mathscr{A}, \tau \rangle$  and  $\mathscr{B}^{\theta} = \langle \mathscr{B}, \theta \rangle$ , is  $\mathscr{A}^{\tau} \cup \mathscr{B}^{\theta} = \langle \mathscr{A} \cup \mathscr{B}, \tau \cup \theta \rangle$ . When applying the join, we will always make sure that the result is a well-defined constrained Boolean circuit. This means that the requirements (i) on unique definition and (ii) on acyclicity above are met, and that  $\tau \cup \theta$  is a (possibly partial) function.

# 2.3 Translating Boolean Circuits to CNF

In order to exploit clausal SAT solvers in solving instances of Boolean circuit satisfiability, the circuit in question has to be translated to CNF. In this work we apply the standard "Tseitin-style" [47] translation. First, a variable  $\tilde{g}$  is introduced for each gate g. For encoding the functionalities of gates, the idea is to represent the logical equivalence  $g \Leftrightarrow f(g_1, \ldots, g_n)$  as clauses; hence for each  $g := f(g_1, \ldots, g_n)$  the corresponding introduced clauses are as shown in Table 1. Similarly, a unit clause is added for each constraint  $\langle g, v \rangle \in \tau$  as shown in Table 1. Given a constrained Boolean circuit  $\mathscr{C}^{\tau}$ , we will denote its CNF translation by  $\operatorname{cnf}(\mathscr{C}^{\tau})$ .

Table 1 CNF translation for constrained Boolean circuits.

| gate or constraint                     | clauses                                                                                                                                                                                                                    |  |  |  |  |  |  |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| $g := XOR(g_1, g_2)$                   | $(\neg \tilde{g} \vee \neg \tilde{g}_1 \vee \neg \tilde{g}_2), (\neg \tilde{g} \vee \tilde{g}_1 \vee \tilde{g}_2), (\tilde{g} \vee \neg \tilde{g}_1 \vee \tilde{g}_2), (\tilde{g} \vee \tilde{g}_1 \vee \neg \tilde{g}_2)$ |  |  |  |  |  |  |

| $g := OR(g_1, \ldots, g_n)$            | $(\neg \widetilde{g} \vee \widetilde{g}_1 \vee \dots \vee \widetilde{g}_n), (\widetilde{g} \vee \neg \widetilde{g}_1), \dots, (\widetilde{g} \vee \neg \widetilde{g}_n)$                                                   |  |  |  |  |  |  |

| $g := AND(g_1, \ldots, g_n)$           | $(\neg \tilde{g} \vee \tilde{g}_1), \ldots, (\neg \tilde{g} \vee \tilde{g}_n),  (\tilde{g} \vee \neg \tilde{g}_1 \vee \cdots \vee \neg \tilde{g}_n)$                                                                       |  |  |  |  |  |  |

| $g := NOT(g_1)$                        | $(\lnot 	ilde{g} \lor \lnot 	ilde{g}_1), (	ilde{g} \lor 	ilde{g}_1)$                                                                                                                                                       |  |  |  |  |  |  |

| $\langle g, \mathbf{t}  angle \in 	au$ | $(	ilde{g})$                                                                                                                                                                                                               |  |  |  |  |  |  |

| $\langle g,\mathbf{f}\rangle\in\tau$   | $(\neg \tilde{g})$                                                                                                                                                                                                         |  |  |  |  |  |  |

### 2.4 CNF Formulas as Constrained Circuits

Any CNF formula  $F = \{C_1, \dots, C_k\}$  can naturally be seen as a Boolean circuit. Basically, F is a Boolean circuit with an AND of ORs which represent the clauses. Formally, circuit $(F) := \langle \mathscr{C}, \tau \rangle$  is defined by associating an input gate x with each variable  $x \in \mathsf{vars}(F)$ , a NOT-gate  $g_{\neg x}$  with each  $x \in \mathsf{vars}^{\neg}(F)$ , an OR-gate  $g_{C_i}$  with each clause  $C_i \in F$ , an AND-gate  $g_F$  with F, and by setting  $\tau = \{\langle g_F, \mathbf{t} \rangle\}$  and

$$\mathscr{C} := \{g_F := \text{AND}(g_{C_1}, \dots, g_{C_k})\} \cup \{g_{\neg x} := \text{NOT}(x) \mid x \in \text{vars}^-(F)\} \cup \{g_{C_i} := \text{OR}(\alpha(l_{i,1}), \dots, \alpha(l_{i,n_i})) \mid C_i = \{l_{i,1}, \dots, l_{i,n_i}\} \in F\}$$

where  $\alpha(\neg x) = g_{\neg x}$  and  $\alpha(x) = x$  for each  $x \in \text{vars}(F)$ .

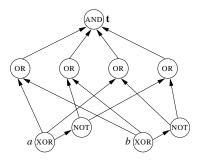

*Example 2* The constrained Boolean circuit circuit(F) for the unsatisfiable CNF formula  $F = \{\{a,b\},\{a,\neg b\},\{\neg a,b\},\{\neg a,\neg b\}\}\$  is shown in Figure 2.

**Fig. 2** The constrained Boolean circuit circuit  $(\{\{a,b\},\{a,\neg b\},\{\neg a,b\},\{\neg a,\neg b\}\})$ .

#### 3 Proof Systems for CNF Formulas

In this section we discuss the propositional proof systems of interest in the context of this work, with known results on their relative efficiency. First, we formally define propositional proof systems and the necessary proof complexity theoretic notions. We then review the well-known Resolution proof system and some of its refinements. After this, we concentrate on the Davis–Putnam–Logemann–Loveland (or DPLL) procedure [17,16] and the additional techniques applied in typical DPLL-based SAT solvers today—most importantly, clause learning. In doing so, we go through characterizations of DPLL (with and without clause learning) as proof systems, which we will apply in the theoretical part of the work.

### 3.1 Propositional Proof Systems and Complexity

Formally, a *propositional proof system* [13] is a polynomial-time computable predicate S such that a propositional formula F is unsatisfiable if and only if there is a *proof* p for which S(F,p) holds. Thus a proof p of F is a *certificate* of the unsatisfiability of F, and a proof system is a polynomial-time procedure for checking the validity of proofs in a certain format.

While proof checking is efficient, finding short proofs may be difficult, or, generally, impossible since short proofs may not exist for too weak a proof system. As a measure of hardness of proving unsatisfiability of a CNF formula F in a proof system S, the (proof) complexity  $C_S(F)$  of F in S is the length of the shortest proof of F in S. For a family  $\{F_n\}$  of unsatisfiable CNF formulas over an increasing number of variables, the (asymptotic) complexity of  $\{F_n\}$  is measured with respect to the number of clauses in  $F_n$ .

For two proof systems, S and S', we say that S' (polynomially) simulates S if for all families  $\{F_n\}$  there is a polynomial p such that  $C_{S'}(F_n) \leq p(C_S(F_n))$  for all  $F_n$ . If S simulates S' and vice versa, then S and S' are polynomially equivalent. If there is a family  $\{F_n\}$  for which S' does not polynomially simulate S, we say that  $\{F_n\}$  separates S from S'. If S can be separated from S' and vice versa, then S and S' are incomparable. Notice that polynomial simulation gives a partial order for proof systems based on their relative power.

With these definitions, in order to show that a proof system S cannot simulate another system S', it suffices to exhibit an infinite family  $\{F_n\}$  of unsatisfiable formulas over an increasing number of variables, such that the minimum length proofs in S for  $\{F_n\}$  are asymptotically superpolynomially longer than the minimum length proofs in S' with respect to the number of clauses in  $F_n$ . It is worth noticing that, from this basic proof complexity

theoretic point of view only *unsatisfiable* formulas (and hence proofs of unsatisfiability) are of interest. Although exponential lower bounds for DPLL on families of *satisfiable* formulas have been shown in restricted probabilistic contexts [41,2,1,4], a satisfying truth assignment acts as a polynomial length witness for the satisfiability of an arbitrary satisfiable formula F.

#### 3.2 Resolution

The well-known Resolution proof system [44] (RES) is based on the *resolution rule*. Let C,D be clauses, and x a Boolean variable. The resolution rule is

$$\frac{\{x\} \cup C \quad \{\neg x\} \cup D}{C \cup D}$$

or, in other words, we can *directly derive*  $C \cup D$  from  $\{x\} \cup C$  and  $\{\neg x\} \cup D$  by *resolving* on x. For a given CNF formula F, a RES *derivation of a clause* C from F is a sequence of clauses  $\pi = (C_1, C_2, \ldots, C_m = C)$ , where each  $C_i$ ,  $1 \le i \le m$ , is either (i) a clause in F (an *initial clause*), or (ii) directly derived with the resolution rule from two clauses  $C_j$ ,  $C_k$  where  $1 \le j, k < i$  (a *derived clause*). The *length* of  $\pi$  is m, the number of clauses occurring in it. A RES *proof (for the unsatisfiability)* of a CNF formula F is any RES derivation of the empty clause  $\emptyset$  from F.

Any RES derivation  $\pi = (C_1, C_2, ..., C_m)$  can be presented as a directed acyclic graph, in which the leafs are initial clauses and the other nodes represent derived clauses. The edge relation is defined so that there are edges from  $C_i$  and  $C_j$  to  $C_k$ , if and only if  $C_k$  has been directly derived from  $C_i$  and  $C_j$  using the resolution rule. Many *refinements of* Resolution, in which the structure of RES proofs is restricted, have been proposed and studied. Here of particular interest is *Tree-like Resolution* (T-RES), with the requirement that proofs are representable as trees. This implies that a derived clause, if used multiple times in the proof, must be derived anew each time starting from initial clauses.

#### 3.2.1 Lower Bounds in RES and its Refinements

Super-polynomial (and even exponential) lower bounds on proof lengths in RES have been shown for various families of CNF formulas, see [11,24,47,48,15,3,6,7] for examples. Among the most studied such families is the *pigeon-hole principle*, which states that there is no injective mapping from an m-element set into an n-element set if m > n (that is, m pigeons cannot sit in fewer than m holes so that every pigeon has its own hole). We will consider the case m = n + 1 encoded as the CNF formula

$$\mathrm{PHP}^{n+1}_n := \bigwedge_{i=1}^{n+1} \Big(\bigvee_{j=1}^n p_{i,j}\Big) \wedge \bigwedge_{j=1}^n \bigwedge_{i=1}^{n} \bigwedge_{i'=i+1}^{n+1} (\neg p_{i,j} \vee \neg p_{i',j}),$$

where each  $p_{i,j}$  is a Boolean variable with the interpretation " $p_{i,j}$  is **t** if and only if the  $i^{th}$  pigeon sits in the  $j^{th}$  hole".

**Theorem 1** ([24]) There is no polynomial length RES proof of  $PHP_n^{n+1}$ .

It is also known that T-RES is a proper refinement of RES in the sense that T-RES cannot polynomially simulate RES.

# **Theorem 2** ([21,49]) T-RES cannot polynomially simulate RES.

This originates from the facts that *regular resolution* cannot simulate RES [21,5], and T-RES in turn cannot simulate regular resolution [49].

#### 3.3 The Davis-Putnam-Logemann-Loveland Procedure

Most modern complete SAT solvers are based on the Davis–Putnam–Logemann–Loveland (or DPLL) procedure [17,16]. Given a CNF formula F as input, DPLL is a depth-first search procedure building a partial assignment  $\tau$  for the variables in F through (i) *branching* and (ii) *unit propagation* (UP). In branching, the current assignment  $\tau$  is extended with the assignment (*decision*)  $\langle x, v \rangle$ , where v is either  $\mathbf{f}$  of  $\mathbf{t}$ , for some unassigned variable x. Unit propagation refers to applying the *unit clause rule*. The unit clause rules states that if there is a clause  $(l_1 \vee \cdots \vee l_k \vee l) \in F$  such that  $\tau(l_i) = \mathbf{f}$  for each  $1 \leq i \leq k$ , the current partial assignment  $\tau$  can be extended with  $\langle l, \mathbf{t} \rangle$ .

An assignment is extended until (i) some variable x would be assigned both  $\mathbf{f}$  and  $\mathbf{t}$  (a conflict is reached, with x as the conflict variable) or (ii)  $\tau$  satisfies F (in which case DPLL terminates). In case (i), non-clause learning DPLL solvers backtrack to the last branching decision which has not been backtracked upon, undoing all assignments made by UP after the particular decision, and flip the decision. DPLL terminates on an unsatisfiable CNF formula when there are no untried branches left.

From the proof theoretic point of view, DPLL can be seen as a tableau proof system with two rules: the *branching rule* and the unit clause rule. The branching rule, corresponding to branching on a variable x, extends the branch into two branches, one of which is extended with the entry x and the other with  $\neg x$ . The unit clause rule, defined above, is similarly applied by extending the branch with l. As typical, a branch is (fully) extended until we have both of the entries x and  $\neg x$  for some variable, or no new entries can be generated with the branching and unit clause rules. From an algorithmic point of view, the choice of in which order branches are extended is part of the solver strategy, and based on a *decision heuristic*. The other branch resulting from the particular application of the branching rule is handled through backtracking. With this intuition, it is clear that a search tree traversed by a DPLL algorithm corresponds to a binary tableau proof, having the form of a binary tree, with all branches fully extended. Hence, a DPLL *proof* will here be such a tableau proof. The length of a DPLL proof is defined as the number of applications of the branching rule in the proof.

One-step lookahead (see, e.g., [37]) is an often implemented technique in (non-clause learning) DPLL algorithms. In one-step lookahead, if there is an assignment v to a currently unassigned variable x such that the current assignment  $\tau$  with the addition of  $\langle x, v \rangle$  leads to a conflict using unit propagation, then x is immediately assigned the value  $\neg v$ . This technique does not add to the strength of DPLL, since the same effect can obviously be accomplished by branching on x.

It is well-known that DPLL and T-RES can polynomially simulate each other (see [8] for example). One can show that for any unsatisfiable CNF formula, a minimum length DPLL proof, with applications of the unit clause rule "simulated by branching", always corresponds one-to-one with a minimum length T-RES proof, and vice versa.

**Fact 1** DPLL and T-RES are polynomially equivalent.

#### 3.3.1 Implication Graphs

*Implication graphs* capture the ways of deriving values for variables with the unit clause rule from assignments made by branching. We will apply this concept in the following for defining clause learning. However, first we need some additional terminology.

A stage of DPLL on a CNF formula *F* is characterized by the *decision literals* in the branch. Considering an arbitrary branch, the variables assigned by branching are called *decision variables* and those assigned values by UP are *implied variables*, with analogous definitions for *decision literals* and *implied literals*. The *decision level of a decision variable x* is one more than the number of decision variables in the branch before branching on *x*. The *decision level of an implied variable x* is the number of decision variables in the branch when *x* is assigned a value. The decision level of DPLL at any stage is the number of decision variables in the branch.

For a given CNF formula F and a set of literals L, we denote by  $F, L \vdash_{\text{UP}} l$  the fact that l can be deduced from F and L by iteratively applying the unit clause rule.

**Definition 1** For a CNF formula F, the *implication graph*  $G = \langle V, E \rangle$  at a given stage of DPLL with the set of decision literals D is a directed graph. The set of nodes is defined as

$$V = \{\Lambda\} \cup D \cup \{l \mid F, D \vdash_{\mathrm{UP}} l\},\$$

where  $\Lambda$  is a special *conflict node*, and the edge relation is

$$E = \{ \langle \neg l_i, l \rangle \mid \{l_1, \dots, l_k, l\} \in F \text{ and } \neg l_1, \dots, \neg l_k \in V \} \cup \{ \langle x, \Lambda \rangle, \langle \neg x, \Lambda \rangle \mid x, \neg x \in V \}.$$

For a given implication graph, a variable x with both  $x, \neg x \in V$  is called a *conflict variable*, and  $x, \neg x$  are *conflict literals*. An implication graph contains a conflict if it contains a conflict variable; DPLL has a conflict at a given stage if the implication graph at the stage contains a conflict.

#### 3.4 DPLL with Clause Learning and Modern SAT Solvers

Clause learning DPLL algorithms differ from non-clause learning algorithms in what happens when reaching a conflict. If a conflict is reached without any branching, DPLL (with or without clause learning) determines the formula F unsatisfiable. In other cases, non-clause learning DPLL algorithm perform simple backtracking as previously explained. In clause learning DPLL algorithms, however, the conflict is *analyzed*, and a *learned clause* (or *conflict clause*), which describes the "cause" of the conflict, is added to F. After this the search is continued typically by applying *non-chronological backtracking* (or *conflict-driven backjumping*) for backtracking to an earlier decision level that "caused" the conflict. Conflict-driven backjumping results in the fact that, as opposed to the basic backtracking in DPLL, the other branch (opposite value) of decision variables is not necessarily forced systematically when backtracking. In other words, branching in clause learning DPLL is seen simply as assigning values to unassigned variables, rather than as a branching rule in which by branching on a variable x the current branch is always extended into two branches, one with x and the other with  $\neg x$ .

# 3.4.1 Conflict Graphs and Conflict Analysis

Similarly as with DPLL, the *stage* of a clause learning DPLL algorithm is characterized by the set of decision literals. At a given stage of a clause learning DPLL algorithm, a clause is called *known* if it either appears in the original CNF formula *F* or has been learned earlier during the search. Conflict analysis is based on a *conflict graph*, which captures one way of reaching the conflict at hand from the decision variables by using the unit clause rule on known clauses.

**Definition 2** Given an implication graph G, a conflict graph H = (V, E) based on G is any acyclic subgraph of G having the following properties.

- 1. H contains  $\Lambda$  and exactly one conflict literal pair  $x, \neg x$ .

- 2. All nodes in H have a path to  $\Lambda$ .

- 3. Every node  $l \in V \setminus \{\Lambda\}$  either corresponds to a decision literal or has precisely the nodes  $\neg l_1, \neg l_2, \dots, \neg l_k$  as predecessors where  $\{l_1, l_2, \dots, l_k, l\}$  is a known clause.

A conflict graph describes a single conflict and contains only decision and implied literals that can be used in reaching the conflict when applying the unit clause rule *in some order*. Hence the way of implementing unit propagation in a solver has an effect on the choice of the conflict graph. The acyclicity of conflict graphs results from the fact that unit propagation is not used to rederive already assigned literals.

Conflict clauses are associated with *cuts* in a conflict graph. Fix a conflict graph contained in an implication graph with a conflict. A *conflict cut* is any cut in the conflict graph with all the decision variables on one side (the *reason side*) and, in addition to  $\Lambda$ , at least one conflict literal on the other side (the *conflict side*). Those nodes on the reason side with at least one edge going to the conflict side in a conflict cut form a cause of the conflict. With the associated literals set to  $\mathbf{t}$ , UP can arrive at the conflict at hand. The disjunction of the negations of these literals form the *conflict clause associated with the conflict cut*. The strategy for fixing a conflict cut is called the *learning scheme*. A learning scheme which always learns a currently unknown clause is called *non-redundant*.

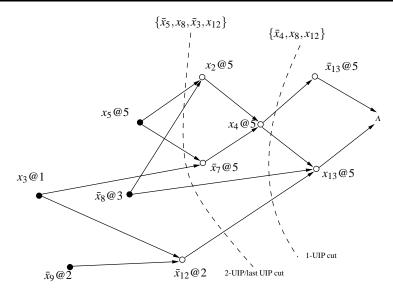

Example 3 A hypothetical conflict graph is illustrated in Figure 3. Decision literals are represented with filled circles, and implied literals with hollow circles. The decision level d of each literal l is presented with the label l@d. For example, the conflict variable  $x_{13}$  is at decision level 5. Notice that since the literals at decision level 4 are missing from this conflict graph, they are not part of the reason for the particular conflict. In the figure two possible conflict cuts are shown with the associated conflict clauses.

# 3.4.2 Unique Implication Points, Conflict-Driven Backjumping, and CL Proofs

Typically implemented clause learning schemes are based on *unique implication points* (UIPs) [39]. A UIP in a conflict graph is a node u on the maximum decision level d such that all paths from the decision variable x at level d to  $\Lambda$  go through u. Such a u always exists as x satisfies this condition. Intuitively, u is a *single* reason for the conflict at level d. Thus one can always choose a conflict cut that results in a conflict clause with a UIP as the only variable from the maximum decision level. Such a conflict clause has the property that the UIP variable can be immediately set to the value opposite to the current assignment using the unit clause rule when backtracking (the phrase "the UIP is *asserted*" is sometimes used). Furthermore, UIP learning schemes enable *conflict-driven backtracking* (or *backjumping*),

Fig. 3 Example of a conflict graph, and two possible conflict cuts

in which DPLL backtracks to the maximum decision level of the variables other than the UIP in a conflict clause. A popular version of UIP learning is the 1-UIP scheme, where a conflict cut is chosen so that the UIP closest to  $\Lambda$  will be in the associated conflict clause. Different learning schemes are evaluated in [52], showing the robustness of the 1-UIP scheme in practice.

Example 4 Recall the conflict graph in Figure 3. The 1-UIP in this graph is the literal  $x_4$ . One conflict cut corresponding to the 1-UIP learning scheme is the cut labeled "1-UIP cut". The cut labeled "2-UIP cut/last UIP cut" can result from applying the *second UIP scheme* in which a conflict clause with the UIP second closest to  $\Lambda$  is chosen. In this example, the "2-UIP cut" is at the same time a cut that can result from applying the *last UIP scheme* in which a cut with the decision literal on the maximum decision level as the UIP is chosen.

For investigating the efficiency of clause learning DPLL in proof complexity theoretic terms, we need to have a proof system characterization of clause learning DPLL algorithms. We will use the following characterization, referred to as the CL *proof system*. Here we loosely follow the characterization of [9]. A clause learning proof (or CL proof) induced by a learning scheme *S* is constructed by applying branching and the unit clause rule, using *S* to learn conflict clauses when conflicts are reached, so that in the end, a *conflict can be reached at decision level zero*. When a conflict cut with a UIP is selected, it is possible to apply conflict-driven backjumping based on the conflict clause. Otherwise, simple backtracking is applied. Notice that this definition allows even the most general *nondeterministic learning scheme* [9], in which the conflict cut is selected nondeterministically from the set of all possible conflict cuts related to the conflict graph at hand.

Hence, a CL proof can be seen as a tree in which the traversal order is marked in the nodes. Each leaf node in the tree is labeled with a conflict graph, a conflict cut in the graph, and the decision level onto which to backjump. Now, the proof system CL consists of CL proofs under any learning scheme. The length of a CL proof is the number of branching decisions.

While the practical efficiency gains of implementing clause learning into DPLL-based algorithms are well-established, the first formal study on the power of clause learning is [9]: CL can provide exponentially shorter proofs than T-RES even if no restarts are allowed. Thus we have the following corollary.

#### Corollary 1 (of Theorem 1 in [9]) DPLL cannot polynomially simulate CL.

#### 3.4.3 Restarts and the CL-- Proof System

Restarting is an additional technique often implemented in modern solvers. When a restart occurs, the decisions and unit propagations made so far are undone, and the search continues from decision level zero. The clauses learned so far remain known after the restart. Intuitively, restarts help in escaping from getting stuck in hard-to-prove sub-formulas. In practice, the choice of when and how often to restart is part of the strategy of a solver. When any number of restarts are allowed during search, we say that CL has *unlimited restarts*. For a recent investigation into the effect of restarts on the efficiency of clause learning DPLL algorithms, see [25].

Beame et al. [9] define CL-- as CL with branching allowed also on already assigned values. Although being non-typical in practice, this enables creating immediate conflicts at will. Although it is not known whether CL can simulate RES, it has been shown that this is true for CL-- using unlimited restarts.

**Theorem 3** ([9]) RES and CL-- with unlimited restarts and any non-redundant learning scheme are polynomially equivalent.

We note that the proof of this theorem in [9] relies on the fact that unit propagation is seen as applications of the unit clause rule, and hence the rule can also be left unapplied when convenient. This is non-typical for implementations of clause learning DPLL; they usually apply unit propagation eagerly whenever possible.

# 4 Relating CNF Proof Systems and Circuit Structure

A key element in this work is the tight correspondence between a constrained Boolean circuit  $\mathscr{C}^{\tau}$  and its CNF translation  $cnf(\mathscr{C}^{\tau})$ . In this section we review details on the correspondence of deduction in the CNF translation of a Boolean circuit with the original circuit structure, and on how branching in DPLL and CL can be restricted based on the original circuit structure. These details play an integral role in the theoretical results presented in the next section.

#### 4.1 Unit Propagation on the Level of Circuits

As there is a one-to-one relationship between the gates in a constrained Boolean circuit  $\mathcal{C}^{\tau}$  and the variables in the corresponding CNF formula  $cnf(\mathcal{C}^{\tau})$ , the variables can be thought to inherit the structural properties of the gates. For example, an *input variable* is a variable that corresponds to an input gate in the original Boolean circuit, and we will take the liberty of using the terms "gate" and "variable" synonymously. Furthermore, since the CNF translation in Table 1 encodes in a natural way the semantics of the gates, unit propagation in the CNF formula can be seen as working on the level of the circuit. A further discussion on this can

be found e.g. in [29], using a unit propagation equivalent characterization of Boolean constraint propagation as deduction rules for circuits [31]. Basically, such circuit level Boolean constraint propagation can set a value on a gate if and only if unit clause propagation can set a value on the corresponding Boolean variable in the CNF translation. For example, consider the gate  $g := \text{AND}(g_1, g_2)$  and its CNF translation  $(\neg \tilde{g} \lor \tilde{g}_1) \land (\neg \tilde{g} \lor \tilde{g}_2) \land (\tilde{g} \lor \neg \tilde{g}_1 \lor \neg \tilde{g}_2)$ . Now whenever the gate  $g_2$  is assigned to  $\mathbf{f}$ , the gate g can be propagated to  $\mathbf{f}$  by the semantics of AND. On the CNF level, we can equivalently propagate the variable  $\tilde{g}$  to  $\mathbf{f}$  by applying the unit clause rule whenever the variable  $\tilde{g}_2$  is assigned to  $\mathbf{f}$  through the clause  $(\neg \tilde{g} \lor \tilde{g}_2)$ . The same kind of equivalent behaviour is noticed in a "top-down" fashion when assigning the gate g to g to g to the circuit-level, the gates g and g can be propagated to g through the clauses g through the clause g to g through the clauses g through the clause g through the g through the g through the g through through through the g through the g through through through through through throu

Hence we will also take the liberty of saying that unit propagation sets a value on a gate when referring to unit propagation setting a value on the corresponding Boolean variable in the CNF translation. Similarly, we *branch on a gate* when referring to branching on the corresponding Boolean variable. Correspondingly, a DPLL or CL proof of a constrained circuit  $\mathcal{C}^{\tau}$  means a proof of the translation  $cnf(\mathcal{C}^{\tau})$ .

Since unit propagation can be also seen as Boolean constraint propagation on the level of constrained circuits, DPLL can also be implemented as a circuit level procedure, see, e.g., [38,31,35,46]. Since conflict graphs are based on how the unit clause rule is applied, clause learning can also be incorporated in such circuit level DPLL-based solvers [35,46]. Thus the results in this paper concerning the relative power of input-restricted clause learning DPLL hold for such circuit level approaches, too. Finally, we note that for instance [35] does not consider input-restricted branching but applies a top-down branching based on justification frontiers. The relative proof complexity theoretic power of the related top-down branching restrictions is analyzed in [29,28].

# 4.2 Restricting Branching in DPLL and CL to Inputs

In structured application domains of SAT solvers, such as automated planning and bounded model checking of hardware and software, the problem at hand is based on a transition relation, where the behavior of the underlying system is dependent solely on the *input* of the system. In the Boolean circuit encoding  $\mathscr{C}^{\tau}$  of such a structural problem, the input is represented by the set of input gates of the circuit, inputs( $\mathscr{C}$ ). Since the values of the other gates in the circuit can be evaluated when all the gates in inputs( $\mathscr{C}$ ) have values, branching in DPLL *with unit propagation* can be restricted to the variables associated with inputs( $\mathscr{C}$ ) without losing completeness. Intuitively, the idea is that since the number of input gates  $|\operatorname{inputs}(\mathscr{C})|$  is often much less than the total amount |G| of gates in  $\mathscr{C}$ , the search space size is reduced from  $2^{|G|}$  to  $2^{|\operatorname{inputs}(\mathscr{C})|}$ , where  $|\operatorname{inputs}(\mathscr{C})| \ll |G|$ .

By allowing branching in the DPLL and CL proof systems on input gates only, we arrive at the proof systems  $DPLL_{inputs}$  and  $CL_{inputs}$ , respectively. From the view of proof complexity, however, in [29] a formal study on the effect of restricting branching in DPLL (without clause learning) to inputs( $\mathscr{C}$ ) reveals that this weakens the proof system considerably.

# Theorem 4 ([29]) DPLL<sub>inputs</sub> cannot polynomially simulate DPLL.

In the following section, we investigate the proof complexity theoretic effect of inputrestricted branching in the context of *clause learning* DPLL-based SAT solving, which is posed as an open question in [29]. In Section 6 we complement this theoretical study by providing an experimental evaluation of the effect of input-restricted branching.

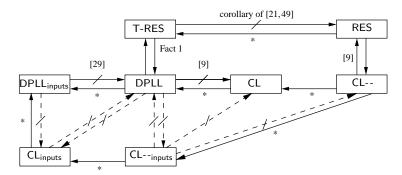

# 5 Restricted Branching and Proof Complexity

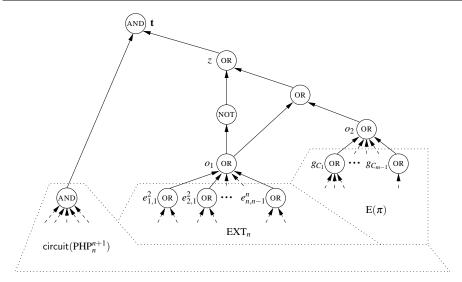

We will now consider the relative proof complexity theoretic power of input-restricted and unrestricted branching CL and DPLL. This will result in the refined relative efficiency hierarchy of DPLL and CL shown in Figure 4. An arrow without a slash from system S to S' means that S can polynomially simulate S', and with a slash that S cannot simulate S'. Arrows labeled with a \* are due to trivial subsumption. The new results, detailed in the following, are represented by dashed arrows. The missing arrows, disregarding those implied by the transitivity of the results, represent questions which are open to the best of our knowledge.

Fig. 4 A refined relative efficiency hierarchy for the proof systems considered in this work.

The main result of this paper is characterized by the following theorem.

**Theorem 5** DPLL and CL--inputs (with or without restarts) are incomparable.

This is a direct corollary of the forthcoming Lemmas 1 and 3. Thus we get the following as a direct corollary.

Corollary 2 CL--inputs with unlimited restarts cannot polynomially simulate CL.

We now proceed by proving Theorem 5 in two parts. First we show by a simple argument why DPLL cannot simulate CL<sub>inputs</sub>. We then discuss further the difference between CL<sub>inputs</sub> and DPLL<sub>inputs</sub> by exhibiting an example of a family of Boolean circuits on which CL<sub>inputs</sub> can simulate CL, while DPLL<sub>inputs</sub> cannot simulate DPLL. The motivation here is two-fold. On one hand, this shows the power of clause learning even when branching is restricted to inputs. On the other hand, the example gives an intuitive explanation of why the result in [29] on the power of DPLL<sub>inputs</sub> with respect to DPLL cannot be directly adapted for proving the analogous result for CL<sub>inputs</sub>. Although CL<sub>inputs</sub> can simulate CL on this particular family of circuits, this is not the case in general for other families. After the example, we proceed by showing that in fact, CL--<sub>inputs</sub>, even with conflict-driven backjumping and unlimited restarts, cannot even simulate DPLL. The proof relies on so called *redundant gates*, and applies known results on the very powerful *Extended Resolution* proof system [47].

#### 5.1 DPLL Cannot Simulate CL<sub>inputs</sub>

We now show that DPLL cannot simulate CL<sub>inputs</sub>. This results from the fact that DPLL cannot simulate CL by additionally noticing that CL and CL<sub>inputs</sub> are equivalent when considering circuits representing CNF formulas.

**Lemma 1** There is an infinite family of constrained Boolean circuits for which DPLL has superpolynomially longer minimum proofs than CL<sub>inputs</sub>.

*Proof* Take any infinite family  $\{F_n\}$  of CNF formulas that is a witness of Corollary 1 stating that DPLL cannot simulate CL. Define the family of Boolean circuits  $\{\operatorname{circuit}(F) \mid F \in \{F_n\}\}$ . The simplified CNF formula resulting from applying unit propagation to  $\operatorname{cnf}(\operatorname{circuit}(F))$  is effectively the same as the simplified CNF formula resulting from applying unit propagation to F; especially, the OR-gate variables in  $\operatorname{cnf}(\operatorname{circuit}(F))$  that represent the clauses in F are all assigned to  $\mathbf{t}$ . Thus CL will only branch on the variables in  $\operatorname{cnf}(\operatorname{circuit}(F))$  that are associated with the input gates of  $\operatorname{circuit}(F)$  or their negations. Thus  $\operatorname{CL}_{\operatorname{inputs}}$  can simulate CL on  $\operatorname{cnf}(\operatorname{circuit}(F))$ , and the claim follows by Corollary 1.

As a direct corollary, we have

Corollary 3 Neither DPLL nor DPLLinputs can polynomially simulate CLinputs.

Before considering whether  $CL_{inputs}$  can simulate CL or DPLL, we next give a motivating example which illustrates why the results in [29] on the power of DPLL<sub>inputs</sub> with respect to DPLL cannot be directly adapted for proving the analogous result for  $CL_{inputs}$ .

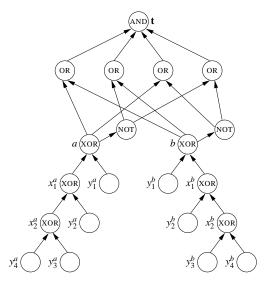

#### 5.2 A Further Motivating Example

To highlight the strength of clause learning even when branching is restricted to input gates, we now give an example of a family, {UNSAT-2PAR<sub>n</sub>} where  $n \ge 3$ , of Boolean circuits on which CL<sub>inputs</sub> can simulate CL applying the 1-UIP learning scheme, although DPLL<sub>inputs</sub> cannot simulate DPLL on the family. The circuit

$$UNSAT-2PAR_n := UNSAT \cup \langle PAR_n^a \cup PAR_n^b, \emptyset \rangle$$

consists of two parts:

- the constant size circuit

UNSAT := circuit

$$(\{\{a,b\},\{a,\neg b\},\{\neg a,b\},\{\neg a,\neg b\}\})$$

, and

– two copies (for a and b,  $\rho \in \{a,b\}$ ) of the circuit structure

$$\begin{split} \mathrm{PAR}_{n}^{\rho} := \big\{ \rho := \mathrm{XOR}(y_{1}^{\rho}, x_{1}^{\rho}) \big\} \cup \bigcup_{i=1}^{n-3} \big\{ x_{i}^{\rho} := \mathrm{XOR}(y_{i+1}^{\rho}, x_{i+1}^{\rho}) \big\} \cup \\ \big\{ x_{n-2}^{\rho} := \mathrm{XOR}(y_{n-1}^{\rho}, y_{n}^{\rho}) \big\}. \end{split}$$

Basically,  $PAR_n^{\rho}$  computes the parity of the *n* input gates  $y_1^{\rho}, \dots, y_n^{\rho}$ , evaluating to true if and only if an odd number of them are true.

**Fig. 5** The constrained Boolean circuit UNSAT-2PAR<sub>n</sub> for n = 4.

The circuit UNSAT-2PAR<sub>4</sub> is shown in Figure 5. Now, since unit propagation will result in a conflict in the UNSAT sub-circuit for any value of the gate a, UNSAT-2PAR<sub>n</sub> yields a trivial (constant length) proof in DPLL. It is also easy to see that minimum length proofs of UNSAT-2PAR<sub>n</sub> are exponential with respect to n in DPLL<sub>inputs</sub>. This is because, due to the structure of PAR<sub>n</sub><sup> $\rho$ </sup>, in order to propagate a value for the gate a or b, DPLL<sub>inputs</sub> has to branch on all of the inputs in the corresponding PAR<sub>n</sub><sup> $\rho$ </sup> sub-circuit. With the chronological backtracking process of DPLL this implies that minimum length DPLL<sub>inputs</sub> proofs of UNSAT-2PAR<sub>n</sub> are exponential with respect to n.

However,  $CL_{inputs}$  can produce linear length proofs on the family. In the following we will say that CL (or DPLL) branches according to a sequence of assignments  $(x_1 = v_1, x_2 = v_2, ...)$ , if it always branches by assigning the value to the variable given by the next assignment in the sequence, i.e., we would first branch by assigning  $x_1$  the value  $v_1$ , and so forth. Now, let  $CL_{inputs}$  branch according to the sequence  $(y_1^a = \mathbf{f}, ..., y_{n-1}^a = \mathbf{f})$ . After this, unit propagation cannot still propagate a value on the gate a, any of the  $x_i^a$  gates, or any gate in the UNSAT sub-circuit. Then branch with  $y_n^a = \mathbf{f}$ . Now unit propagation sets values for all  $x_i^a$  gates without a conflict. The values for  $x_1^a$  and  $y_1^a$  propagate the value  $\mathbf{f}$  for a, which then propagates a conflict at a gate in UNSAT. Notice that  $x_1^a$  and  $y_1^a$  are the *only* reasons for the value of a. In *any* conflict graph associated with the branching sequence  $(y_1^a = \mathbf{f}, ..., y_n^a = \mathbf{f})$ ,  $\neg a$  is a 1-UIP, and, furthermore, constitutes a reason for the conflict on its own. Hence  $CL_{inputs}$  can learn as a unit clause the opposite value of a, and backjump to the decision level zero. This opposite value will then propagate a conflict without branching, and  $CL_{inputs}$  terminates.

It is interesting to notice how  $CL_{inputs}$  can branch on  $(y_1^a = \mathbf{f}, \dots, y_n^a = \mathbf{f})$  and still avoid backtracking on these decisions since there is the *bottleneck* at gate a due to the construction of UNSAT-2PAR<sub>n</sub>. This shows the strength of clause learning with conflict-driven backjumping—even with input-restricted branching—due to its ability to backjump over an exponential size search space by detecting small locally inconsistent sub-formulas. With

this intuition, it is evident that the results in [29] on the power of DPLL<sub>inputs</sub> with respect to DPLL cannot be directly adapted for proving the analogous result for CL<sub>inputs</sub>.

# 5.3 CL--inputs Cannot Simulate DPLL

Although  $CL_{inputs}$  can simulate CL on the  $\{UNSAT-2PAR_n\}$  family, this is generally not the case for other families. In fact, it turns out that CL--inputs cannot even simulate DPLL, as detailed next.

We will apply the concept of redundant gates in constrained Boolean circuits.

**Definition 3** A gate in a constrained Boolean circuit  $\mathscr{C}^{\tau}$  is *redundant* if it is unconstrained and not a descendant of any constrained gate.

We will assume that circuits do not contain redundant input gates; such inputs can always be assigned an arbitrary truth value without affecting satisfiability. As shown next, when considering CL--<sub>inputs</sub>, redundant gates cannot appear in conflict graphs. Intuitively, this is because redundant gates can only have a value due to unit propagation "upwards" (from child to parent) on the circuit structure in CL--<sub>inputs</sub>; as they, or any of their parents, are not constrained by definition, they cannot cause a conflict or be a part of a unit propagation chain responsible for a conflict. As a consequence of this, redundant gates can never appear in conflict clauses derived by CL--<sub>inputs</sub>.

**Lemma 2** Let  $\mathcal{C}^{\tau}$  be an arbitrary constrained Boolean circuit. Considering CL--inputs on input cnf( $\mathcal{C}^{\tau}$ ), redundant gates do not occur in any conflict graph at any stage of CL--inputs. This holds whether or not restarts are allowed.

*Proof* Take any constrained Boolean circuit  $\mathscr{C}^{\tau}$ . The stages in which CL-- $_{inputs}$  does not have a conflict are trivial. Now assume that the lemma holds at a stage where CL-- $_{inputs}$  has made m conflicts. Consider the stage producing the (m+1)th conflict and any conflict graph associated with the conflict. We next show that the conflict graph contains no redundant gates. Take any redundant gate g in  $\mathscr{C}^{\tau}$ . If it is not assigned, it cannot appear in the conflict graph. Now assume that g is assigned. Since g is redundant, it cannot be constrained by  $\tau$ . Furthermore, g is not an input gate (by the assumption we made above), and thus g is assigned not because it was branched on. Therefore, g has been assigned by unit propagation. Now there are three cases.

- By the induction hypothesis, there are no known learned clauses containing redundant gates before the (m+1)th conflict, and therefore g is not assigned by unit propagation on a learned clause.

- The gate g is assigned because some of its children are assigned, i.e., by unit propagation on one of the clauses in  $cnf(\mathscr{C}^{\tau})$  resulting from the equality  $g \Leftrightarrow f(g_1, \ldots, g_n)$ . Once g becomes assigned in this way, all these clauses become satisfied. Therefore, the value assigned to g by unit propagation could not have caused any of the children of g to be assigned.

- The gate g is assigned due to an assigned value on a parent g' of g, i.e., by unit propagation on one of the clauses in  $cnf(\mathscr{C}^{\tau})$  resulting from the equality  $g' \Leftrightarrow f(\ldots,g,\ldots)$ . Since g is redundant, g' is also redundant. By the arguments above, the only way for g' to have been assigned in this situation is due to one of its parents' assigned value. Inductively, this leads to the fact that a redundant output gate o should have been assigned by unit propagation because one of o's parents has been assigned. This is a contradiction,

since output gates have no parents. Therefore, the redundant gate g cannot be assigned because one of its parents is assigned.

Hence, the only reason for a redundant gate to be assigned is that some of its children are assigned. Furthermore, the value of an assigned redundant gate can only propagate values to its parents (which are also redundant). On the other hand, since redundant gates are not constrained by  $\tau$ , g cannot act as the conflict variable in the conflict graph. Therefore, there cannot be any path from g to the conflict node in the implication graph which the conflict graph is based on. This proves that a redundant gate cannot occur in the conflict graph.

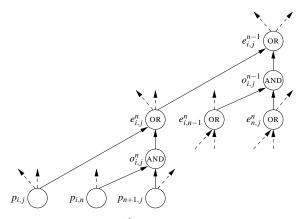

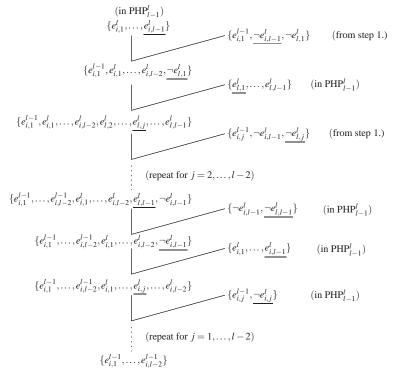

Although redundant gates can be removed from any constrained Boolean circuit without affecting its satisfiability, they may have an effect on the length of shortest proofs. Cook [12] gives a way of introducing a polynomial number of clauses which can be interpreted as redundant gates to circuit(PHP<sub>n</sub><sup>n+1</sup>) so that, contrarily to circuit(PHP<sub>n</sub><sup>n+1</sup>), the extended circuit yields polynomial length proofs in RES. As a circuit structure, this *extension* is defined as  $EXT_n := \bigcup_{l=3}^{n+1} EXT^l$ , where

$$\mathrm{EXT}^l := \bigcup_{i=1}^{l-1} \bigcup_{i=1}^{l-2} \left\{ o_{i,j}^{l-1} := \mathrm{AND}(e_{i,l-1}^l, e_{l,j}^l), \ e_{i,j}^{l-1} := \mathrm{OR}(e_{i,j}^l, o_{i,j}^{l-1}) \right\},$$

and each  $e_{i,j}^{n+1}$  is the gate  $p_{i,j}$  in circuit(PHP $_n^{n+1}$ ). A part of EXT $_n$  is illustrated in Figure 6. The output gates of EXT $_n$  are  $e_{1,1}^2$  and  $e_{2,1}^2, e_{3,2}^3, \ldots, e_{n,n-1}^n$ .

**Fig. 6** Part of Cook's extension  $EXT_n$  to  $PHP_n^{n+1}$  as a circuit.

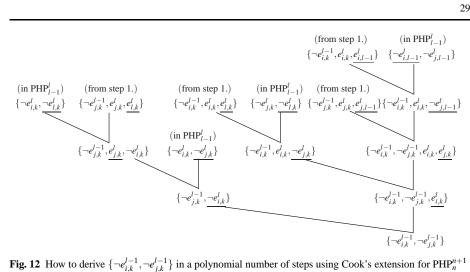

Due to the result in [12], we immediately have a polynomial length RES proof  $\pi = (C_1, \dots, C_m = \emptyset)$  of the extended PHP $_n^{n+1}$  formula cnf(circuit(PHP $_n^{n+1}$ )  $\cup$  (EXT $_n$ ,  $\emptyset$ ). Intuitively, EXT $^l$  allows reducing PHP $_l^{l+1}$  to PHP $_{l-1}^l$  with a polynomial number of resolution steps. However, since in [12] such a proof is not given explicitly, we include a detailed description of the proof in Appendix A. For the following, what is most important is that such a short proof  $\pi$  exists, not really the actual details of  $\pi$ . The details of  $\pi$ , along with EXT $_n$ , are included here for the sake of concreteness and illustration.

<sup>&</sup>lt;sup>1</sup> See remark 6 in Section 5.4 for more details.

Using the above-described polynomial length RES proof  $\pi = (C_1, C_2, ..., C_m = \emptyset)$  for  $cnf(circuit(PHP_n^{n+1}) \cup \langle EXT_n, \emptyset \rangle)$ , we define the circuit construct

$$\begin{split} \mathbf{E}(\pi) := \bigcup_{i=1}^{m-1} \left\{ g_{C_i} := \mathrm{OR}(g_1, \dots, g_j, \hat{g}_{j+1}, \dots, \hat{g}_k) \mid C_i = \{ \tilde{g}_1, \dots, \tilde{g}_j, \neg \tilde{g}_{j+1}, \dots, \neg \tilde{g}_k \} \right\} \cup \\ & \bigcup_{i=1}^{m-1} \left\{ \hat{g} := \mathrm{NOT}(g) \mid \tilde{g} \in \mathsf{vars}^-(C_i) \right\}. \end{split}$$

That is, each clause  $C_i$  in the RES proof  $\pi$  is simply represented as a corresponding OR-gate. This allows a simple polynomial length DPLL proof of

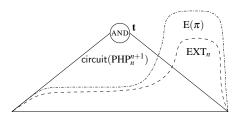

$$\mathsf{EPHP}_n^{n+1} := \mathsf{circuit}(\mathsf{PHP}_n^{n+1}) \cup \langle \mathsf{EXT}_n, \emptyset \rangle \cup \langle \mathsf{E}(\pi), \emptyset \rangle,$$

while there is no polynomial length proof of EPHP<sub>n</sub><sup>n+1</sup> in CL--<sub>inputs</sub>. Intuitively this is because E( $\pi$ ) allows DPLL to "verify" the resolution proof of PHP<sub>n</sub><sup>n+1</sup> extended with EXT<sub>n</sub> step-by-step, while CL--<sub>inputs</sub> cannot make use of the redundant gates of EXT<sub>n</sub> and E( $\pi$ ). For a high-level view of the structure of EPHP<sub>n</sub><sup>n+1</sup>, see Figure 7.

**Fig. 7** High-level view of EPHP $_n^{n+1}$ .

**Lemma 3** For the infinite family  $\{EPHP_n^{n+1}\}$  of constrained Boolean circuits, CL--inputs with unlimited restarts has superpolynomially longer minimum-length proofs than DPLL.

*Proof* A polynomial length DPLL proof of EPHP<sub>n</sub><sup>n+1</sup> is witnessed by the branching sequence  $(g_{C_1} = \mathbf{f}, g_{C_2} = \mathbf{f}, \dots, g_{C_{m-1}} = \mathbf{f})$ , as detailed next. By induction on i, we will show that, if  $g_{C_1} = \mathbf{t}, \dots, g_{C_{i-1}} = \mathbf{t}$ , then branching with  $g_{C_i} = \mathbf{f}$  results in a conflict by unit propagation, and hence immediately sets  $g_{C_i} = \mathbf{t}$ .

The base case. The gate  $g_{C_1}$  represents the first clause  $C_1$  in  $\pi$ , and thus  $C_1$  must belong to  $\operatorname{cnf}(\operatorname{circuit}(\operatorname{PHP}_n^{n+1}) \cup \langle \operatorname{EXT}_n, \emptyset \rangle)$ . As  $C_1$  is a result of applying the cnf translation to a gate g in  $\operatorname{circuit}(\operatorname{PHP}_n^{n+1}) \cup \langle \operatorname{EXT}_n, \emptyset \rangle$  (which is part of  $\operatorname{EPHP}_n^{n+1}$ ), setting  $g_{C_1} = \mathbf{f}$  will result in a conflict after unit propagation because the functional definition or the constraint of the gate g is violated. For example, if  $g := \operatorname{OR}(g_1, g_2)$  and  $C_1 = (\tilde{g} \vee \neg \tilde{g}_1)$ , then  $g_{C_1} := \operatorname{OR}(g, \hat{g}_1)$  with  $\hat{g}_1 := \operatorname{NOT}(g_1)$ , and the assignment  $g_{C_1} = \mathbf{f}$  will propagate  $g = \mathbf{f}$  and  $g_1 = \mathbf{t}$ , violating the definition of g and thus resulting in a conflict.

Now assume as the induction hypothesis that we have  $g_{C_i'} = \mathbf{t}$  for all  $1 \le i' < i$ . Next branch with  $g_{C_i} = \mathbf{f}$ . If the *i*th clause  $C_i$  in  $\pi$  belongs to  $\operatorname{cnf}(\operatorname{circuit}(\operatorname{PHP}_n^{n+1}) \cup \langle \operatorname{EXT}_n, \emptyset \rangle)$ , branching on  $g_{C_i} = \mathbf{f}$  will result in a conflict after unit propagation as in the base case. Otherwise  $C_i$  has been derived from two clauses,  $C_j = C'_j \cup \{\tilde{g}\}$  and  $C_k = C'_k \cup \{\neg \tilde{g}\}$ , in  $\pi$  for  $1 \le j, k < i$ , by resolving on the variable  $\tilde{g}$ . By the induction hypothesis we have  $g_{C_j} = \mathbf{t}$

and  $g_{C_k} = \mathbf{t}$ . On the other hand, as  $g_{C_i} = \mathbf{f}$ , all the gates corresponding to the literals in  $C'_j \cup C'_k$  are assigned to  $\mathbf{f}$  by unit propagation, implying that unit propagation will assign both  $g = \mathbf{t}$  and  $g = \mathbf{f}$  as  $g_{C_j} = g_{C_k} = \mathbf{t}$ . Thus a conflict is reached, closing the branch  $g_{C_i} = \mathbf{f}$ , and  $g_{C_i} = \mathbf{t}$  is set by backtracking.

Finally, since  $C_m = \emptyset \in \pi$ , there are unit clauses  $C_j = \{\tilde{g}\}$  and  $C_k = \{\neg \tilde{g}\}$  in  $\pi$ , where  $1 \le j, k < m$ . Without loss of generality, assume that j < k. By induction, at latest after branching with  $g_{C_k} = \mathbf{f}$  and setting  $g_{C_k} = \mathbf{t}$  by backtracking, we will have  $g_{C_j} = g_{C_k} = \mathbf{t}$  in the branch, and thus both  $g = \mathbf{t}$  and  $g = \mathbf{f}$ , a conflict. This closes the last branch, and we have a linear size DPLL proof of EPHP<sub>n</sub><sup>n+1</sup>.

Now consider proofs of  $\mathrm{EPHP}_n^{n+1}$  in  $\mathrm{CL-}_{\mathsf{inputs}}$ . The non-input gates in  $\langle \mathrm{EXT}_n,\emptyset \rangle \cup \langle \mathrm{E}(\pi),\emptyset \rangle$  are all redundant in  $\mathrm{EPHP}_n^{n+1}$ , and they cannot be part of a reason for any conflict in  $\mathrm{CL-}_{\mathsf{inputs}}$  (Lemma 2). Thus any  $\mathrm{CL-}_{\mathsf{inputs}}$  proof of  $\mathrm{EPHP}_n^{n+1}$  contains a  $\mathrm{CL-}_{\mathsf{inputs}}$  proof of  $\mathrm{PHP}_n^{n+1}$ , which cannot be of polynomial length (Theorems 1 and 3).

Theorem 5 now follows directly from Lemmas 1 and 3.

#### 5.4 Additional Remarks

Closely related to Lemma 3 and the applied construction  $EPHP_n^{n+1}$ , we make the following additional remarks.

- Due to the fact that redundant gates do not occur in any conflict graph of CL--inputs, Lemma 3 covers all clause learning schemes based on conflict cuts, including, for example, schemes which learn multiple clauses at each conflict [39]. Additionally, conflict clause forgetting schemes, which are applied in typical clause learning solvers such as [18], do not affect this result.

- 2. We use redundant gates in the EPHP<sub>n</sub><sup>n+1</sup> construction for simplicity of the proof of Lemma 3; by a simple modification of EPHP<sub>n</sub><sup>n+1</sup> one can construct as a witness for Lemma 3 a constrained circuit with no redundant gates and a single output as the only constrained gate. The basic idea, illustrated in Figure 8, is to make a small local change to the EPHP<sub>n</sub><sup>n+1</sup> circuit construct. In more detail, introduce the OR-gate  $o_1$  over the output gates  $e_{1,1}^2, e_{2,1}^2, \dots, e_{n,n-1}^n$  in EXT<sub>n</sub>. Similarly, introduce the OR-gate  $o_2$  over the output gates  $g_{C_1}, \dots, g_{C_{m-1}}$  in E( $\pi$ ). Now, introduce an OR-gate over  $o_1$  and  $o_2$ . Then, introduce a gate z that is the OR of this gate and a new gate NOT( $o_1$ ). Finally, constrain the AND of this gate and the output gate of the unconstrained version of circuit(PHP<sub>n</sub><sup>n+1</sup>) to **t**. The resulting circuit family can be used in proving Lemma 3 as the values propagated to the non-input gates in EXT<sub>n</sub> and E( $\pi$ ) cannot be part of any conflict graph in CL--inputs. This is because the gate z always evaluates to **t**; it corresponds to a tautology of form  $\neg a \lor (a \lor b)$  and thus effectively makes EXT<sub>n</sub> and E( $\pi$ ) redundant.

- 3. Since redundant gates can be removed from constrained Boolean circuits without affecting the existence of satisfying assignments, such gates are typically removed in practice before the CNF translation and SAT solving by using the so-called *cone-of-influence reduction* [31]. However, applying the cone-of-influence reduction can have a drastic negative effect on minimum length proofs: if one applies the cone-of-influence reduction to the circuit family EPHP<sub>n</sub><sup>n+1</sup>, one obtains the family PHP<sub>n</sub><sup>n+1</sup> for which CL-- does not have polynomial length proofs although the much weaker system DPLL has short proofs for the original family EPHP<sub>n</sub><sup>n+1</sup> (as shown in the proof of Lemma 3).

- 4. It is interesting to notice that DPLL solvers with full one-step lookahead can detect the small proofs of  $\text{EPHP}_n^{n+1}$  witnessed by the branching sequence  $(g_{C_1} = \mathbf{f}, g_{C_2} =$

**Fig. 8** Local change to the EPHP<sub>n</sub><sup>n+1</sup> circuit for removing redundancy of gates in  $E(\pi)$  and  $EXT_n$

- $\mathbf{f}, \dots, g_{C_{m-1}} = \mathbf{f}$ ). In particular, for each i, lookahead on  $g_{C_i} = \mathbf{f}$  when having  $g_{C_j} = \mathbf{t}$  for all j < i in the branch will result in an immediate conflict using unit propagation, as detailed in the proof of Lemma 3.

- 5. The Cook's extension (a variant of EXT<sub>n</sub>) presented in [12] is motivated by investigations into the power of the *Extended Resolution proof system* defined by Tseitin [47]. Extended Resolution is the result of adding an *extension rule* to RES, which allows for iteratively adding *definitions* of the form  $x \Leftrightarrow l_1 \land l_2$  (or, as a set of clauses,  $\{\{x, \neg l_1, \neg l_2\}, \{\neg x, l_1\}, \{\neg x, l_2\}\}$ ) to the CNF formula, where x is a new variable and  $l_1, l_2$  are literals in the current formula. This is equivalent to adding a redundant binary AND gate of the literals  $l_1, l_2$  to a constrained Boolean circuit. Notably, it is known that Extended Resolution is among the most powerful proof systems, and can simulate, e.g., *Frege systems* (see [34] for more details).

- 6. Instead of the pigeon-hole problem PHP<sub>n</sub><sup>n+1</sup>, Cook's extension EXT<sub>n</sub> to it, and the resolution proof  $\pi$  of their combination, one could use any CNF formula F that (i) does not have a polynomial size resolution proof but (ii) has a polynomial size extended resolution proof to prove a result similar to Lemma 3. That is, for such formula F, DPLL has a polynomial sized proof of circuit(F)  $\cup$   $\langle$ EXT<sub>F</sub>, $\emptyset$  $\rangle$   $\cup$   $\langle$ E( $\pi_F$ ), $\emptyset$  $\rangle$  while CL--inputs does not, where EXT<sub>F</sub> is the polynomial sized extension of F and  $\pi_F$  is a polynomial sized resolution proof of cnf(circuit(F)  $\cup$   $\langle$ EXT<sub>F</sub>, $\emptyset$  $\rangle$ ).

- 7. The additional extension  $E(\pi)$  applied above is motivated by a similar construction which can be used for simulating *Frege proofs* with their tree-like variants (see [34, Chapter 4]).

# 6 Experiments

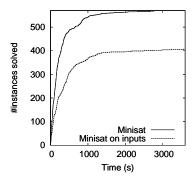

We evaluate the effect of restricting branching to input variables on the functionality of modern clause learning solver techniques. The set of benchmarks<sup>2</sup> used in the experiments consists of instances from various application domains, for which Boolean circuits offer a natural representation form: super-scalar processor verification [50], integer factorization based on hardware multipliers [43], equivalence checking of hardware multipliers [26], bounded model checking (BMC) for deadlocks in asynchronous parallel systems represented as labelled transition systems (LTS) [32], and linear temporal logic (LTL) BMC of finite state systems with a compact encoding [36]. We use standard PCs with 2-GHz AMD 3200+ processors and two gigabytes of memory running Linux, and apply a timeout of one hour and a memory limit of one gigabyte to each SAT solver execution.

For solving the Boolean circuit instances, we apply BCMinisat<sup>3</sup> (version 0.26), which we have modified in order to restrict branching to input variables. BCMinisat is a Boolean circuit front-end for the successful clause learning SAT solver Minisat [18] (version 1.14). BCMinisat accepts as input Boolean circuits with various Boolean functions allowed as gate types, performs circuit-level preprocessing, including Boolean propagation, substructure sharing, and cone-of-influence reductions to the circuit, normalizing the circuit into a form which can be translated into CNF applying a standard translation in the style of cnf defined in Table 1. BCMinisat feeds the resulting CNF translation and the input-restriction to Minisat, which then solves the CNF. For each circuit, we obtain 15 CNF instances by permuting the CNF variable numbering.

Minisat implements 1-UIP clause learning. After each conflict the heuristic value of each variable on the conflict side and in the conflict clause is incremented by one, and the values of all variables are decremented by 5%. To avoid hindering efficiency by learning massive amounts of clauses, the solver also uses a scheme for forgetting learned clauses that have not occurred on the conflict side in recent conflicts.

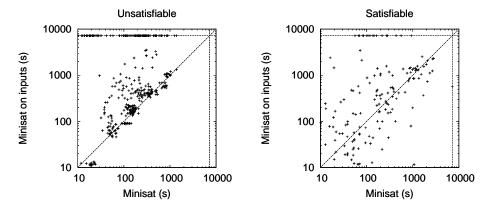

#### 6.1 Results

Table 2 gives the minimum, median, and maximum number of decisions for BCMinisat and input-restricted BCMinisat (BCMinisat<sub>inputs</sub>) for each benchmark instance. For the instances based on hardware multiplication designs, for which the number of unassigned input variables is 2% or less out of all unassigned variables, BCMinisat<sub>inputs</sub> shows an advantage over BCMinisat with respect to the number of decisions. However, for the hardware verification and BMC instances, the overall performance of BCMinisat<sub>inputs</sub> is much worse, with timeouts on all verification and half of the LTL BMC instances. The possible gains of applying input-restricted branching seem to correlate with a very low relative number of input variables. On the equivalence checking instances, we notice that the number of decision for BCMinisat<sub>inputs</sub> is more than the brute-force upper bound, e.g., for eq-test.atree.braun.10 around  $1.4 - 1.8 \times 10^6$ , compared to the brute-force bound  $2^{20} \approx 1.0 \times 10^6$ . Considering that we are using a state-of-the-art clause learning solver, this surprising result is likely due to conflict clause forgetting <sup>4</sup>; when forgetting a conflict clause C, the solver may have to re-examine the search space characterised as unsatisfiable by C.

<sup>&</sup>lt;sup>2</sup> The set of Boolean circuit benchmarks is available at http://www.tcs.hut.fi/~mjj/benchmarks/.

<sup>&</sup>lt;sup>3</sup> Part of the BCTools package, http://www.tcs.hut.fi/~tjunttil/bcsat/.

<sup>&</sup>lt;sup>4</sup> For more evidence corroborating this claim, see [30].

**Table 2** Minimum (**min**), median (**med**), and maximum (**max**) of number of decisions for BCMinisat and BCMinisat<sub>inputs</sub>, with number of timeouts in parenthesis. The **sat** column gives the satisfiability of the instance, and #inputs gives the number of unassigned input variables in the CNF translation (percentage in parentheses). For **ud** and **bb**, see the text body.

|                                           |     |              | Number of decisions |          |         |         |         |         |       |      |  |

|-------------------------------------------|-----|--------------|---------------------|----------|---------|---------|---------|---------|-------|------|--|

|                                           |     |              |                     | 3CMinisa | at      | BC      | -       |         |       |      |  |

| Instance                                  | sat | #inputs      | min                 | med      | max     | min     | med     | max     | ud    | bb   |  |

| Super-scalar processor verification       |     |              |                     |          |         |         |         |         |       |      |  |

| fvp.2.0.3pipe.1                           | no  | 186 (8.2)    | 61531               | 384386   | 1225134 | - (15)  | - (15)  | - (15)  | -     | -    |  |

| fvp.2.0.3pipe_2_ooo.1                     | no  | 305 (11.7)   | 75962               | 184798   | 426489  | - (15)  | - (15)  | - (15)  | -     | -    |  |

| fvp.2.0.4pipe_1_ooo.1                     | no  | 544 (10.4)   | 188992              | 209048   | 271982  | - (15)  | - (15)  | - (15)  | -     | -    |  |

| fvp.2.0.4pipe_2_ooo.1                     | no  | 547 (9.8)    | 1033607             | 2094617  | 5241781 | - (15)  | - (15)  | - (15)  | -     | -    |  |

| fvp.2.0.5pipe_1_000.1                     | no  | 845 (8.9)    | 336281              | 746231   | 1838599 | - (15)  | - (15)  | - (15)  |       | -    |  |

| Equivalence checking hardware multipliers |     |              |                     |          |         |         |         |         |       |      |  |

| eq-test.atree.braun.8                     | no  | 16 (2.3)     | 180449              | 285665   | 339805  | 65785   | 73834   | 82372   | 88.5  | 0.02 |  |

| eq-test.atree.braun.9                     | no  | 18 (2.0)     | 898917              | 1055511  | 1317785 | 323688  | 385398  | 389890  | 106.6 | 0.02 |  |

| eq-test.atree.braun.10                    | no  | 20 (1.8)     | 3755375             | 4540598  | 5089443 | 1428957 | 1590390 | 1787295 | 127.9 | 0.01 |  |

| Integer factorisation                     |     |              |                     |          |         |         |         |         |       |      |  |

| atree.sat.34.0                            | yes | 60 (0.6)     | 156733              | 228792   | 761620  | 24820   | 208880  | 277896  | 21.9  | 0.04 |  |

| atree.sat.36.50                           | yes | 64 (0.6)     | 251218              | 721474   | 937152  | 316590  | 571533  | 788762  | 18.4  | 0.04 |  |

| atree.sat.38.100                          | yes | 68 (0.6)     | 284980              | 1095192  | - (1)   | 190330  | 498092  | 1082729 | -     | -    |  |

| atree.unsat.32.0                          | no  | 57 (0.7)     | 141419              | 163508   | 180973  | 123502  | 138797  | 162546  | 15.3  | 0.04 |  |

| atree.unsat.34.50                         | no  | 60 (0.6)     | 248371              | 287351   | 404418  | 223130  | 244382  | 301464  | 18.0  | 0.04 |  |

| atree.unsat.36.100                        | no  | 64 (0.6)     | 527237              | 623889   | 915810  | 431576  | 480469  | 578331  | 19.4  | 0.03 |  |

| braun.sat.32.0                            | yes | 61 (2.2)     | 27480               | 82122    | 140150  | 5675    | 81269   | 135093  | 25.6  | 0.05 |  |

| braun.sat.34.50                           | yes | 65 (2.1)     | 30717               | 152224   | 353464  | 43924   | 110614  | 223306  | 25.3  | 0.05 |  |

| braun.sat.36.100                          | yes | 69 (2.0)     | 129771              | 447716   | 589449  | 86134   | 374884  | 752645  | 19.4  | 0.05 |  |

| braun.unsat.32.0                          | no  | 60 (2.2)     | 107617              | 122550   | 156004  | 96894   | 119437  | 150121  | 10.4  | 0.06 |  |