# Wirelessly Powered Sensor Transponder for UHF RFID

In: Proceedings of Transducers & Eurosensors'07 Conference. Lyon, France, June 10–14, 2007, pp. 73–76. © 2007 IEEE. Reprinted with permission from the publisher.

This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of the VTT Technical Research Centre of Finland's products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org.

## WIRELESSLY POWERED SENSOR TRANSPONDER FOR UHF RFID

P. Pursula, J. Marjonen, H. Ronkainen and K. Jaakkola

VTT Technical Research Centre of Finland Espoo, FINLAND (email: pekka.pursula@vtt.fi)

**Abstract:** A transponder for UHF RFID with sensor interface for external capacitive sensors is described. The sensor interface consists of a capacitive voltage divider and a 10 bit successive approximation analog to digital converter. The power consumption is about 30  $\mu$ W<sub>DC</sub> and the transponder is wirelessly powered with RF waves from the reader device. Wireless measurement of capacitance is demonstrated at a distance of 30 cm with 0.5 W erp transmission power. Low operation distance is mostly due to low efficiency of the rectifying Schottky-diodes in the particular BiCMOS process.

Keywords: UHF RFID, sensor.

# **1. INTRODUCTION**

One of the most modern applications of the RF technology is a radio frequency identification (RFID) transponder operating at ultra high frequencies (UHF). A passive transponder gets its power supply from the radiation field of the reading device by RF/DC rectification. Understandingly, the electronics of the transponder must consume power as little as possible, in order of microwatts.

Passive transponders have been used for sensing for a long time: In [1] a passive temperature sensor in the UHF with analog data transfer is described as early as 1987. Recently, more sophisticated sensor transponders with integrated sensors and digital communication have been reported (e.g. [2]). In this paper a passive sensor transponder with digital communication and an interface for an external capacitive sensor is described.

# 2. FUNCTIONAL DESCRIPTION

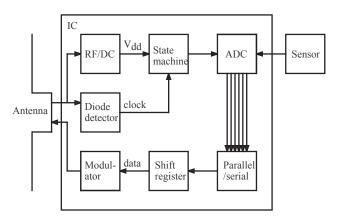

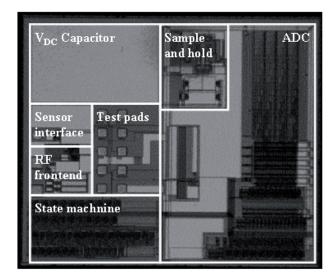

The transponder chip consists of three functional blocks: RF frontend, state machine and analog to digital converter (ADC). The chip was processed with MAS 1,5  $\mu$ m BiCMOS process to an area of 2.5 \* 3.0 mm<sup>2</sup>. The chip schematic is presented in Fig. 1 and the photograph in Fig. 2.

Figure 1: Block diagram of the wireless sensor transponder.

Figure 2: Photograph of the IC chip.

#### 2.1 RF front end

The operating power for the chip is generated by a six diode Schottky ladder followed by a regulator. The RF frontend includes also a diode detector for reader-to-transponder communication. The reader sends clock to the transponder by pulse interval encoding and amplitude modulation, keeping the reader and transponder all the time synchronized [3]. A storage capacitor of several hundred pF is used to provide power for the chip for the short intervals (<10  $\mu$ s), when RF power from the reader is off due to the modulation.

Communication from the tag to the reader is based on backscattering. The transponder IC modulates its input impedance with a switched capacitor to modulate the radiation scattered from the antenna. Phase modulation of about 35 degrees is achieved.

### 2.2. State machine

Communication protocol of the sensor system is extremely simplified. The transponder goes through a preprogrammed loop, whenever it gets enough power from the rectifier and a power-onreset signal. The state machine creates control signals by counting the clock.

The transponder completes a new conversion approximately every 128 clock cycles, which means about 16 times a second with 10 kHz clock used when testing the system. While doing a new conversion, the previous conversion result is simultaneously transmitted to the reader.

## 2.3 Sensor interface

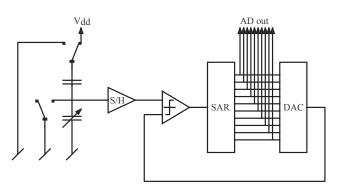

The analog to digital converter utilises a successive approximation register (SAR) architecture [4] with an offset voltage self-correction sample-and-hold circuit as a front-end [5]. The sensor interface is a capacitive voltage divider, which is charged for every sampling to avoid charge accumulation. The schematic of the ADC and the sensor interface is presented in Fig. 3.

## **3. MEASUREMENT RESULTS**

#### 3.1 RF front end

The rectifier power conversion efficiency  $\eta$  is defined as the ratio between output DC power  $P_{DC}$

Figure 3. Block diagram of the sensor interface and the SAR based ADC.

and RF power  $P_{in}$  going into the rectifier

$$\eta = \frac{P_{DC}}{P_{in}} = \frac{V_{DC}^2 / R_{DC}}{(1 - |\Gamma|^2) P_{RF}},$$

(1)

where  $V_{DC}$  is the output voltage,  $R_{DC}$  the load resistance,  $\Gamma$  reflection coefficient and  $P_{RF}$  input RF power from the analyser.

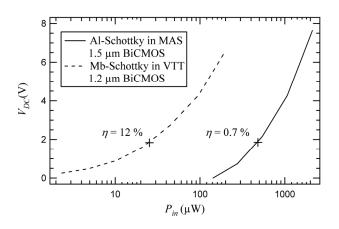

The rectifier in the chip has the power conversion efficiency of 0.7 % at output voltage of 1.8 V with a 1.1 M $\Omega$  load. In this chip aluminium metallisation was used for Schottky contact. A similar rectifier processed at VTT with Molybdenium Schottkies has efficiency of 12 %. The output voltages of the two rectifiers are presented as a function of ingoing RF power in Fig. 4.

Figure 4. Output voltage  $V_{DC}$  of the rectifier as a function of ingoing RF power  $P_{in}$  with a 1.1 M $\Omega$  load. The rectifier power conversion efficiencies at 1.8 V output voltage are written out.

## 3.2 Analog to digital converter

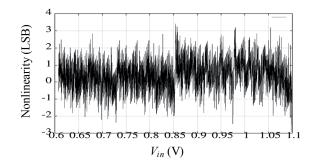

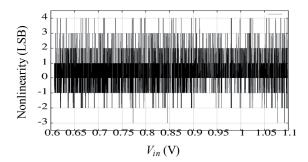

A separate DC measurement of the ADC yielded the integral (INL) and differential (DNL) nonlinearities to be 3.3 LSB and 4 LSB at 1.8 V, respectively. The nonlinearity measurement results are presented in Figs. 5 and 6. The equivalent number of bits estimated from INL was 8.28 bits. Both static nonlinearities, INL and DNL, can be explained by the low open loop gain of the comparator and by the prevailing noise.

Figure 5. The integral nonlinearity of the ADC vs. input voltage  $V_{in}$  at  $V_{dd} = 1.8 V$  [6]. © IEEE 2006.

Figure 6. The differential nonlinearity of the ADC vs. input voltage  $V_{in}$  at  $V_{dd} = 1.8 V [6]$ . © IEEE 2006.

A dynamic measurement was done also, in which a full-range 2 Hz sinusoidal signal was applied into the sample-and-hold (S/H) circuit input. Sampling frequency was 75 Hz. In dynamic measurement the signal to noise ratio (SNR) was 40 dB, and spurious free dynamic range (SFDR) 30 dB for 8 Hz sine. The result of the dynamic measurement was to some extent invalid, because the used signal source was not spectrically pure either, i.e. there were frequency components produced by the signal source at higher frequencies with power levels -40 dBc or lower. The measured stand-by power consumption was 2.3  $\mu$ W at 1.8 V, which met the specification.

## 3.3 Wireless measurement

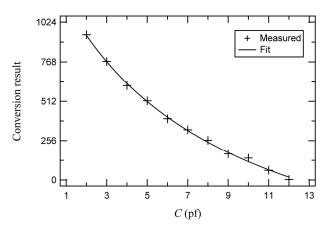

To demonstrate the chip functionality wirelessly, the chip was connected by wire bonding and a matching circuit to a  $\lambda/2$ -dipole (Fig. 7). The measurement was carried out at 869 MHz with transmit power 0.5 W erp. The conversion result as a function of the measured capacitance in the wireless measurement is presented in Fig. 8.

Figure 7. The demonstrator transponder. The IC chip (shiny rectangle) was wire bonded on a carrier, which was connected with a matching network to a  $\lambda/2$ -dipole. Above the chip, there is a connector for diagnostic outputs of the IC and a chip capacitor, which was measured.

Figure 8. The conversion result and theoretical fit as a function of capacitance C in a wireless measurement.

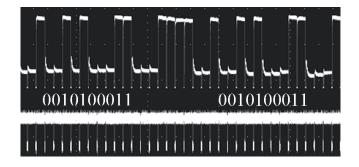

The observed operating distance with transmit power 0.5 W erp was about 30 cm. The operating distance in this case is power transfer limited. This can be seen from Fig. 9, where communication in the system is demonstrated. The signal to noise ratio in the receiver is very good. Thus the operating distance is proportional to the square root of the rectifier efficiency  $\eta$ . Using the VTT process allows a considerable improvement in the operating distance.

Figure 9. Communication in the wireless sensor system seen with an oscilloscope: The upper trace shows transponder response with conversion result written out. Between the conversion results a header is transmitted. The lower trace shows clock signal sent by the reader to the transponder.

# 4. CONCLUSIONS

In this paper a sensor transponder for UHF RFID was described. The chip includes a 10 bit analog to digital converter and is designed for external capacitive sensors. The chip power consumption is about  $30 \ \mu W_{DC}$ .

Wirelessly powered measurement of capacitance was demonstrated at 869 MHz to a distance of 30 cm, which is short in comparison with the operating distances of several meters of the commercial UHF RFID transponders, but which only include memory. Furthermore, the short operating distance is mostly due to the low efficiency of the rectifier, which was realised using standard aluminium metallisation of the process.

Future and ongoing work of the authors includes realising a similar chip with the VTT process, which enables a better rectifier, as well as capacitive MEMS sensor integration on the same chip.

## ACKNOWLEDGMENTS

This work has been financially supported by Tekes, the Finnish Funding Agency for Technology and Innovation, and EU under the sixth framework.

## REFERENCES

- [1] X. Q. Bao, W. Burkhard, V. V. Varadan, V. K. Varadan, "SAW temperature sensor and remote reading system," IEEE Ultrasonics Symposium, 1987, pp. 583-586.

- [2] N. Cho, S.-J. Song, S. Kim, S. Kim, H.-J. Yoo, "A 5.1-µW UHF RFID tag chip integrated with sensors for wireless environmental monitoring", Proceedings of ESSCIRC, September 12-16, 2005, pp. 279-282.

- [3] U. Karthaus, M. Fischer, "Fully integrated passive UHF RFID transponder IC with 16.7-μW minimum RF input power", IEEE J. Solid-State Circuits, volume 38, October 2003, pp. 1602-1608.

- [4] J. Sauerbrey, D. Schmitt-Landsiedel, R. Thewes, "A 0.5V, 1mW successive approximation ADC", Proceedings of ESSCIRC, September 24-26, 2002, pp. 247-250.

- [5] L. Ferreira, R. Moreno, T. Pimenta, C. Filho, "A precise sample-and-hold circuit topology in CMOS for low voltage applications with offset voltage self correction", IEEE International Conference on Communications, Circuits and Systems, volume 2, June 29-July 1, 2002, pp. 914-917.

- [6] J. Marjonen, R. Alaoja, H. Ronkainen, M. Åberg, "Low power successive approximation A/D converter for passive RFID tag sensors", Proceedings of the 10th Biennial Baltic Electronics Conference, October 2-4, 2006, pp. 107-110.