DESIGN AND CHARACTERIZATION OF MONOLITHIC MILLIMETER-WAVE ACTIVE AND PASSIVE COMPONENTS, LOW-NOISE AND POWER AMPLIFIERS, RESISTIVE MIXERS, AND RADIO FRONT-ENDS

**Doctoral Dissertation**

Mikko Varonen

Aalto University

School of Science and Technology

Faculty of Electronics, Communications and Automation

Department of Micro and Nanosciences

DESIGN AND CHARACTERIZATION OF MONOLITHIC MILLIMETER-WAVE ACTIVE AND PASSIVE COMPONENTS, LOW-NOISE AND POWER AMPLIFIERS, RESISTIVE MIXERS, AND RADIO FRONT-ENDS

**Doctoral Dissertation**

#### Mikko Varonen

Doctoral dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Faculty of Electronics, Communications and Automation for public examination and debate in Auditorium S4 at the Aalto University School of Science and Technology (Espoo, Finland) on the 29th of April 2010 at 12 noon.

Aalto University

School of Science and Technology

Faculty of Electronics, Communications and Automation

Department of Micro and Nanosciences

Aalto-yliopisto Teknillinen korkeakoulu Elektroniikan, tietoliikenteen ja automaation tiedekunta Mikro- ja nanotekniikan laitos Distribution:

Aalto University

School of Science and Technology

Faculty of Electronics, Communications and Automation

Department of Micro and Nanosciences

P.O. Box 13000 (Otakaari 5)

FI - 00076 Aalto

**FINLAND**

URL: http://nano.tkk.fi/

Tel. +358-9-470 22276

Fax +358-9-470 22269

E-mail: mikko.varonen@tkk.fi

© 2010 Mikko Varonen

ISBN 978-952-60-3090-6 ISBN 978-952-60-3091-3 (PDF) ISSN 1795-2239

ISSN 1795-4584 (PDF)

URL: http://lib.tkk.fi/Diss/2010/isbn9789526030913/

TKK-DISS-2741

Multiprint Oy Espoo 2010

| ABSTRACT OF DOCTORAL DISSERTATION                                                                                                                                                         |                                      | AALTO UNIVERSITY SCHOOL OF SCIENCE AND TECHNOLOGY P.O. BOX 11000, FI-00076 AALTO http://www.aalto.fi |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------|--|--|

| Author Mikko Vard                                                                                                                                                                         | onen                                 |                                                                                                      |  |  |

| Name of the dissertation  Design and characterization of monolithic millimeter-wave active and passive components, low-noise and power amplifiers, resistive mixers, and radio front-ends |                                      |                                                                                                      |  |  |

| Manuscript submitted 26.10.2009                                                                                                                                                           |                                      | Manuscript revised 03.02.2010                                                                        |  |  |

| Date of the defenc                                                                                                                                                                        | Date of the defence 29.04.2010       |                                                                                                      |  |  |

| ☐ Monograph                                                                                                                                                                               |                                      | ☐ Article dissertation (summary + original articles)                                                 |  |  |

| Faculty                                                                                                                                                                                   | Faculty of Electronics, Communic     | ations and Automation                                                                                |  |  |

| Department                                                                                                                                                                                | Department of Micro and Nanosciences |                                                                                                      |  |  |

| Field of research                                                                                                                                                                         | Electronic Circuit Design            |                                                                                                      |  |  |

| Opponent(s)                                                                                                                                                                               | Professor Piet Wambacq               |                                                                                                      |  |  |

| Supervisor                                                                                                                                                                                | Professor Kari Halonen               |                                                                                                      |  |  |

| Instructor                                                                                                                                                                                |                                      |                                                                                                      |  |  |

|                                                                                                                                                                                           | ·                                    |                                                                                                      |  |  |

#### Abstract

This thesis focuses on the design and characterization of monolithic active and passive components, low-noise and power amplifiers, resistive mixers, and radio front-ends for millimeter-wave applications. The thesis consists of 11 publications and an overview of the research area, which also summarizes the main results of the work. In the design of millimeter-wave active and passive components the main focus is on realized CMOS components and techniques for pushing nanoscale CMOS circuits beyond 100 GHz. Test structures for measuring and analyzing these components are shown. Topologies for a coplanar waveguide, microstrip line, and slow-wave coplanar waveguide that are suitable for implementing transmission lines in nanoscale CMOS are presented. It is demonstrated that the proposed slow-wave coplanar waveguide improves the performance of the transistor-matching networks when compared to a conventional coplanar waveguide and the floating slow-wave shield reduces losses and simplifies modeling when extended below other passives, such as DC decoupling and RF short-circuiting capacitors. Furthermore, wideband spiral transmission line baluns in CMOS at millimeter-wave frequencies are demonstrated. The design of amplifiers and a wideband resistive mixer utilizing the developed components in 65-nm CMOS are shown. A 40-GHz amplifier achieved a +6-dBm 1-dB output compression point and a saturated output power of 9.6 dBm with a miniature chip size of 0.286 mm<sup>2</sup>. The measured noise figure and gain of the 60-GHz amplifier were 5.6 dB and 11.5 dB, respectively. The V-band balanced resistive mixer achieved a 13.5-dB upconversion loss and 34dB LO-to-RF isolation with a chip area of 0.47 mm<sup>2</sup>. In downconversion, the measured conversion loss and 1-dB input compression point were 12.5 dB and +5 dBm, respectively. The design and experimental results of low-noise and power amplifiers are presented. Two wideband low-noise amplifiers were implemented in a 100-nm metamorphic high electron mobility transistor (HEMT) technology. The amplifiers achieved a 22.5-dB gain and a 3.3-dB noise figure at 94 GHz and a 18-19-dB gain and a 5.5-7.0-dB noise figure from 130 to 154 GHz. A 60-GHz power amplifier implemented in a 150-nm pseudomorphic HEMT technology exhibited a +17-dBm 1-dB output compression point with a 13.4-dB linear gain. In this thesis, the main system-level aspects of millimeter-wave transmitters and receivers are discussed and the experimental circuits of a 60-GHz transmitter front-end and a 60-GHz receiver with an on-chip analog-to-digital converter implemented in 65-nm CMOS are shown. The receiver exhibited a 7-dB noise figure, while the saturated output power of the transmitter front-end was +2 dBm. Furthermore, a wideband W-band transmitter front-end with an output power of +6.6 dBm suitable for both image-rejecting superheterodyne and direct-conversion transmission is demonstrated in 65-nm CMOS.

Keywords balun, CMOS, low-noise amplifier, millimeter-wave receiver, millimeter-wave transmitter, MMIC, power amplifier, resistive mixer, slow-wave shield, transmission line

| unipiliter, resistiv                                                                                        | re mixer, slow wave sincle, transmission mic                                                 |                 |                     |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------|---------------------|

| ISBN (printed)                                                                                              | 978-952-60-3090-6                                                                            | ISSN (printed)  | 1795-2239           |

| ISBN (pdf)                                                                                                  | 978-952-60-3091-3                                                                            | ISSN (pdf)      | 1795-4584           |

| Language                                                                                                    | English                                                                                      | Number of pages | 83 p. + app. 107 p. |

| Publisher                                                                                                   | her Aalto University, School of Science and Technology, Department of Micro and Nanosciences |                 |                     |

| Print distribution Aalto University, School of Science and Technology, Department of Micro and Nanosciences |                                                                                              |                 |                     |

| ☐ The dissertation can be read at http://lib.tkk.fi/Diss/2010/isbn9789526030913/                            |                                                                                              |                 |                     |

|                          |                                   | Aaito-yiiopisto                                                                            |

|--------------------------|-----------------------------------|--------------------------------------------------------------------------------------------|

| VÄITÖSKIRJAN TIIVISTELMÄ |                                   | AALTO-YLIOPISTO<br>TEKNILLINEN KORKEAKOULU<br>PL 11000, 00076 AALTO<br>http://www.aalto.fi |

| Tekijä Mikko Var         | onen                              |                                                                                            |

|                          |                                   | vikomponenttien, vähäkohinaisten vahvistimien,<br>etupäiden suunnittelu ja karakterisointi |

| Käsikirjoituksen pä      | äivämäärä 26.10.2009              | Korjatun käsikirjoituksen päivämäärä 03.02.2010                                            |

| Väitöstilaisuuden a      | ajankohta 29.04.2010              |                                                                                            |

| ☐ Monografia             |                                   | ☐ Yhdistelmäväitöskirja (yhteenveto + erillisartikkelit)                                   |

| Tiedekunta               | Elektroniikan, tietoliikenteen ja | automaation tiedekunta                                                                     |

| Laitos                   | Mikro- ja nanotekniikan laitos    |                                                                                            |

| Tutkimusala              | Piiritekniikka                    |                                                                                            |

| Vastaväittäjä(t)         | Professori Piet Wambacq           |                                                                                            |

| Työn valvoja             | Professori Kari Halonen           |                                                                                            |

| Työn ohjaaja             |                                   |                                                                                            |

|                          | <u> </u>                          |                                                                                            |

#### Tiivistelmä

Tässä väitöskirjassa on tutkittu millimetriaaltoalueen integroituja aktiivi- ja passiivikomponentteja, vähäkohinaisia vahvistimia, tehovahvistimia, resistiivisiä sekoittimia ja radioetupäitä. Väitöskirja koostuu 11:sta julkaisusta sekä niistä laaditusta yhteenvedosta. Aktiivi- ja passiivikomponenttien suunnittelussa on keskitytty CMOS-komponentteihin ja piirisuunnittelutekniikoihin, joilla voidaan toteuttaa piirejä yli 100 GHz:n taajuuden käyttäen nanomittaluokan CMOSteknologioita. Työssä on suunniteltu testipiirejä komponenttien mittauksia ja analysointeja varten. Työssä on esitetty koplanaariselle siirtojohdolle, mikroliuskalle ja hitaan aallon suojalla toteutetulle koplanaariselle siirtojohdolle rakenteet, joita voidaan käyttää nanomittaluokan CMOS-teknologioissa. Työssä on demonstroitu, että hitaan aallon suojalla toteutettu koplanaarinen siirtojohto vähentää transistorien sovituspiirien häviöitä verrattuna koplanaariseen siirtojohtoon. On myös osoitettu, että hitaan aallon suojan ulottaminen muiden passiivisten komponenttien alle vähentää häviöitä ja yksinkertaistaa millimetriaaltoalueella. Tvössä demonstroidaan CMOS-teknologioilla kierukkasiirtolinjamuuntajien käyttöä millimetriaaltoalueella. Esitetyillä komponenteilla on suunniteltu vahvistimia ja laajakaistainen balansoitu resistiivinen sekoitin käyttäen 65 nm:n CMOS-teknologiaa. 40 GHz:n vahvistimesta mitattiin lähdön yhden dB:n kompressiopisteeksi 6 dBm:n tehotaso ja saturaatiotehoksi 9,6 dBm. Piirin pinta-ala on 0,286 mm². 60 GHz:n vahvistimen kohinaluvuksi mitattiin 5,6 dB:ä ja vahvistukseksi 11,5 dB:ä. V-alueen sekoittimen sekoitusvaimennukseksi mitattiin 13,5 dB:ä ylössekoituksessa ja lokaalivaimennukseksi RF-portissa 34 dB:ä. Piirin pintaala on 0,47 mm². Alassekoitusvaimennukseksi mitattiin 12,5 dB:ä ja tulon yhden dB:n kompressio-pisteeksi 5 dBm:n tehotaso. Työssä esitetään millimetriaaltoalueen vähäkohinaisten vahvistimien ja teho-vahvistimien suunnittelua. Kaksi laajakaistaista vähäkohinaista vahvistinta suunniteltiin ja toteutettiin 100 nm:n metamorfisella HEMT-teknologialla. Vahvistimien vahvistukseksi mitattiin 22,5 dB:ä 94 GHz:n taajuudella ja 18-19 dB:ä taajuusalueella 130-154 GHz:ä. Vastaavat mitatut kohinaluvut olivat 3,3 ja 5,5-7,0 dB:ä. Tehovahvistimen lähdön yhden dB:n kompressiopisteeksi mitattiin 17 dBm:n tehotaso ja vahvistukseksi 13,4 dB:ä. Vahvistin toteutettiin 150 nm:n pseudomorfisella HEMT-teknologialla. Työssä käsitellään millimetriaalto-alueen lähettimiä ja vastaanottimia systeemitasolla ja esitellään 65 nm:n CMOSteknologialla toteutettujen 60 GHz:n ja W-alueen lähettimien sekä 60 Ghz:n vastaanottimen, joka sisältää analogiadigitaalimuuntimen, suunnittelu. Vastaanottimen kohinaluvuksi mitattiin 7 dB:ä ja 60 GHz lähettimen lähtötehoksi 2 dBm.

Asiasanat CMOS, hitaan aallon suoja, millimetriaaltoalueen lähetin, millimetriaaltoalueen vastaanotin, MMIC, resistiivinen sekoitin, siirtojohto, symmetrointimuuntaja, tehovahvistin, vähäkohinainen vahvistin

| ISBN (paine                                                                       | ttu) 978-952-60-3090-6                                                                                |           | ISSN (painettu)      | 1795-2239            |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------|----------------------|----------------------|

| ISBN (pdf)                                                                        | 978-952-60-3091-3                                                                                     |           | ISSN (pdf)           | 1795-4584            |

| Kieli                                                                             | Englanti                                                                                              |           | Sivumäärä            | 83 s. + liit. 107 s. |

| Julkaisija                                                                        | Aalto-yliopisto, Teknillinen ko                                                                       | rkeakoulu | ı, Mikro- ja nanotel | kniikan laitos       |

| Painetun väi                                                                      | Painetun väitöskirjan jakelu Aalto-yliopisto, Teknillinen korkeakoulu, Mikro- ja nanotekniikan laitos |           |                      |                      |

| ☐ Luettavissa verkossa osoitteessa http://lib.tkk.fi/Diss/2010/isbn9789526030913/ |                                                                                                       |           |                      |                      |

## **Preface**

The work for this thesis was carried out in the Electronic Circuit Design Laboratory of Helsinki University of Technology during 2001-2009. The work was funded by the Finnish Funding Agency for Technology and Innovation (Tekes) under the Nastec, Brawe, and LALAMO projects, by the Academy of Finland under the Millimono and UNCMOS projects and the Centre of Excellence program (SMARAD2), the Graduate School in Electronics, Telecommunication and Automation (GETA), by the European Space Agency, by Nokia Research Center, by Nokia Networks, and by Ylinen Electronics. I would like to thank the Nokia Foundation, Walter Ahlström Foundation, HPY Research Foundation, Ulla Tuominen Foundation, the Finnish Society of Electronics Engineers (EIS), and Telealan edistämissäätiö for awarding scholarships for my postgraduate studies.

I would like to thank my supervisor, Professor Kari Halonen, for the opportunity to write this thesis and encouragement during the study. I wish to thank both Professor Kari Halonen and emeritus Professor Veikko Porra for the opportunity to work on this interesting research area. I warmly thank Professor Henrik Sjöland and Professor Patrick Reynaert for reviewing my thesis.

I have been fortunate to work on many interesting research projects among very talented research engineers. The excellent research results reported in this thesis have been result of collaborative work and I am grateful to all co-authors for their valuable work. Especially, I wish to thank my colleague Mikko Kärkkäinen for managing the projects, which gave me the opportunity to concentrate on the research work and writing my thesis. I also thank D.Sc. Pekka Kangaslahti for instructing me in the early stage of my studies, advice during the research, and reading this thesis. I appreciate the work of Jan Riska in the area of MMIC design. It has inspired me in my own research. I am grateful to Dan Sandström for fruitful collaboration. I also thank Professor Jussi Ryynänen for advice, useful discussions about MMIC design, and good company during several conference trips. All the staff at the Electronic Circuit Design Laboratory deserves thanks for creating a pleasant working atmosphere. I warmly thank Ville Saari, Tero Tikka, Pasi Juurakko, and Mikko Kärkkäinen for sharing the same office with me in a good team spirit.

8

I wish to thank my friends for giving me something else to think than the research on electronics. The friendship that we share and our freetime activities have been playing important part in completing this thesis. I am grateful to my mother and Veikko, my grandparents and my parents-in-law for encouragement and support during my studies. Finally, I would like to thank my lovely wife Essi. Without her support I would never have been able to finish this work. Writing this thesis would have been a real burden without her and my daughter Emmi bringing sunshine to my life.

Espoo, April 2010

Mikko Varonen

# **Contents**

| Preface                                                             | 7         |

|---------------------------------------------------------------------|-----------|

| Contents                                                            | 9         |

| List of Publications                                                | 11        |

| Author's contribution                                               | 13        |

| List of Abbreviations                                               | 16        |

| List of Symbols                                                     | 19        |

| 1 Introduction                                                      | 22        |

| 1.1 Objectives and contents of this thesis                          |           |

| 2 Millimeter-wave active and passive components                     | 24        |

| 2.1 Design flow for millimeter-wave circuits in CMOS                | 24        |

| 2.2 Transmission lines in CMOS                                      | 25        |

| 2.2.1 Coplanar waveguide in CMOS                                    | 25        |

| 2.2.2 Microstrip line in CMOS                                       | 26        |

| 2.2.3 Slow-wave coplanar waveguide in CMOS                          | 27        |

| 2.2.4 Characterization of transmission lines in CMOS                | 28        |

| 2.3 Capacitors in CMOS                                              | 30        |

| 2.4 Spiral transmission line baluns                                 | 31        |

| 2.5 Transistor layout considerations for millimeter-wave operation  | 34        |

| 2.5.1 Transistor de-embedding structures for millimeter-wave freque | encies in |

| CMOS                                                                | 37        |

| 3 Millimeter-wave amplifier design                                  | 38        |

| 3.1 Millimeter-wave low-noise amplifier design                      |           |

| 3.1.1 Experimental results of millimeter-wave low-noise amplifiers. |           |

| 3.2 Millimeter-wave power amplifiers                                | 43        |

| 3.2.1 Experimental results of the millimeter-wave power amplifier        | 47    |

|--------------------------------------------------------------------------|-------|

| 3.3 Millimeter-wave amplifier design in CMOS                             | 49    |

| 3.3.1 Amplifier topology                                                 | 49    |

| 3.3.2 Impedance matching of millimeter-wave CMOS amplifiers              | 49    |

| 3.3.3 Experimental results of millimeter-wave amplifiers in CMOS         | 51    |

| 4 Millimeter-wave resistive mixer design                                 | 53    |

| 4.1 Resistive mixer fundamentals                                         | 53    |

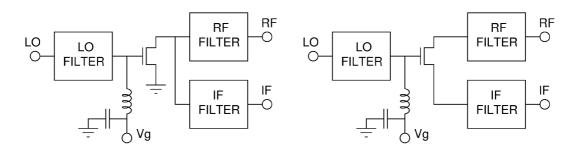

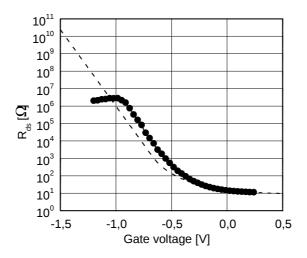

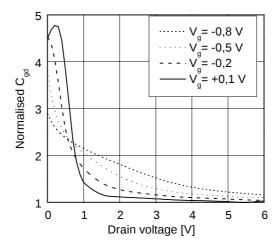

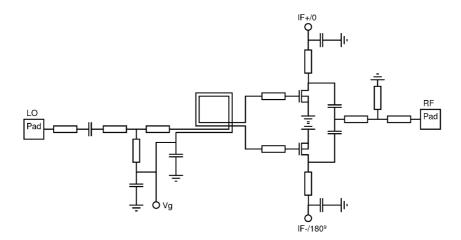

| 4.2 Balanced resistive mixers                                            | 55    |

| 4.2.1 Experimental results of the millimeter-wave balanced resistive mix | ker56 |

| 5 Millimeter-wave receiver and transmitter front-end design              | 58    |

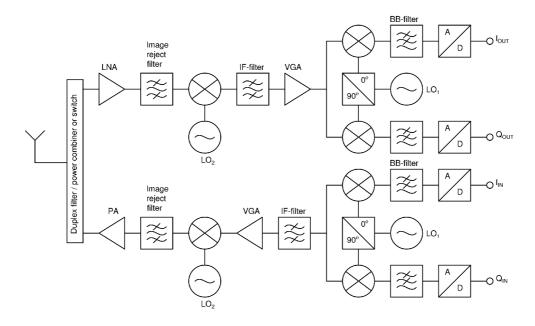

| 5.1 Transceiver architectures                                            | 58    |

| 5.1.1 Superheterodyne architecture                                       | 58    |

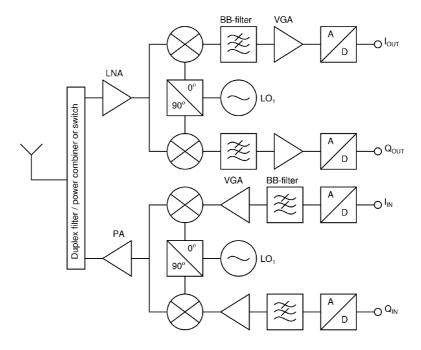

| 5.1.2 Direct conversion architecture                                     | 60    |

| 5.2 Experimental results                                                 | 61    |

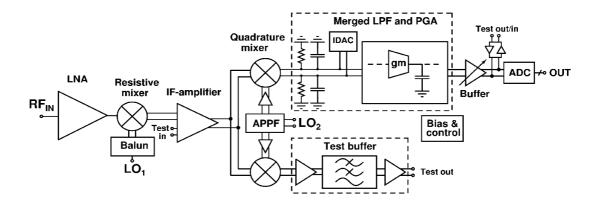

| 5.2.1 A 60-GHz CMOS receiver with an on-chip ADC                         | 61    |

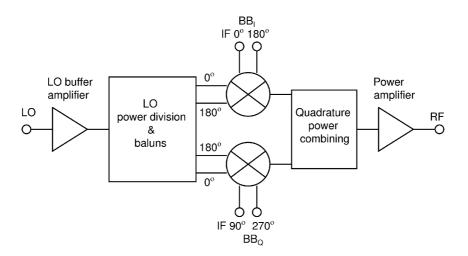

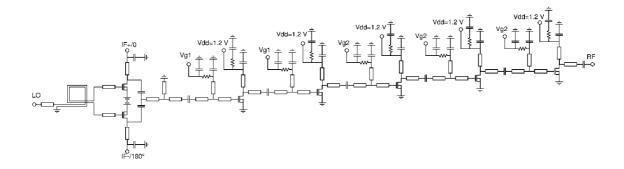

| 5.2.2 A 60-GHz transmitter front-end in CMOS                             | 63    |

| 5.2.3 A W-band transmitter front-end in CMOS                             | 65    |

| 6 Conclusions                                                            | 66    |

| References                                                               | 70    |

| Еммата                                                                   |       |

# **List of Publications**

This thesis is based on the work presented in the following papers:

- [P1] M. Varonen, M. Kärkkäinen, M. Kantanen, and K. A. I. Halonen, "Millimeter-wave integrated circuits in 65-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 9, pp. 1991-2002, Sep. 2008.

- [P2] M. Kärkkäinen, M. Varonen, D. Sandström, T. Tikka, S. Lindfors, and K. A. I. Halonen, "Design aspects of 65-nm CMOS MMICs," in *Proc. of the 3rd European Microwave Integrated Circuits Conference*, Amsterdam, the Netherlands, Oct. 2008, pp. 115-118.

- [P3] D. Sandström, M. Varonen, M. Kärkkäinen, and K. A. I. Halonen, "60 GHz amplifier employing slow-wave transmission lines in 65-nm CMOS," accepted to be published in *International Journal on Analog Integrated Circuits and Signal Processing*.

- [P4] D. Sandström, M. Varonen, M. Kärkkäinen, and K. A. I. Halonen, "W-band CMOS amplifiers achieving +10dBm saturated output power and 7.5dB NF," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 12, pp. 3403-3409, Dec. 2009.

- [P5] D. Sandström, M. Varonen, M. Kärkkäinen, and K. A. I. Halonen, "A W-band 65nm CMOS transmitter front-end with 8GHz IF bandwidth and 20dB IR-ratio," in *IEEE International Solid-State Circuits Conference Dig.*, San Francisco, CA, Feb. 2010, pp. 418-419.

- [P6] M. Varonen, M. Kärkkäinen, J. Riska, P. Kangaslahti, and K. A. I. Halonen, "Resistive HEMT mixers for 60-GHz broadband telecommunication," *IEEE Transactions on Microwave Theory and Techniques*, vol. 53, no. 4, pp. 1322-1330, April 2005.

- [P7] M. Varonen, M. Kaltiokallio, V. Saari, O. Viitala, M. Kärkkäinen, S. Lindfors, J. Ryynänen, and K. A. I. Halonen, "A 60-GHz CMOS receiver with an on-chip ADC," in *IEEE International Radio Frequency Integrated Circuits Symposium Dig.*, Boston, MA, June 2009, pp. 445-448.

- [P8] M. Kärkkäinen, M. Varonen, D. Sandström, and K. A. I. Halonen, "60-GHz receiver and transmitter front-ends in 65-nm CMOS," in *IEEE International Microwave Symposium Dig.*, Boston, MA, June 2009, pp. 577-580.

- [P9] M. Varonen, M. Kärkkäinen, M. Kantanen, M. Laaninen, T. Karttaavi, R. Weber, A. Leuther, M. Seelmann-Eggebert, T. Närhi, J. Lahtinen, and K. A. I. Halonen, "W-band lownoise amplifiers," *Proceedings of the European Microwave Association*, vol. 3, issue 4, pp. 358-366, Dec. 2007.

- [P10] M. Kantanen, M. Kärkkäinen, M. Varonen, M. Laaninen, T. Karttaavi, R. Weber, A. Leuther, M. Seelmann-Eggebert, T. Närhi, J. Lahtinen, and K. A. I. Halonen, "Low noise amplifiers for D-band," *Proceedings of the European Microwave Association*, vol. 4, issue 4, pp. 268-275, Dec. 2008.

- [P11] M. Kärkkäinen, M. Varonen, P. Kangaslahti, and K. A. I. Halonen, "Integrated amplifier circuits for 60 GHz broadband telecommunication," *International Journal on Analog Integrated Circuits and Signal Processing*, vol. 42, no. 1, pp. 37-46, January 2005.

# **Author's contribution**

Paper [P1] was mainly contributed by the author. The author was responsible for writing the manuscript. The author designed all the test structures for the passive and active components. The topology for the conventional coplanar waveguide and the core capacitor was designed by the author and M. Kärkkäinen in co-operation. The author designed the slow-wave coplanar waveguide, the spiral transmission line balun, both amplifiers, and the mixer. The measurements of the S-parameters, the noise parameters of the transistor, the noise figures, and the power sweeps of the amplifiers, to which the author contributed, were carried out in the Millimetre Wave Laboratory of Finland. The author was responsible for the measurement setup and the measurements of the mixer. The analysis of the transistor S-parameter data was carried out by the author and M. Kärkkäinen in co-operation. M. Kärkkäinen was responsible for extracting the noise parameters of the transistor and the de-embedding of the S-parameters of the capacitor. Otherwise, the author is responsible for the analysis in the manuscript.

Paper [P2] is a result of collaborative work. The author contributed substantially to the writing of the manuscript. The electromagnetic simulations of the transmission lines were performed by D. Sandström under the instruction of the author and M. Kärkkäinen. The author designed the amplifier presented in the paper. The test structure was designed and the transistor was analyzed by the author in co-operation with T. Tikka. The measurements, to which the author contributed, were carried out in the Millimetre Wave Laboratory of Finland.

Paper [P3] is a result of collaborative work. The author contributed to the writing of the manuscript. The amplifier was designed by D. Sandström under the instruction of the author. The microstrip line was designed and the results analyzed by D. Sandström under the instruction of the author. The noise performance of the amplifier was simulated using the de-embedded transistor data calculated by M. Kärkkäinen. The models of the other active and passive components are based on the work presented in [P1].

Paper [P4] is a result of collaborative work. The author contributed to the writing of the manuscript. The two amplifiers were designed by D. Sandström under the instruction of the author. The author designed the test structures for the transmission lines. The author had the main responsibility for the analysis of the results of the transmission lines in co-operation with

D. Sandström. The original idea of extending the slow-wave shield under the other passives and under the capacitor was the author's. The realization of the shield under the capacitor was carried out by D. Sandström in co-operation with the author. M. Kärkkäinen was responsible for the realization and the analysis of the slotted plate capacitor in co-operation with D. Sandström. The models of the other active and passive components and the matching arrangement of the amplifiers are based on the work presented in [P1]. The measurements were carried out in the Millimetre Wave Laboratory of Finland.

Paper [P5] is a result of collaborative work. The author contributed to the writing of the manuscript. The author was responsible for the system-level design of the transmitter front-end. The circuit-level design of the transmitter front-end was carried out by D. Sandström and the author in co-operation. The measurements were carried out in the Millimetre Wave Laboratory of Finland.

Paper [P6] is a result of collaborative work. The author was responsible for writing the manuscript. J. Riska designed the circuits presented in this paper. The author was responsible for building the measurement setup and for the measurements and the analysis presented in the paper. M. Kärkkäinen contributed to the analysis of the measurement results.

Paper [P7] is a result of collaborative work. The author participated in the writing of the manuscript. The system-level analysis of the receiver was carried out by the author, M. Kaltiokallio and Prof. J. Ryynänen in co-operation. The author designed and implemented the millimeter-wave front-end for the receiver. The interface between the millimeter-wave front-end and the IF circuitry was designed and implemented by the author in co-operation with M. Kaltiokallio. M. Kaltiokallio designed and implemented all the IF circuits in co-operation with Prof. J. Ryynänen. V. Saari and O. Viitala designed and implemented the low-pass filter and the analog-to-digital converter, respectively, both in co-operation with Prof. S. Lindfors. The author participated in the building of the measurement setup and the measurements.

Paper [P8] is a result of collaborative work. The author was responsible for the design of the transmitter front-end and the amplifier for the receiver front-end. The spiral transmission line balun used in both front-ends is based on the work presented in [P1]. M. Kärkkäinen was

responsible for the downconverter mixer design. The author was responsible for the transmitter front-end measurements. The author wrote Chapters III, IV and V B.

Paper [P9] is a result of collaborative work. The author contributed to the writing of the manuscript. The author designed the wideband low-noise amplifier chip (LNA2) and participated in the on-wafer S-parameter measurements which were carried out in the Millimetre Wave Laboratory of Finland.

Paper [P10] is a result of collaborative work. The author designed the wideband low-noise amplifier chip (LNA3) and participated in the on-wafer S-parameter measurements, which were carried out in the Millimetre Wave Laboratory of Finland.

Paper [P11] is a result of collaborative work. The author designed the power amplifier chip. The power amplifier was packaged by Ylinen Electronics. The author was responsible for the power amplifier measurements, which were carried out in the Millimetre Wave Laboratory of Finland. The author wrote Chapter 4. Chapters 1, 2, and 5 were written by the author in co-operation with M. Kärkkäinen.

# **List of Abbreviations**

AC alternating current

ADC analog-to-digital converter

ADPD antiparallel diode pair

AlSb aluminum antimony

AM amplitude modulation

APPF active poly-phase filter

ASK amplitude shift-keying

BB baseband

BiCMOS bipolar complementary metal oxide semiconductor

C carbon

CAD computer-aided design

CG conversion gain

CMOS complementary metal oxide semiconductor

CPW coplanar waveguide

CS common source

DAC digital-to-analog converter

DAT distributed active transformer

DC direct current

DFE decision feedback equalizer

DSB double sideband

ESD electrical static discharge

FDD frequency domain duplexing

FET field-effect transistor

GaAs gallium arsenide

GCPW grounded coplanar waveguide

HEMT high electron mobility transistor

I in-phase

IF intermediate frequency

InAs indium arsenide

InP indium phosphide

IR image rejection

LNA low-noise amplifier

LO local oscillator

LPF low-pass filter

LTCC low temperature co-fired ceramic

MB-OFDM multi band orthogonal frequency division multiplexing

MHEMT metamorphic high electron mobility transistor

MIM metal-insulator-metal

MMIC monolithic microwave integrated circuit

MSG maximum stable gain

NF noise figure

OFDM orthogonal frequency division multiplexing

OOK on-off keying

PA power amplifier

PCB printed circuit board

PGA programmable gain amplifier

PHEMT pseudomorphic high electron mobility transistor

PLL phase-locked loop

PM phase modulation

Q quadrature-phase

RC resistor-capacitor

RF radio frequency

SHP subharmonically pumped

SiGe silicon germanium

SOI silicon on insulator

TDD time-domain duplexing

TIA transimpedance amplifier

USB universal serial bus

UWB ultra-wideband

VCO voltage-controlled oscillator

VGA variable gain amplifier

# **List of Symbols**

B bandwidth

BB<sub>I</sub> baseband in-phase

BB<sub>Q</sub> baseband quadrature-phase

*C* shunt capacitance per unit length

$C_{gd}$  gate-to-drain capacitance

$C_{gs}$  gate-to-source capacitance

$e_{n,out}$  output noise voltage

*F* noise factor

$f_{max}$  maximum frequency of oscillation

$F_{min}$  minimum noise factor

$f_t$  cut-off frequency

$F_{tot}$  total noise factor

*G* shunt conductance per unit length

*G* power gain

$g_{ds}$  drain-to-source conductance

$g_m$  transconductance

*H* distance between the signal line and ground plane

*ICP*<sub>1dB</sub> 1-dB input compression point

$I_d$  drain current

*IDAC* current-steering digital-to-analog converter

$I_{max}$  saturation current

$I_{swing}$  current swing

*k* Boltzmann's constant

*K* empirical fitting factor

L series inductance per unit length

$OCP_{1dB}$  1-dB output compression point

$PAE_{max}$  maximum power added efficiency

$P_{DC}$  power consumption

$P_{sat}$  saturated output power

$Q_C$  capacitive quality factor

$Q_L$  inductive quality factor

*Q*<sub>res</sub> self-resonance quality factor of a transmission line

*R* series resistance per unit length

$R_{ch}$  channel resistance

$R_{ds}$  drain-to-source resistance

$R_g$  gate resistance

$r_n$  equivalent normalized noise resistance

$R_{opt}$  optimum load line resistance

$R_{\rm s}$  source resistance of a transistor

$R_{\rm S}$  source resistance

S signal-to-ground spacing

$S_{11}$  input match

*SNR*<sub>in</sub> signal-to-noise ratio at the input

*SNR*<sub>out</sub> signal-to-noise ratio at the output

*T* absolute temperature

$V_{brk}$  device breakdown voltage

$V_d$  drain voltage

$V_{dd}$  supply voltage

$V_g$  gate voltage

$V_{knee}$  transistor knee voltage

$V_{out}$  output signal voltage

$V_S$  source voltage

$V_{swing}$  voltage swing

*W* width of the center conductor

$Z_0$  input impedance

$Z_L$  load impedance

$Z_{driver}$  output match for the driver

Z<sub>even</sub> even-mode impedance

$Z_{load}$  output match

$Z_{odd}$  odd-mode impedance of the quarter-wave transformer

$\alpha$  attenuation per unit length

$\beta$  phase delay

$\lambda$  wavelength

$ho_{opt}$  optimum reflection coefficient

$\rho_{\rm s}$  source reflection coefficient

$\omega$  angular frequency

## 1 Introduction

The millimeter-wave region of the electromagnetic spectrum covers the wavelengths from 10 millimeters to 1 millimeter, which corresponds to radio frequencies of 30 to 300 GHz. Applications for this frequency band vary from scientific satellites to commercial high-data-rate wireless transfers. The most promising millimeter-wave consumer applications are expected to utilize the unlicensed band around 60 GHz since it offers up to 7 GHz of bandwidth, which makes possible various high-bandwidth applications such as the wireless transmission of uncompressed high-definition video streams and the wireless replacement of wired interconnections for example USB 3.0. Other applications include point-to-point links at 60 GHz and in the E-band (71-76 GHz, 81-86 GHz) as well as collision avoidance car radars at 77 GHz. Applications above and around 100 GHz include radar, wideband communication, environmental monitoring, and millimeter-wave active and passive imaging at the atmospheric windows at 94, 140, and 220 GHz. The imaging applications include for example atmospheric radiometers, airport safety in landing and taxiing, the detection of concealed weapons and explosives, and high-resolution collision avoidance car radars.

The monolithic microwave integrated circuit (MMIC) technology enables the fabrication of low-cost, high-performance, highly reliable, small-sized, and light-weight millimeter-wave radios. By using MMICs the production of millimeter-wave systems is feasible in large quantities with a high yield. Millimeter-wave integrated circuits have traditionally been implemented using technologies which are based on compound semiconductors such as gallium arsenide (GaAs) or indium phosphide (InP). Recently, there has been enormous development in the field of silicon integrated circuits operating at millimeter-wave frequencies. Circuits and subsystems have been demonstrated in silicon germanium (SiGe) and complementary metal oxide semiconductor (CMOS) technologies even beyond 100 GHz. However, the high electron mobility transistor (HEMT) technology provides the best high-frequency noise, gain, and output power performance. An example application where optimum performance is required is atmospheric water vapor profiling using a radiometer for simultaneous measurements at the water vapor resonance frequency of 183 GHz and at a window frequency within 140 to 165 GHz. In the current generation of atmospheric sounders, a heterodyne radiometer architecture is used with Schottky mixers as the first component after the antenna. The sensitivity of these instruments could be improved with an HEMT low-noise amplifier. Silicon-based technologies have the potential to enable front-end, baseband, analog-to-digital and digital-to-analog converters, and digital signal processing circuitry to be integrated on a single chip. When targeting high-volume commercial applications, for example, in the 60-GHz band, CMOS technology can provide the highest integration level at low cost when produced in large volumes.

# 1.1 Objectives and contents of this thesis

Regardless of the MMIC technology, appropriate transceiver architectures, circuit topologies, and circuit design methods must be selected and developed to take full advantage of the potential of the chosen technology and to meet the requirements of the target application. This thesis focuses on the design and characterization of active and passive MMIC components and the circuit design of integrated low-noise and power amplifiers, resistive mixers, and radio front-ends for millimeter-wave applications.

In the first part of this thesis, an overview of the research area is given and the main results of the work are summarized. In Chapter 2, the design of active and passive millimeter-wave components are discussed. The main focus is on realized CMOS components and techniques for pushing nanoscale CMOS beyond 100 GHz. Furthermore, test structures for measuring and analyzing these components are shown. In Chapter 3, the design of millimeter-wave low-noise and power amplifiers and the experimental results of amplifiers implemented in GaAs pseudomorphic and metamorphic HEMT and 65-nm CMOS are shown. Chapter 4 concentrates on the design and experimental results of resistive mixers. In Chapter 5, the main system-level aspects of millimeter-wave transmitters and receivers are discussed and the experimental circuits of a 60-GHz transmitter front-end and single chip 60-GHz receiver implemented in 65-nm CMOS are shown. Furthermore, a wideband W-band transmitter front-end suitable for both image-rejecting superheterodyne and direct conversion transmission is demonstrated. The main contributions of this work are summarized in the chapter on Conclusions.

The second part of this thesis contains the published papers, where the theoretical and experimental results of this research work are reported.

# 2 Millimeter-wave active and passive components

## 2.1 Design flow for millimeter-wave circuits in CMOS

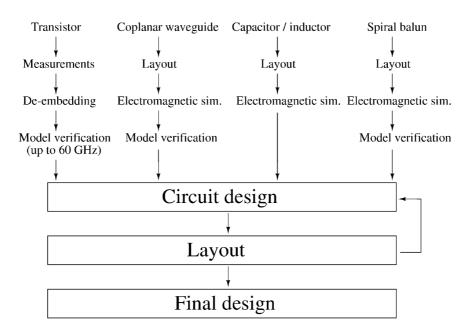

Millimeter-wave integrated circuits have traditionally been implemented using compound semiconductor technologies such as gallium arsenide or indium phosphide. For these technologies circuit models have been available for basic active and passive components in standard computer-aided design (CAD) packages. The foundries or institutions have developed their own compact models which enable accurate simulations well beyond 100 GHz [1]. However, active and passive millimeter-wave models for CMOS components are not readily available. Because of the lossy silicon substrate, thin dielectric layers above the substrate, and metal density requirements of CMOS technologies, the traditional models, for example, for transmission lines, metal-insulator-metal (MIM) capacitors, or resistors are not applicable for circuit design. Furthermore, the available models for transistors in CMOS are limited to RF frequencies [2]. Therefore, a systematic approach is needed for developing models that take into account the distributed effects and the challenges in CMOS described above. We used the design flow shown in Fig. 1, which resulted in state-of-the-art performance for the first design cycle circuits.

Fig. 1. Design flow for successful first design cycle in CMOS.

The flow includes preliminary test transistor measurements, electromagnetic simulations and parasitic extractions to capture the high-frequency behavior of the transmission lines, capacitors, and, balun structures and the circuit design of the amplifiers and mixers. We also included test structures in the first run for the accurate verification of the active and passive components. Using the data of these test structures, we have been able to design CMOS circuits beyond 100 GHz, with state-of-the-art results.

#### 2.2 Transmission lines in CMOS

Equation-based models derived for microwave transmission lines are not applicable for lines integrated on silicon substrates. The models typically assume thin conductors, ground planes which are far from the signal lines, and high-quality dielectrics [3]. Furthermore, thin dielectric layers above the substrate of a CMOS technology and stringent metal density requirements set limitations for implementing transmission lines on silicon. In Papers [P1] and [P2], we presented topologies for a coplanar waveguide (CPW), microstrip line, and slow-wave coplanar waveguide that are suitable for implementing transmission lines in nanoscale CMOS. Furthermore, test structures were developed for these lines and, to the best of the author's knowledge, we were the first to present measurement results for a slow-wave coplanar waveguide in 65-nm CMOS. We also showed that the proposed slow-wave CPW improves the performance (i.e. reduce losses) of the transistor-matching networks when compared to a conventional coplanar waveguide.

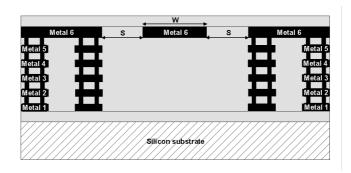

## 2.2.1 Coplanar waveguide in CMOS

A way to realize a conventional coplanar waveguide in nanoscale CMOS was proposed in [P1] and is shown in Fig. 2. The top metal layer is used for the center conductor. Although it is possible to design transmission lines that allow dummy metal filling around the signal conductor [4], in our case, dummy metal is not allowed around the center conductor or in between the ground planes of the CPW at any metal level. On the other hand, the metal density requirement has to be fulfilled, which means that there has to be enough metal at all metal levels. This is accomplished by strapping all the other metal layers together with vias to form the ground plane for the CPW. The width of the center conductor *W* and the signal-to-ground spacing *S* can be used for realizing different characteristic impedances for the CPW. A wider

center conductor leads to lower conductor losses. In principle, the maximum width of the center conductor is limited by the layout design rules of the chosen process. The metal density requirements set the limits for the maximum signal-to-ground spacing for the CPW. The unwanted slotline mode can be suppressed by connecting the ground planes of the CPW together around the discontinuities using the lower metal layers. In this way the ground planes at the opposite sides of the center conductor remain at the same potential.

Fig. 2. Simplified cross-section of the conventional coplanar waveguide (© 2008 IEEE, with permission from [P1]).

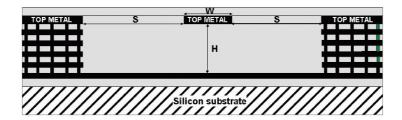

## 2.2.2 Microstrip line in CMOS

The microstrip line is realized between the top metal and lower metal planes. This isolates the effect of the lossy silicon substrate. The removal of dummy metal from both underneath and in the vicinity of the center conductor can create a metal density problem. A way to realize a microstrip line in a CMOS technology was proposed in [5] and is shown in Fig. 3.

Fig. 3. Simplified cross-section of the microstrip line with sidewalls (© 2008 EuMA, with permission from [P2]).

Adding ground planes similar to a CPW line fulfills the metal density requirements. These ground planes are then connected together using lower metal planes. Because of the metal density requirements the wide ground plane on the lower metal level must have longitudinal slots which do not interfere with the longitudinal ground currents of the microstrip line. When the distance between the signal line and ground plane *H* is rather low and when the side ground planes are located far from the center conductor, the signal propagates mostly in microstrip mode.

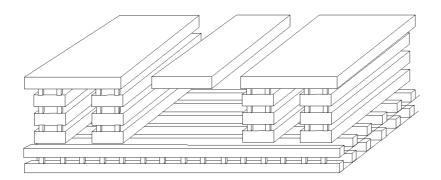

## 2.2.3 Slow-wave coplanar waveguide in CMOS

In the conventional coplanar waveguide, presented above, the electromagnetic field penetrates into the silicon substrate, which increases losses. A metal shield structure can be drawn using the lowest metal levels to prevent the electromagnetic fields from penetrating into the lossy silicon substrate. An efficient way to realize the shield is a slow-wave structure employing floating shield strips [6]. A simplified cross-section of the slow-wave coplanar waveguide proposed in [P1] is shown in Fig. 4. The two lowest metal layers are strapped together with vias to form the floating shield strips. The shield is designed using minimum design rules, i.e. minimum metal strip width and spacing, in order to suppress the induced current flow in the direction of the propagating RF signal. This minimizes the ohmic losses and maximizes the reactive energy storage per unit length. The smallest allowable shield strip spacing minimizes the exposure of the overlying CPW to the conductive substrate.

Fig. 4. Simplified cross-section of the slow-wave coplanar waveguide. The two lowest metal layers are strapped together with vias to form the floating shield strips (© 2008 IEEE, with permission from [P1]).

In addition to shielding the substrate, the dielectric constant and thus the wavelength of the slow-wave CPW are adjustable by changing the signal-to-ground spacing, allowing more compact implementation of transmission lines for impedance transformation and phase-shifting applications [6]. The electromagnetic simulation of the slow-wave CPW is challenging, typically time consuming, and memory intensive. Different methods have been developed for accurate and fast electromagnetic simulations of slow-wave CPWs in CMOS [7], [8]. To characterize slow-wave CPWs and on-chip transmission lines, we developed on-wafer test structures for the lines.

## 2.2.4 Characterization of transmission lines in CMOS

A test structure for a conventional CPW is shown in Fig. 5.

Fig. 5. Test structure for the conventional CPW in 65-nm CMOS (© 2008 IEEE, with permission from [P1]).

The self-resonance quality factor  $Q_{res}$  of a transmission line can be calculated using the attenuation per unit length  $\alpha$  and the phase delay along the line  $\beta$ . The inductive and capacitive quality factors ( $Q_L$  and  $Q_C$ ) can be calculated from the distributed transmission line parameters, series resistance per unit length R, series inductance per unit length L, shunt conductance per unit length R, and shunt capacitance per unit length R. These are related to the self-resonance quality factor according to the following equation [9]:

$$\frac{1}{Q_{res}} \approx \frac{2\alpha}{\beta} \approx \frac{1}{Q_L} + \frac{1}{Q_C} = \frac{R}{\omega L} + \frac{G}{\omega C} \quad . \tag{1}$$

The ground plane of the microstrip line is an effective substrate shield, but it is located very close to the signal line yielding to a very small distributed inductance. This significantly degrades the inductive quality factor which is a more important figure of merit when transmission lines are used to resonate with the intrinsic capacitances of the transistors [9]. The technology scaling even exacerbates the problem, since the distance between the signal line and ground plane typically decreases. This means that a narrower line width is needed for a highimpedance line. This will increase the metal losses of the signal line, degrading the inductive quality factor even more. Furthermore, the ground plane of the microstrip produces more metal losses since it has to be realized using thinner lower metal layers rather than the thick top metal layer in the case of the coplanar waveguide. Since the coplanar waveguide offers a higher inductive quality factor, it seems to be an appealing transmission-line topology for transistormatching networks [9]. Furthermore, the substrate losses can be minimized by using a slowwave shield. Although it is difficult to compare transmission lines with different impedances, the measurement results showed that the attenuations for the conventional and slow-wave CPW with characteristic impedances of 45  $\Omega$  and 35  $\Omega$  are 2.8 dB/mm and 1.1 dB/mm at 60 GHz, respectively, and that the  $Q_{res}$  was improved by a factor of three. This suggests that the shielding of the substrate is effective in the case of the structure that was realized [P1]. It was also found that the substrate shielding of the proposed slow-wave coplanar waveguide is as effective as with the microstrip topology [P3]. Since the substrate is shielded, the capacitive quality factor is increased and the impedance of the line is reduced when compared to a conventional CPW with the same *W* and *S*. However, in this case, the inductive quality factor remains the same, as the signal-to-ground spacing is the same in both topologies. In order to have the same impedances for the conventional and slow-wave CPW, the signal-to-ground spacing of the slow-wave CPW can be increased. The measurement results in [P4] suggest that both the inductive quality factor and the capacitive quality factors will then be higher for the slow-wave CPW. Thus, in our case the use of slow-wave CPW with the same characteristic impedance as the conventional CPW should improve the performance (i.e. reduce losses) of the transistor matching networks. However, it should be noted that the slow-wave CPW has a more limited range of feasible characteristic impedances compared to a conventional coplanar waveguide. This is because the capacitance per unit length is increased, whereas the inductance is the same as for a conventional CPW with the same W and S. For a high impedance slow-wave CPW line the signal-to-ground spacing should be increased or the width of the signal line should be decreased. However, the signal-to-ground spacing is limited by the design rules and the width of the center conductor by metallic losses.

# 2.3 Capacitors in CMOS

On-chip capacitors are needed for DC decoupling and implementing an RF short circuit for shunt matching stubs. Two types of capacitor structures are usually used in MMIC circuits: a metal-insulator-metal (MIM) capacitor or a finger (interdigital) capacitor. MIM capacitors consist of two metal plates with a thin dielectric between them. The fabrication of the MIM capacitors typically requires an additional process step in CMOS. Finger capacitors can be realized in any modern CMOS process. They consist of many narrow fingers in parallel using all the available metal layers.

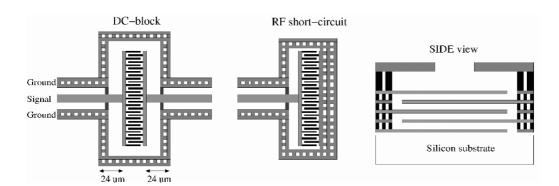

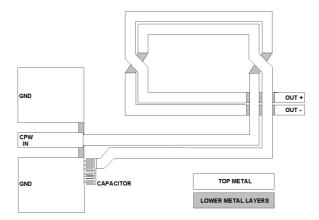

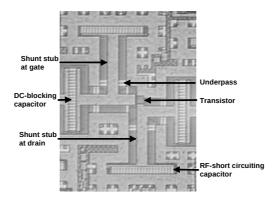

When CPWs are used for matching the capacitors should be implemented in a CPW environment, as shown in Fig. 6, where simplified layouts for DC decoupling and RF short-circuiting capacitors are shown. A micrograph of a CPW test structure for the series capacitor is shown in Fig. 7.

Fig. 6. Simplified layouts of a DC decoupling capacitor (left) and RF short-circuiting capacitor (middle) implemented using finger capacitors.

Fig. 7. Test structure for the series capacitor in 65-nm CMOS (© 2008 IEEE, with permission from [P1]).

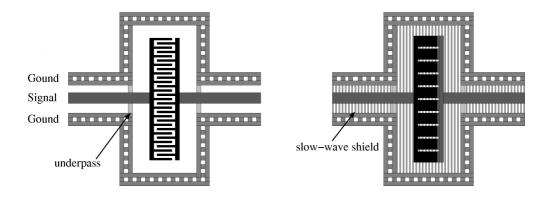

The close proximity of the silicon substrate of the capacitor structures described above induces losses and complicates the modeling. By extending the slow-wave shield below the capacitors, as shown in Fig. 8, the frequency-dependent substrate effects of the matching networks can be almost completely removed. As a result, the substrate losses of these passives become minimal. Furthermore, at millimeter-wave frequencies the modeling of passive structures becomes more accurate as the complicated substrate effects are negligible. In Paper [P4] we presented a custom-designed plate capacitor utilizing a slow-wave shield. As the floating shield effectively reduces substrate losses and coupling, the capacitor model can be obtained from the RC-parasitic extraction tool. Furthermore, the MIM capacitor can be modeled simply by using the foundry model, which utilizes a metal shield. In the simulations, the shield node is floating and the access to the MIM is modelled with slow-wave CPWs [P5].

Fig. 8. Simplified presentation of a standard finger capacitor in the CPW environment on left and the modified capacitor structure with a slow-wave shield in the slow-wave CPW environment on right (© 2009 IEEE, with permission from [P4]).

# 2.4 Spiral transmission line baluns

At millimeter-wave frequencies the integration of a transformer or a balun is feasible. A spiral transmission line transformer is a compact and wide-bandwidth balun. The use of spiral transmission line transformers has been shown to be a successful solution in microwave mixer circuits [10]. In Paper [11], compact-sized spiral baluns were utilized in millimeter-wave frequency doubler circuits. In Paper [P6], we demonstrated how to employ and analyze spiral transmission line baluns at the V-band. In addition, we presented a wide band and a compact

method for the transition from even to odd mode with in-phase power division by feeding the signal from a coplanar waveguide input to two spiral transmission line baluns. The use of transformers in silicon technologies at millimeter-wave frequencies is a relatively new subject of study [12]. To the best of the author's knowledge, we were the first to demonstrate spiral transmission line baluns in CMOS at millimeter-wave frequencies [P1]. We also utilized the even-to-odd mode transition with in-phase power division described above for the LO signal in CMOS at 100 GHz [P5].

The balun is used for matching the input impedance  $Z_0$  of the circuit to the impedances  $Z_L$  of the loads. The circuit is properly matched, providing that the electrical length of the coupled lines in the odd mode is  $\lambda/4$  at the design frequency and the odd-mode impedance  $Z_{odd}$  of the quarterwave transformer is

$$Z_{odd} = \sqrt{2Z_L Z_0} \quad . \tag{2}$$

For the signal to propagate in the odd mode, the balun has to suppress the even-mode propagation. This means that the even-mode impedance  $Z_{even}$  has to be as high as possible. The even-mode impedance can be increased by wrapping the balun in a spiral, as explained in [10]. The spiral has a minimal effect on the odd-mode impedance. In practice, the number of turns of the spiral is limited by the parasitic capacitance, which may cause undesired resonances.

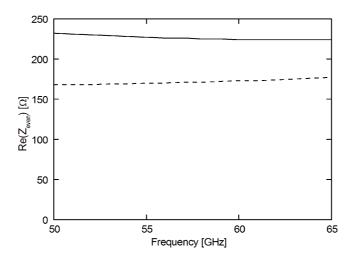

The electromagnetic analysis of the balun can be divided into two parts, as proposed in [10]. The even-mode characteristic impedance is evaluated from the electromagnetic simulation of a spiral inductor in which the lines of the balun are joined. The odd-mode impedance and the effective permittivity can be modeled by calculating the odd-mode properties of a straight section of coupled lines. Because of the semi-insulating substrate of compound semiconductor technologies, such as GaAs, this analysis is quite straightforward, since the return currents of the balun in both modes are well defined. In the even propagation mode the return current flows through the backside metallization, whereas in CMOS the return currents of a complicated circuit may not be explicit. In general, the return current in even propagation mode can flow through the lossy substrate or through a lower impedance return current path, for example, through other metallization layers connected between the source and load. However, at millimeter-wave frequencies the return current will flow underneath the structure because the

path has lower inductance [13]. Fig. 9 presents the simulated even-mode impedance of a straight section of coupled lines on CMOS and GaAs substrates used in this work. The even-mode impedance of the CMOS line is higher which is beneficial for the balun design.

Fig. 9. Simulated even-mode impedance of a straight section of coupled lines on CMOS and GaAs (dashed line) substrates. The odd mode impedance for both lines is around  $60 \Omega$ .

The CMOS balun was verified by measuring it on-wafer in a back-to-back test structure shown in Fig. 10. The measured insertion loss including pads was less than 5 dB from 50 to 60 GHz; thus, less than 2.5 dB for a single balun including a pad. The result is comparable to insertion losses of transformers published in [12] and [14]. Furthermore, the balun was used in a balanced resistive mixer [P1], [P7], [P8] and in an active mixer [P8]. The simulations and measurements of these circuits were in excellent agreement, which suggests that the design methodology chosen for the balun is successful.

Fig. 10. Test structure for the balun (© 2008 IEEE, with permission from [P1]). The chip area utilized is 0.57 mm x 0.30 mm.

In Paper [P1], we presented a transition from CPW to the balun in a deep submicron CMOS. As shown in Fig. 11, the balun is fed from a coplanar waveguide input. To ensure a proper excitation for the balun, the ground planes of the CPW are connected together with lower metal layers at the transition point from CPW to the spiral balun. In order to prevent the DC from being grounded, multiple finger capacitors are used in parallel at the ground connection of the spiral balun.

Fig. 11. Principle layout of the spiral balun and the transition from CPW input to the balun (© 2008 IEEE, with permission from [P1]).

# 2.5 Transistor layout considerations for millimeter-wave operation

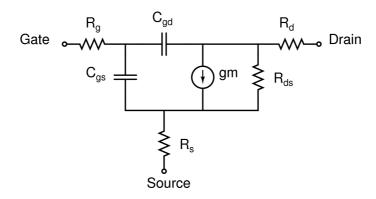

The transistor sizing is critical at millimeter-wave frequencies and the performance depends greatly on how the layout is drawn, since the influence of the parasitics become more dominant at millimeter-wave frequencies. Furthermore, the chosen technology has an influence on the optimal layout of the transistor. The simplified equations for the maximum frequency of oscillation  $f_{max}$ , and maximum stable gain MSG calculated from the transistor small-signal equivalent circuit shown in Fig. 12 can be used for evaluating the effect of parasitics on the gain performance of a transistor [15], [16]:

$$f_{max} \approx \frac{f_t}{2\sqrt{(R_a + R_s)(g_{ds} + 2\pi f_t C_{ad})}}$$

(3)

$$MSG \approx \sqrt{\left(\frac{g_m}{\omega C_{qd}}\right)^2 + 1} \approx \frac{g_m}{\omega C_{qd}}$$

(4)

where  $g_m$ ,  $R_g$ ,  $R_s$ ,  $C_{gd}$ , and  $g_{ds}$  are the transconductance, gate and source resistances, gate-to-drain capacitance, and drain-to-source conductance, respectively.  $f_t = g_m/[2\pi(C_{gs} + C_{gd})]$  is the cut-off frequency, where  $C_{gs}$  is the gate-to-source capacitance.

Fig. 12. Simplified small-signal equivalent circuit for a field-effect transistor (FET).

Because of the metal gates of HEMTs a few fingers of wide devices can be used to obtain a very high  $f_T$  and  $f_{max}$  for the transistor. Since polysilicon gates are used in CMOS-technology the width of the fingers must be kept short to minimize the gate resistance [13]. Because the minimum noise factor  $F_{min}$  is a function of the gate resistance, as shown in Fukui's equation, minimizing this parasitic is of great importance [17]:

$$F_{min} = 1 + K \omega C_{gs} \sqrt{\frac{R_g + R_s}{g_m}}$$

(5)

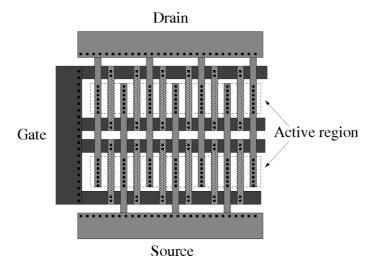

In Eq. (5), K is an empirical fitting factor. Fig. 13 shows a way to realize a common source transistor [P4], [18]. Several narrow fingers (around 1 um) are connected in parallel and the gates are connected on both sides to minimize the gate resistance. The drain and source are fed from opposite sides to minimize  $C_{gd}$ . As can be seen from Equations 3 and 4 this will improve both the MSG and  $f_{max}$ .

Fig. 13. Simplified layout of a multifinger transistor using double-contacted gates and two parallel devices in CMOS (© 2009 IEEE, with permission from [P4]).

Furthermore, as we use the transistor in a coplanar waveguide environment, the positioning of the gate, drain, and source access lines in this way gives the designer an opportunity to place a matching stub directly at the drain, as shown in Fig. 14. This is important, because adding even a short series line at the drain node will easily result in a low impedance point, which complicates the matching. For higher current swings, multiple fingers can be used in parallel to obtain high output power with a low supply voltage. However, the gate width cannot be increased arbitrarily as low-loss wideband matching may become unfeasible. This will be discussed in more detail in Chapter 3.

Fig. 14. Micrograph of a part of a transistor matching arrangement (© 2009 IEEE, with permission from [P4]).

# 2.5.1 Transistor de-embedding structures for millimeter-wave frequencies in CMOS

To capture the millimeter-wave behavior of a CMOS transistor, a coplanar waveguide test-structure for the transistor and the corresponding open and short structures for the de-embedding were developed [19]. A micrograph of the test structure is shown in Fig. 15.

Fig. 15. Coplanar test structure including open (middle) and short (right) structures for measuring a transistor (left) in CMOS.

Based on the transistor test structure data [P1], we have been able to design circuits such as amplifiers beyond 100 GHz [P4].

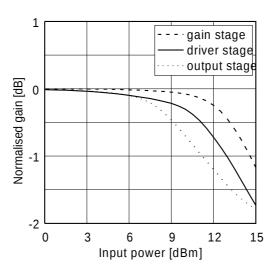

# 3 Millimeter-wave amplifier design

In a transmitter, a power amplifier is needed to amplify the transmitted signal to a sufficient power level with reasonable linearity and efficiency. The gain, noise, and intermodulation properties of the low-noise amplifier have a strong influence on the receiver performance. At millimeter-wave frequencies the gain of a single transistor is relatively low. Therefore, there is little margin, with power amplifiers, for trade-off between linearity, output power, gain, and efficiency. Because of the low gain, the noise contribution of the following stages becomes significant. Therefore, in a low-noise amplifier several stages have to be cascaded in order to make the noise produced in the following blocks low enough when the total system noise figure is calculated. The requirements for the power and low-noise amplifiers are determined by the intended system and its system specifications. Power amplifiers and low-noise amplifiers as part of millimeter-wave systems are discussed in more detail in Chapter 5. In this chapter the focus is on the circuit-level design of these blocks.

## 3.1 Millimeter-wave low-noise amplifier design

The noise factor is defined as:

$$F = \frac{SNR_{in}}{SNR_{out}} = \frac{V_S^2/(4kTBR_S)}{V_{out}^2/e_{n,out}^2} , \qquad (6)$$

where  $SNR_{in}$  and  $SNR_{out}$  are the signal-to-noise ratios at the input and output,  $V_S$  is the source voltage,  $V_{out}$  and  $e_{n,out}$  are the output signal and output noise voltages, k is the Boltzmann's constant, B is the bandwidth, and  $R_S$  is the source resistance. The Friis equation can be used for calculating the noise factor of the cascaded blocks [20]:

$$F_{tot} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots + \frac{F_n - 1}{\prod_{i=1}^{n-1} G_i}$$

(7)

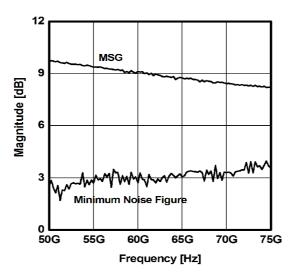

where  $F_n$  and  $G_n$  are the noise factor and available power gain of the  $n^{th}$  stage. From Equation 7 it can be seen that to minimize the total noise figure NF (NF=10log(F)) the gain of the first block should be high so as to reduce the noise contribution of the following stages. However, at high frequencies the gain of a single transistor is relatively low, as shown in Fig. 16. Therefore, in a millimeter-wave low-noise amplifier several stages have to be cascaded in order to make the noise produced in the following blocks low enough when the total system noise figure is calculated.

Fig. 16. Measured maximum stable gain and minimum noise figure of a W/L=90/0.07-sized transistor in 65-nm CMOS at V-band (data from [P1]).

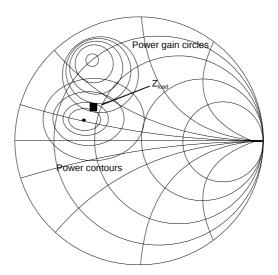

The minimum noise figure of a two-port can be obtained by selecting the source reflection coefficient properly. For a two-port and a transistor the noise factor can be expressed as [21]:

$$F = F_{min} + 4r_n \frac{|\rho_s - \rho_{opt}|^2}{(1 - |\rho_s|^2)|1 + \rho_{opt}|^2} , \qquad (8)$$

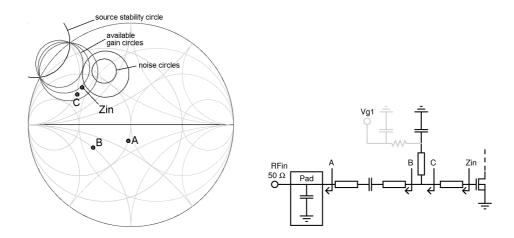

where  $r_n$  is the equivalent normalized noise resistance,  $\rho_s$  is the source reflection coefficient, and  $\rho_{opt}$  is the optimum reflection coefficient when the noise factor reaches its minimum value  $F_{min}$ . In general, matching the input of the transistor to the minimum noise figure does not lead to maximum gain for the transistor. Therefore, in the design of a low-noise amplifier there is a

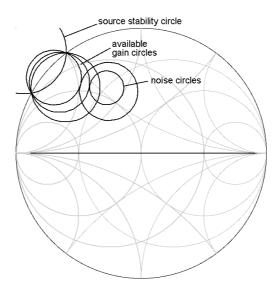

trade-off between the noise, gain, and return loss. This is illustrated in Fig. 17, where the noise circles and the available gain circles of a 90/0.07-sized CMOS transistor are plotted on a Smith chart.

Fig. 17. Available gain circles and noise circles of a 90/0.07-sized CMOS transistor are plotted for the 7, 8, and 9 dB and 3.1 and 3.4 dB levels, respectively (data from [P7]).

Feedback can be used for bringing the conjugate of  $S_{11}$  and  $\rho_{opt}$  closer together. In a series feedback an inductor is placed between the FET source contact and ground. The conjugate of  $S_{11}$  depends on both the series feedback and the output loading, whereas  $\rho_{opt}$  is only affected by the feedback inductor. This means that by selecting a proper combination of the output loading and feedback inductor the minimum noise figure and conjugate match can be obtained simultaneously [22]. The series feedback reduces the gain and improves the stability.

### 3.1.1 Experimental results of millimeter-wave low-noise amplifiers

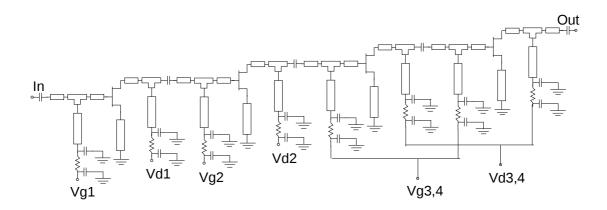

Two low-noise amplifiers for the W-band and D-band were designed [P9], [P10], [23], [1] and fabricated in a 100-nm GaAs-based metamorphic HEMT technology from Fraunhofer IAF, Freiburg, Germany. The simulation models were provided by Fraunhofer IAF. The simplified schematic and chip micrograph of the D-band amplifier are presented in Fig. 18 and Fig. 19, respectively. Both amplifiers were designed for wideband performance and flat gain response.

This was realized by using reactive matching elements implemented in grounded coplanar waveguides (GCPW) and using a double-resonance technique for interstage matching. The input is matched using a 30- $\Omega$  series line and a short-circuited shunt stub. The interstage matching can be divided into two parts. The drain of the transistor is loaded with a long 50- $\Omega$  series line and a short-circuited shunt stub. The interstage matching is completed with a quarter-wavelength 30- $\Omega$  series line and a short-circuited shunt stub. Inductive series feedback is used in every stage to stabilize the amplifiers.

Fig. 18. Simplified schematic of the D-band amplifier.

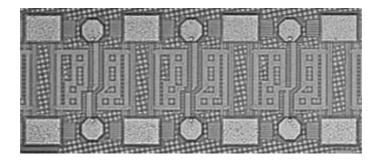

Fig. 19. Micrograph of the D-band amplifier. The chip size is 1.00 mm x 2.25 mm.

A comparison of published W-band and D-band HEMT MMIC amplifiers is presented in Table 1 and Table 2, respectively. The measured results demonstrate excellent noise and gain performance. In addition, both amplifiers were packaged in a split block package and the W-band packaged amplifier was measured at cryogenic temperatures.

Table 1. Comparison of published HEMT MMIC amplifiers for W-band.

| Frequency Gain NF Techn<br>[GHz] [dB] [dB] |       | Technology | Ref.                        |      |

|--------------------------------------------|-------|------------|-----------------------------|------|

| 95                                         | 20    | 2.5        | InP HEMT                    | [24] |

| 94                                         | 18    | 2.9        | InP HEMT                    | [25] |

| 94                                         | 33    | 3.2        | 130-nm InP HEMT             | [26] |

| 94                                         | 16    | 3.2        | 100-nm InP HEMT             | [27] |

| 94                                         | 12    | 3.3        | 100-nm InP HEMT             | [28] |

| 94                                         | 19.4  | 2.5        | 100-nm InP HEMT             | [29] |

| 65-86                                      | 26-30 | 3.1        | 35-nm InP HEMT              | [30] |

| 90                                         | 17    | 2.8        | GaAs MHEMT                  | [31] |

| 89                                         | 14    | 4.8        | 100-nm GaAs MHEMT           | [32] |

| 80-100                                     | 12    | 2.3        | 70-nm GaAs MHEMT            | [33] |

| 70-105                                     | 20    | 2.5        | 70-nm GaAs MHEMT            | [34] |

| 80-100                                     | 20    | 2.5        | 70-nm GaAs MHEMT            | [35] |

| 94                                         | 31    | 4.0        | 100-nm GaAs low noise PHEMT | [36] |

| 90-100                                     | 10.3  | 3.6        | 100-nm GaAs power PHEMT     | [37] |

| 94                                         | 11    | 5.4        | 100-nm InAs/AlSb HEMT       | [38] |

| 94                                         | 20    | 3.9        | 200-nm InAs/AlSb HEMT       | [39] |

| 94                                         | 22.5  | 3.3        | 100-nm GaAs MHEMT           | [P9] |

Table 2. Comparison of published HEMT MMIC amplifiers for D-band.

|                    |              | -          |                  |                   |       |

|--------------------|--------------|------------|------------------|-------------------|-------|

| Frequency<br>[GHz] | Gain<br>[dB] | NF<br>[dB] | Number of Stages | Technology        | Ref.  |

| 160                | 16           | 3.6        | 3                | 35-nm InP HEMT    | [40]  |

| 150-220            | 18-26        | -          | 3                | 50-nm InP HEMT    | [41]  |

| 150-215            | 12           | -          | 3                | 70-nm InP HEMT    | [42]  |

| 150-215            | 20±6         | 8          | 6                | 80-nm InP HEMT    | [43]  |

| 150-205            | 17±2         | -          | 8                | 100-nm InP HEMT   | [44]  |

| 140                | 30           | -          | 3                | 100-nm InP HEMT   | [45]  |

| 90-140             | 15±3         | -          | 6                | 100-nm InP HEMT   | [46]  |

| 150                | 5            | -          | 1                | 120-nm InP HEMT   | [47]  |

| 164                | 6            | -          | 2                | 70-nm InP PHEMT   | [48]  |

| 120-124            | 10-12        | -          | 2                | 100-nm InP PHEMT  | [49]  |

| 142                | 9            | -          | 2                | 100-nm InP PHEMT  | [50]  |

| 155                | 10.1         | 5.1        | 3                | 100-nm InP PHEMT  | [51]  |

| 148                | 12           | -          | 2 cascode stages | 150-nm GaAs PHEMT | [52]  |

| 155-160            | 15           | -          | 2 cascode stages | 70-nm GaAs MHEMT  | [53]  |

| 140-160            | 20           | 4.5        | 4                | 70-nm GaAs MHEMT  | [35]  |

| 180-220            | 16           | 4.8        | 4                | 50-nm GaAs MHEMT  | [54]  |

| 130-154            | 18.0-19.0    | 5.5-7.0    | 4                | 100-nm GaAs MHEMT | [P10] |

# 3.2 Millimeter-wave power amplifiers

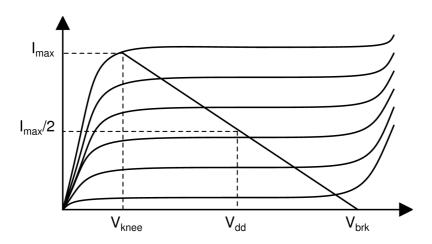

In power amplifier design, a suitable load impedance is presented to the transistor for delivering maximum output power. The maximum output power of a device in Class A can be derived from the load line theory [55]. The optimum load line can be calculated from the I-V characteristics of the transistor, as shown in Fig. 20. The maximum output power of a FET is delivered to the load when the output current  $I_{swing}$  and voltage swings  $V_{swing}$  are maximized. The optimum load line resistance  $R_{opt}$  is therefore

$$R_{opt} = \frac{V_{swing}}{I_{swing}} = \frac{V_{brk} - V_{knee}}{I_{max}} = \frac{2(V_{dd} - V_{knee})}{I_{max}}$$

$$(9)$$

It can be seen that the maximum voltage swing of a FET is limited by the device breakdown voltage  $V_{brk}$  and the transistor knee voltage  $V_{knee}$ . If the supply voltage  $V_{dd}$  is fixed, it might limit the swing. As the  $V_{brk}$  (or the  $V_{dd}$ , according to the specifications of the system) is fixed for each process, a larger current swing is needed to achieve higher output power. The current swing can be increased by using a larger device. This can be accomplished by placing identical devices in parallel. In principle, increasing the device size this way does not affect the gain performance of the transistor. However, the increased parasitics of the realized FET start to reduce the gain of the device and eventually, when the size of the device becomes significant when compared to the wavelength, the phase errors between the gate fingers start to reduce the gain performance.

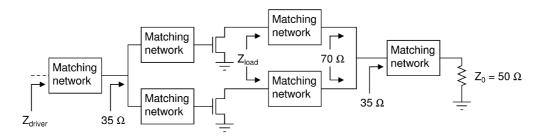

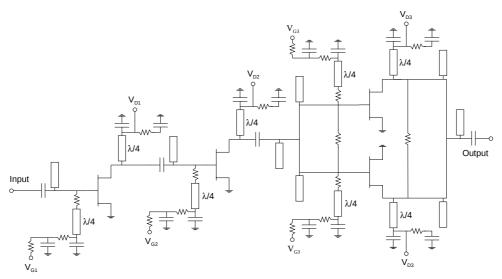

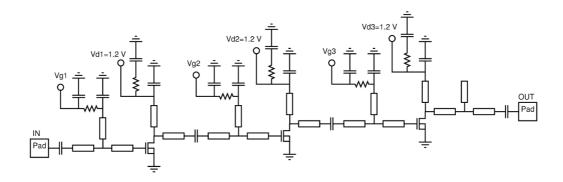

Fig. 20. I-V-characteristics and optimum load line of a FET.