#### Publication P5

Mika Kämäräinen, Matti Paavola, Mikko Saukoski, Erkka Laulainen, Lauri Koskinen, Marko Kosunen, and Kari Halonen. 2008. A 1.5 $\mu$ W 1V 2<sup>nd</sup>-order  $\Delta\Sigma$  sensor front-end with signal boosting and offset compensation for a capacitive 3-axis micro-accelerometer. In: Digest of Technical Papers of the 2008 IEEE International Solid-State Circuits Conference (ISSCC 2008). San Francisco, CA, USA. 3-7 February 2008. Pages 578-579, 637. ISBN 978-1-4244-2011-7.

© 2008 Institute of Electrical and Electronics Engineers (IEEE)

Reprinted, with permission, from IEEE.

This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of the Aalto University School of Science and Technology's products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org.

By choosing to view this document, you agree to all provisions of the copyright laws protecting it.

### **ISSCC 2008 / SESSION 32 / MEMS & SENSORS / 32.2**

# 32.2 A $1.5\mu W$ 1V $2^{nd}$ -Order $\Delta \Sigma$ Sensor Front-End with Signal Boosting and Offset Compensation for a Capacitive 3-Axis Micro-Accelerometer

Mika Kämäräinen, Matti Paavola, Mikko Saukoski, Erkka Laulainen, Lauri Koskinen, Marko Kosunen, Kari Halonen

Helsinki University of Technology, Espoo, Finland

The advantages of capacitive accelerometers [1], such as zero static bias current and the capability of achieving high sensitivity, are emphasized in ultra-low-power applications. In [1], representing the current state-of-the-art in low-power 3-axis micro-accelerometers, capacitance-to-voltage and A/D conversions were performed separately. In this paper, an ultra-low-power  $2^{\rm nd}$ -order  $\Delta\Sigma$  sensor front-end with inherent capacitance-to-digital conversion [2] for a capacitive 3-axis micro-accelerometer is presented. The front-end is designed for 1V operation and 12b accuracy with a 1Hz BW using a  $0.25\mu m$  CMOS technology.

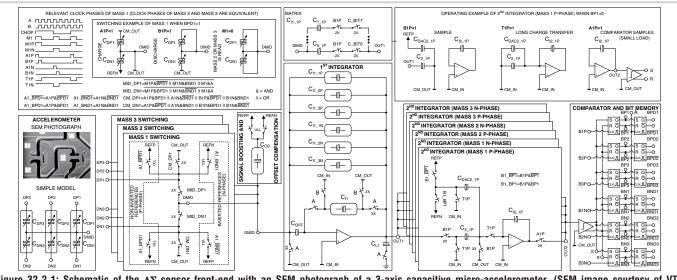

The schematic of the  $\Delta\Sigma$  sensor front-end with the sensor element is shown in Fig. 32.2.1. The capacitive acceleration information from each proof mass is first converted to a charge and then to a bit stream. In order to achieve sufficient (>20dB) mechanical attenuation of folding out-of-band interferers, a minimum  $f_s$  of 2kHz per mass was chosen. Chopper stabilization (CS) and CDS are implemented in order to reduce the offset voltage and noise of the front-end. The 1st integrator stage has to use time-multiplexing because of the common middle electrode of the proof masses. The use of six parallel integrators (one for each mass and chop phase) in the  $2^{\rm nd}$  stage makes possible the use of longer settling times, thus reducing power dissipation. To keep the implementation simpler, one comparator is multiplexed between the outputs of the  $2^{\rm nd}$  integrators.

The  $\Delta\Sigma$  front-end balances charge (i.e., ensures an equal average charge in both positive and negative detection capacitances) and thus reduces the distorting effects of the nonlinear electrostatic forces. Additionally, the transfer function is of the form  $(C_{\mbox{\scriptsize DP}}$  - $C_{DN}$  /( $C_{DP}$  +  $C_{DN}$ ), which cancels the nonlinearity of the displacement-to-capacitance conversion to the first order. The front-end uses two main clock phases, A and B, and three main mass selection phases, Mn, n being the index of the proof mass. In phase A, the mass being read is charged to a proper reference voltage and the 1st integrator samples the offset and flicker noise of the operational amplifier. Simultaneously, the 2nd integrator feeds the sampling capacitor of the comparator. In phase B, the charge of the mass being read is integrated in the 1st integrator and the 2nd integrator samples the new output voltage of the 1st integrator. Additionally, the comparator resolves a new output bit and the DAC capacitor of the 2<sup>nd</sup> integrator is charged to either reference voltage as determined by the new output bit. The 2nd integrator performs the charge transfer while the other masses are read.

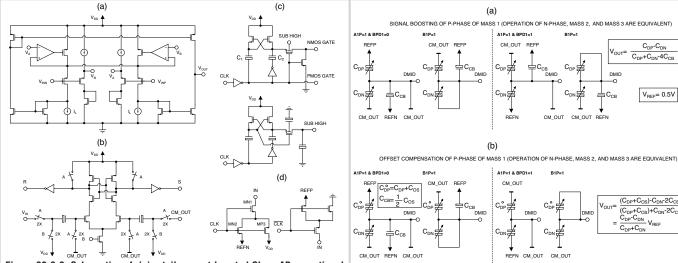

The positive and negative reference voltages (REFP/N) are equal to the supply and ground. Because of the low supply voltage of 1V, the input and output common-mode levels (CM\_IN/OUT) of the operational amplifiers are separated to 0.1 and 0.5V, respectively. The capacitor sizes in the 1st integrator are programmed to yield a gain of 0.5. To minimize power dissipation, a tail-current-boosted Class-AB operational amplifier (Fig. 32.2.2(a)) [3] is used in the  $1^{\rm st}$ integrator. The DC gain is increased by using the current sources I<sub>L</sub> [4]. The required feedback amplifiers are one-stage amplifiers with NMOS input pairs. The operational amplifier used in the 2<sup>nd</sup> integrators is a basic current mirror OTA, whose DC gain is increased with the same technique. The amplifiers were designed so that their biasing currents can be increased to enable a maxi- $\operatorname{mum} f_s$  of 51.2kS/s per mass. The simulated DC gains of the amplifiers of the 1st and 2nd integrators are approximately 50dB and 45dB, respectively. The dynamic latch with zero static power dissipation (Fig. 32.2.2(b)) [5] is used as a comparator.

A method to boost the available signal and to compensate for the offsets of the sensor capacitors was developed. The operating principle is shown in Fig. 32.2.3. The programmable capacitor matrix  $C_{CR}$  can be used to either source or sink charge from the sensor

middle electrode DMID. A single matrix is used for all three masses, with different programming. If charge is removed from both sides of the differential sensor capacitor pair, the denominator of the ratiometric transfer function is reduced and the signal is boosted. At the same time, the signal swing at the output of the 1st integrator is reduced, making low-voltage operation easier to achieve. If charge is sourced or sunk from only one side, the system compensates for any offset in the sensor capacitors. The signal boosting and offset compensation can also be used simultaneously.

Because of the low supply voltage, the use of floating switches is not possible without boosting the gate voltages. Therefore, the gate voltage of an NMOS device in a floating transmission gate is increased to  $2 \cdot V_{DD}$  using charge pumps (Fig. 32.2.2(c)) [6]. To minimize the silicon area, the number of gate-voltage-boosted floating switches was kept as low as possible. Other switches were implemented as single N- or P-MOS devices. The symbol  $2\times$  is used to indicate the gate-voltage-boosted switches in Fig. 32.2.1. The area required by the charge pumps is minimized by driving all the switches operating on the same clock phase with a single pump, and by sizing  $C_1 << C_2$  in each pump.

As the sampling frequency is low, the leakage currents of off-state switches must be minimized in order to prevent signal distortion and temperature-dependent offset. The primary source of leakage is the subthreshold current, which was minimized by using a non-minimum channel length to increase the threshold voltage whenever there is a voltage drop over an off-state switch. Additionally, the sensor middle electrode DMID was identified as being especially sensitive to leakage currents. To minimize the leakage into this node, a special ultra-low-leakage switch (Fig. 32.2.2(d), denoted by ULL in Fig. 32.2.1) similar to that in [7] was developed. When CLK=0, then in the case of an NMOS switch, MN1 and MN2 are off, while MP3 pulls the middle node to the positive supply rail. The bulk effect increases the threshold voltage of MN1, significantly reducing the leakage current.

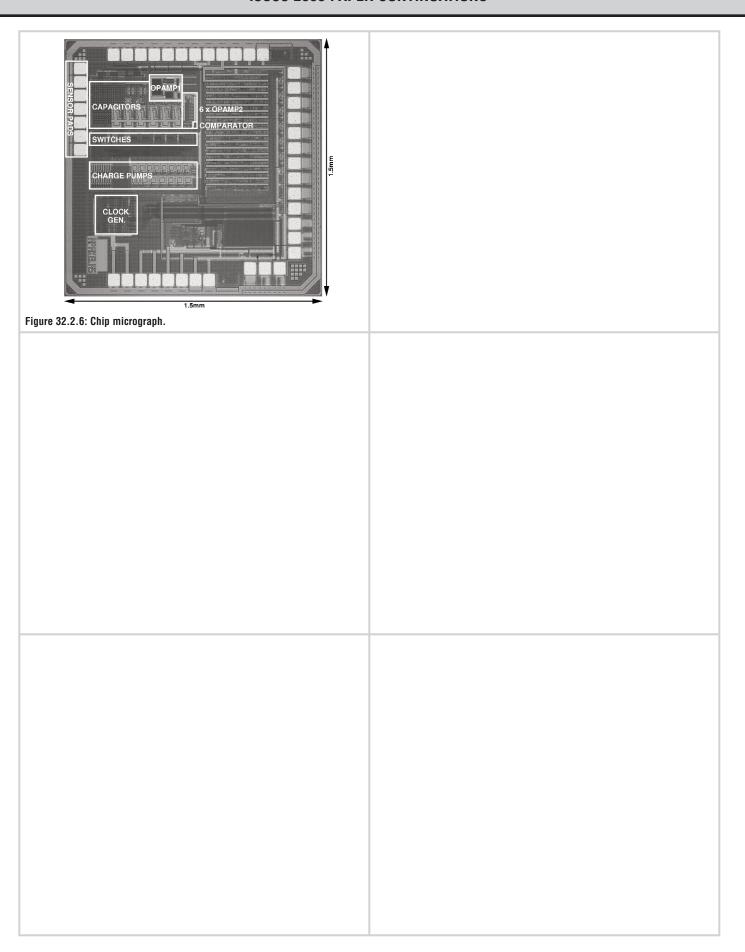

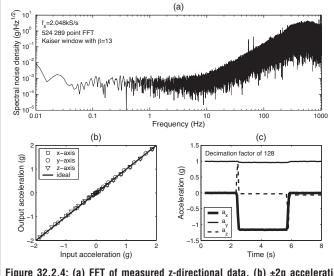

The prototype was fabricated with a 0.25µm CMOS technology with MIM capacitors. The silicon area of the front-end (Fig. 32.2.6) is 0.49mm². The chip was combined with an external ±2g capacitive 3-axis accelerometer on a PCB. The measurements were performed with off-chip references. An FFT of the measured z-directional data is shown in Fig. 32.2.4(a). The measured noise in the x, y and z directions with  $f_s = 2.048 \text{kS/s}$  per mass and chop phase is  $917 \mu \text{g/Hz}$ ,  $791 \mu \text{g/Hz}$  and  $704 \mu \text{g/Hz}$ , respectively. These results yield a DR of 72dB at a 1Hz BW. Figure 32.2.4(b) shows the ±2g acceleration ramps, and Fig. 32.2.4(c) an x-direction acceleration pulse, both measured using a rotating rate table. Because of smaller parasitic capacitances, the results are expected to improve when the front-end is bonded directly to the sensor.

This  $\Delta\Sigma$  sensor front-end IC draws 1.5µA from a 1V supply while sampling three proof masses, each at 4.096kS/s. The overall performance is summarized in Fig. 32.2.5.

## Acknowledgments:

We thank VTI Technologies, Vantaa, Finland for providing the sensor elements and funding, and the Finnish Funding Agency for Technology and Innovation (TEKES) for funding.

#### References:

[1] M. Paavola, M. Kämäräinen, J. Järvinen, M. Saukoski, M. Laiho, and K. Halonen, "A 62μA Interface ASIC for a Capacitive 3-Axis Micro-Accelerometer," *ISSCC Dig. Tech. Papers*, pp. 318–319, 2007.

[2] Y. Cao and G. Temes, "High-Accuracy Circuits for On-Chip Capacitance Ratio Testing or Sensor Readout," *IEEE T. CAS II*, pp. 637–639, Sept. 1994. [3] R. Harjani, R. Heineke, and F. Wang, "An Integrated Low-Voltage Class AB CMOS OTA," *IEEE J. Solid-State Circuits*, pp. 134–142, Feb. 1999. [4] L. Yao, M. Steyaert, and W. Sansen, "A 0.8-V, 8-µV, CMOS OTA with 50-150 Company."

[4] L. Yao, M. Steyaert, and W. Sansen, "A 0.8-V, 8-μW, CMOS OTA with 50-dB Gain and 1.2-MHz GBW in 18-pF Load," in *Proc. ESSCIRC*, pp. 297–300, 2003.

[5] T. Kobayashi, K. Nogami, T. Shirotori et al., "A Current-Controlled Latch Sense Amplifier and a Static Power-Saving Input Buffer for Low-Power Architecture," *IEEE J. Solid-State Circuits*, pp. 523–527, Apr. 1993.

[6] T. B. Cho and P. R. Gray, "A 10 b, 20 Msample/s, 35 mW Pipeline A/D

Converter," *IEEE J. Solid-State Circuits*, pp. 166–172, Mar. 1995. [7] K. Ishida, K. Kanada, A. Tamtrakarn et al., "Managing Subthreshold Leakage in Charge-Based Analog Circuits With Low-V<sub>TH</sub> Transistors by Analog T-Switch (AT-Switch) and Super Cut-Off CMOS (SCCMOS)," *IEEE J. Solid-State Circuits*, pp. 859–867, Apr. 2006.

# ISSCC 2008 / February 6, 2008 / 2:00 PM

Figure 32.2.1: Schematic of the  $\Delta\Sigma$  sensor front-end with an SEM photograph of a 3-axis capacitive micro-accelerometer. (SEM image courtesy of VTI Technologies, Vantaa, Finland)

Figure 32.2.2: Schematics of: (a) a tail-current-boosted Class-AB operational amplifier; (b) a dynamic latch; (c) charge pumps, and (d) an ultra-low-leakage NMOS (left) / PMOS (right) switch.

Figure 32.2.3: Operating principle of (a) signal boosting and (b) offset com-

| Figure | 32.2.4: | (a) FFT | of m  | neasured | z-direction  | al data | , (b) ±2g | acceleration | 1 |

|--------|---------|---------|-------|----------|--------------|---------|-----------|--------------|---|

| ramps, | and (c) | an x-di | ectio | nal acce | leration pul | se.     |           |              |   |

| Process                            | 0.25µm CMOS with MIM capacitors     |     |                    |        |  |

|------------------------------------|-------------------------------------|-----|--------------------|--------|--|

| Operating mode                     | With CS and CDS, no signal boosting |     |                    |        |  |

| Supply voltage                     | 1V                                  |     |                    |        |  |

| Power dissipation                  | 1.5µW                               |     |                    |        |  |

| Sampling frequency per mass        | 4.096kS/s                           |     |                    |        |  |

|                                    | x-axis                              | y-a | xis                | z-axis |  |

| Noise floor (µg/√Hz)               | 917                                 | 79  | 91                 | 704    |  |

| Current consumption / silicon area | (µA)                                |     | (mm <sup>2</sup> ) |        |  |

| Opamps                             | 1.4µA                               |     | 0.0358             |        |  |

| Comparator                         |                                     |     | 0.0006             |        |  |

| Charge pumps                       |                                     |     | 0.0727             |        |  |

| Switches                           |                                     |     | 0.0378             |        |  |

| Clock generator                    | 0.1µA                               |     | 0.0552             |        |  |

| Capacitors                         |                                     |     |                    | 0.1181 |  |

| • Wirings                          |                                     |     |                    | 0.1705 |  |

| Total                              | 1.5µA                               |     |                    | 0.4907 |  |

Figure 32.2.5: Summary of measured performance.

Continued on Page 637

V<sub>REF</sub>= 0.5V

(CDP+COS)-CDN-2CCB (C<sub>DP</sub>+C<sub>OS</sub>)+C<sub>DN</sub>-2C<sub>C</sub>

C<sub>DP</sub>-C<sub>DN</sub>

V<sub>REF</sub>

# **ISSCC 2008 PAPER CONTINUATIONS**