#### Publication P5

Matti Paavola, Mika Kämäräinen, Erkka Laulainen, Mikko Saukoski, Lauri Koskinen, Marko Kosunen, and Kari Halonen. 2008. A 21.2 $\mu$ A  $\Delta\Sigma$ -based interface ASIC for a capacitive 3-axis micro-accelerometer. In: Proceedings of the 2008 IEEE Asian Solid-State Circuits Conference (A-SSCC 2008). Fukuoka, Japan. 3-5 November 2008. Pages 101-104. ISBN 978-1-4244-2605-8.

© 2008 Institute of Electrical and Electronics Engineers (IEEE)

Reprinted, with permission, from IEEE.

This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of the Aalto University School of Science and Technology's products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org.

By choosing to view this document, you agree to all provisions of the copyright laws protecting it.

# A 21.2 $\mu A$ $\Delta \Sigma$ -Based Interface ASIC for a Capacitive 3-Axis Micro-Accelerometer

Matti Paavola<sup>1</sup>, Mika Kämäräinen<sup>1</sup>, Erkka Laulainen<sup>1</sup>, Mikko Saukoski<sup>1,2</sup>, Lauri Koskinen<sup>1</sup>, Marko Kosunen<sup>1</sup>, and Kari Halonen<sup>1</sup>

<sup>1</sup>SMARAD-2/Electronic Circuit Design Laboratory, Helsinki University of Technology, Espoo, Finland Email: mhpaavol@ecdl.tkk.fi

Abstract—In this paper, a micropower interface IC for a capacitive 3-axis micro-accelerometer implemented in a 0.25- $\mu m$  CMOS process is presented. The fully-integrated sensor interface consists of a  $\Delta\Sigma$  sensor front-end that converts the acceleration signal into the digital domain, a decimator, a frequency reference, a clock generator for the front-end, a voltage and current reference, the required reference buffers, and low-dropout regulators (LDOs) needed for system-on-chip power management. The interface IC provides operating modes for 1 and 25 Hz signal bandwidths. The chip with a  $1.72~mm^2$  active area draws  $21.2~\mu A$  in 1~Hz mode, and  $97.6~\mu A$  in 25~Hz mode, from a 1.2-2.75~V supply. In 1~Hz mode with a  $\pm 2$ -g capacitive 3-axis accelerometer, the measured noise floors in the x-, y-, and z-directions are  $1080,\,1165$  and  $930~\mu g/\sqrt{Hz}$ , respectively.

#### I. INTRODUCTION

Micro-accelerometers have a wide range of different applications, such as automotive safety and stability control systems, navigation, and movement detection and user interfaces in hand-held mobile terminals and in game controllers. The use of microsensors in battery-powered equipment requires the sensor interface to exhibit low power dissipation and to be able to operate from supply voltages varying over a wide range. In order to realize a low-power, high-performance accelerometer with a small silicon area, the readout electronics has to be integrated together with the sensor element at chip or packaging level, forming a microelectromechanical system (MEMS).

The advantages of capacitive accelerometers [1], such as zero static bias current, the capability of achieving high sensitivity, and excellent thermal stability, are emphasized in ultralow-power applications. In this paper, a fully-integrated low-voltage low-power sensor interface IC for a capacitive 3-axis micro-accelerometer will be presented. The system is based on the front-end circuit presented earlier by the authors in [2], and includes additionally a decimator, all the required reference circuits, and on-chip power management circuitry. The  $2^{\rm nd}$ -order  $\Delta\Sigma$  sensor front-end operates in open-loop configuration and performs inherent capacitance-to-digital conversion and charge balancing. The reasons for using an open-loop configuration are simple implementation that reduces both silicon area and power dissipation, and a limited voltage range available for electrostatic feedback.

The authors wish to thank VTI Technologies and the Finnish Funding Agency for Technology and Innovation (TEKES) for financial support.

<sup>2</sup>Starting from the year 2008, M. Saukoski has been with ELMOS Semi-conductor AG, Dortmund, Germany.

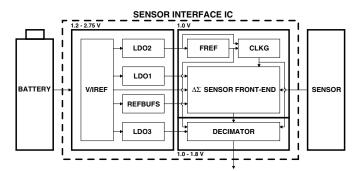

Fig. 1. Block diagram of the implemented interface IC for a capacitive 3-axis micro-accelerometer.

To make an operation over wide range of supply voltages  $(1.2-2.75\,V)$  required by the battery-powered system possible, low-dropout regulators (LDOs) were implemented for system-on-chip power management. LDOs have significant advantages, such as fast transient response, low-noise characteristic, low complexity, and no need for inductors. The implemented sensor interface provides operating modes for 1 and  $25\,Hz$  signal bandwidths. The former makes it possible to detect accelerations while maintaining low power dissipation, and the latter can be used to measure accelerations over a wider bandwidth.

The paper is organized as follows. The system architecture of the implemented sensor interface is briefly described in Section II. Different circuit blocks are presented in Section III and the measurement results of the implemented prototype are presented in Section IV. Finally, conclusions are drawn in Section V.

#### II. SYSTEM DESCRIPTION

A block diagram of the implemented sensor interface system is shown in Fig. 1. The  $\Delta\Sigma$ -type sensor front-end [2] converts the capacitive acceleration information from each of the three proof masses first to charge and then subsequently to a bit stream. The decimator, based on the implementation presented in [3], filters and decimates the single-bit outputs to the final desired bandwidth and accuracy. The frequency reference circuit (FREF) [4] provides the master clock signal for both the clock generator of the front-end (CLKG) and for the decimator. The CLKG then generates all the clock signals required by the front-end.

The voltage and current reference circuit (V/IREF) provides the main reference voltage and current, together with the bias voltages and currents required by the other circuit blocks. The

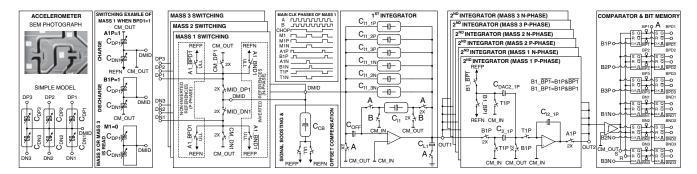

Fig. 2. Schematic of the  $\Delta\Sigma$  sensor front-end with an SEM photograph of a capacitive 3-axis micro-accelerometer. (SEM image courtesy of VTI Technologies, Vantaa, Finland).

reference voltage buffers (REFBUFs) are used to scale and buffer the reference voltage, and they provide the positive reference (REFP) and the common-mode output (CM\_OUT) and input (CM\_IN) voltages required by the front-end circuit. Two separate buffers were designed to optimize power dissipation in both 1 and  $25\,Hz$  operating modes.

Two LDOs were implemented to provide separate  $1.0\,V$  regulated supply voltages for the  $\Delta\Sigma$  sensor front-end and for the FREF and the CLKG. Additionally, the decimator had to be provided with an LDO of its own with programmable output voltage from 1.0 to  $1.8\,V$ , as the standard cell library used in the design was specified only for supply voltages down to  $1.8\,V$ . To avoid the use of impractical off-chip load capacitors and to guarantee the maximum tolerable output voltage drop of  $0.1\,V$ , the LDOs were equipped with programmable on-chip load capacitors up to  $1\,nF$ . Because of the low-power characteristic of the sensor interface, the LDOs must remain stable with zero load currents.

In order to reach a sufficient ( $>20\,dB$ ) mechanical attenuation of folding out-of-band interferers and low enough noise level for 12-bit resolution for a  $\pm 2$ -g dc acceleration signal in  $1\,Hz$  mode, a sampling frequency of  $4.096\,kHz$  per mass was chosen. With a full-scale input signal, the maximum signal-tonoise ratio of the sensor front-end would then be limited by thermal noise to 16 bits. However, the limited signal available from the  $\pm 2$ -g accelerometer limits the achievable dynamic range to 12 bits. In the  $25\,Hz$  mode, a sampling frequency of  $51.2\,kHz$  is required for the same resolution. The 16-bit accuracy is demanded also from the reference buffers. This has an adverse effect on the current consumption of the REFBUFs.

The attenuation of the used  $\mathrm{sinc}^3$  decimation filters is not allowed to be greater than  $3\,dB$  at the edge of the passband. Thus, the output data rate of the decimator was chosen to be 4 and  $100\,Hz$  in the 1 and  $25\,Hz$  modes, respectively. Because of the absence of analog gain control before the A/D conversion, the decimator is equipped with shifters for gain control and 16-bit wide serial outputs to maintain the resolution even at the presence of uncompensated offsets.

## III. CIRCUIT DESCRIPTION

#### A. $\Delta\Sigma$ Sensor Front-End

The schematic of the  $\Delta\Sigma$  sensor front-end with the sensor element is shown in Fig. 2. The front-end balances charge,

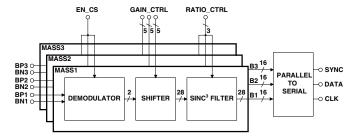

Fig. 3. Simplified block diagram of the decimator.

in other words it ensures an equal average charge in both positive and negative detection capacitances, and thus reduces the distorting effects of the nonlinear electrostatic forces. The resulting transfer function from acceleration to bit stream is of the form  $(C_{DP}-C_{DN})/(C_{DP}+C_{DN})$ , which cancels the nonlinearity of the displacement-to-capacitance transducer to the first order. Chopper stabilization (CS) and correlated double sampling (CDS) are implemented in order to reduce the offset voltage and noise of the front-end.

The operation principle of the front-end is described in detail in [2]. The positive and negative reference voltages are equal to the supply and ground. Because of the low supply voltage of  $1.0\,V$ , the input and output common-mode levels of the operational amplifiers are separated to 0.1 and  $0.5\,V$ , respectively. To minimize power dissipation, a tail-current-boosted Class-AB operational amplifier [5] with enhanced dc gain [2] is used in the  $1^{\rm st}$  integrator. The operational amplifier used in the  $2^{\rm nd}$  integrators is a basic current mirror OTA, whose dc gain is enhanced with the same technique. The simulated dc gains of the two amplifiers are approximately 50 and  $45\,dB$ , respectively. A dynamic latch with zero static power dissipation is used as a comparator.

The programmable capacitor matrix  $C_{CB}$  can be used to sink charge from the sensor middle electrode DMID. It makes possible both boosting the available signal and compensating the offsets of the sensor capacitors [2]. Because of the low supply voltage, the gate voltage of an NMOS device in a floating transmission gate is increased to  $2 \cdot V_{DD}$  using charge pumps [2]. The symbol 2x is used to indicate the gate-voltage-boosted switches in Fig. 2. As the node DMID is especially sensitive to leakage currents, a special ultra-low-leakage switch [2] denoted by ULL in Fig. 2 was developed.

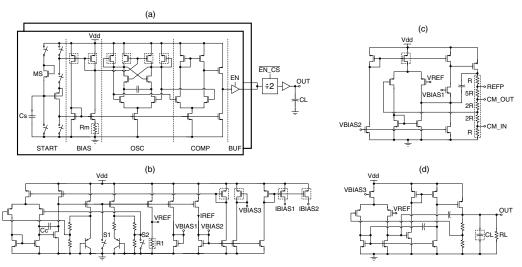

Fig. 4. Schematics of: (a) a frequency reference; (b) a voltage and current reference; (c) a reference voltage buffer, and (d) an LDO.

#### B. Decimator

The simplified block diagram of the designed decimator based on three parallel sinc<sup>3</sup> filters [3], one for each proof mass, is shown in Fig. 3. Three-stage cascaded integratorcomb (CIC) filters with one sample delays and selectable rate change factor are used. Each of the filters has two 1bit inputs and a 16-bit wide output. When CS is not used, the filters use only one input. In the case of CS enabled, the demodulation is performed by subtracting the two input bits. After possible demodulations the signals can be scaled with shifters. The decimation ratio can be selected between 16 and 512, with each control step doubling the ratio. The outputs from the three filters are fed to a parallel-to-serial converter that outputs the 48  $(3 \times 16)$  bits. Based on the measurement results [3], the decimator operates nominally from a 1.0 Vsupply in  $1\,Hz$  mode, and from a  $1.8\,V$  supply in  $25\,Hz$  mode. The decimation ratios used are 512 and 256, respectively.

#### C. Reference Circuits and LDOs

The master clock frequency is  $24.576 \, kHz$  in  $1 \, Hz$  mode and  $307.2 \, kHz$  in  $25 \, Hz$  mode. The frequency reference that provides the master clock signal and which consists of two parallel source-coupled CMOS multivibrator-based structures is shown in Fig. 4 (a) [4]. Both modes require an independent frequency reference circuit because, due to the low supply voltage of 1.0 V, floating switches cannot be used, and therefore a sufficient frequency tuning range cannot be achieved by using capacitor matrices. Coarse tuning is implemented by using PMOS transistor matrices in the biasing circuits and in the multivibrators, while fine tuning is implemented with resistor matrix Rm (matrices marked with dashed boxes in Fig. 4). The devices Rm, MS, and Cs are common for the two frequency references. The used biasing circuits are proportionalto-absolute-temperature (PTAT) current generators. Two-stage differential comparators are used to magnify the oscillation amplitudes rail-to-rail, and tri-state buffers are used to interface the parallel frequency references to the divider consisting of two cascaded gated SR latches. The divide-by-two operation is enabled when CS is disabled.

The designed V/IREF shown in Fig. 4 (b) is based on the bandgap reference topology presented in [6], and it is suitable to be implemented with a standard CMOS process. A Miller-compensated operational amplifier with a PMOS input pair is used as the feedback amplifier. To allow the use of supply voltages down to 1.2 V, the input voltage levels of the operational amplifier are lowered with resistive voltage dividers. The effects of process variations on the output voltage level (VREF nominally 0.3 V) can be eliminated by trimming R1. To achieve a sufficient noise performance, the bandwidth of the bandgap reference is limited aggressively by using the compensation capacitor Cc of 50 pF. As a result, the bandwidths of the negative feedback loop and the closed loop are nominally 1.6 and  $11.0\,kHz$ , respectively. The NMOS switches S1 and S2 were included to provide a power-on-reset that can be used to force the bandgap reference to the right operating point, if needed. Programmable biasing currents IBIAS1 and IBIAS2 are used to bias the amplifiers of the  $\Delta\Sigma$  sensor front-end.

The two REFBUFs have identical schematics shown in Fig. 4 (c), but different device parameters. Time constants formed by the resistances of the resistive networks and the load capacitances from the front-end and the sensor element determine the settling accuracies.

The LDO shown in Fig. 4 (d) is based on the structure presented in [7]. It uses a Q-reduction technique to minimize both the required on-chip capacitance and the minimum output current. Nominally, the current of  $2.0\,\mu A$  flows through the feedback resistive network. The requirement for stability at zero load current  $(RL \to \infty)$  results in a small bandwidth of  $18.5\,kHz$  for the loop response. To minimize the silicon area required by the programmable  $1\,nF$  load capacitors metalinsulator-metal (MIM) capacitors were stacked above standard MOS capacitors.

## IV. MEASUREMENT RESULTS

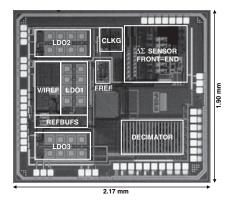

The prototype chip with a  $1.72 \, mm^2$  active core area shown in Fig. 5 was fabricated in a  $0.25 \text{-} \mu m$  CMOS technology.

Fig. 5. Microphotograph of the implemented chip.

TABLE I SUMMARY OF MEASURED PERFORMANCE.

| Process             | $0.25$ - $\mu m$ CMOS with MIM capacitors and high- |                 |                                     |

|---------------------|-----------------------------------------------------|-----------------|-------------------------------------|

|                     | resistivity polysilicon resistors                   |                 |                                     |

| Supply              | 1.2 - 2.75 V                                        |                 |                                     |

|                     | Two $1.0 V$ and one $1.0 - 1.8 V$ regulated on chip |                 |                                     |

| Configuration       | With CS and CDS                                     |                 |                                     |

|                     | Without signal boosting and offset compensation     |                 |                                     |

| Active area         | $1.72  mm^2$                                        |                 |                                     |

| Mode                | $1\mathrm{Hz}$                                      | $25\mathrm{Hz}$ |                                     |

| $f_s$ per mass      | 4.096                                               | 51.2            | kHz                                 |

| Current consumption |                                                     |                 |                                     |

| $I_{LDO1}^{a}$      | 14.5                                                | 84.3            | $\mu A$                             |

| $I_{LDO2}^{b}$      | 3.5                                                 | 5.2             | $\mu A$                             |

| $I_{LDO3}^{c}$      | 3.2                                                 | 8.1             | $\mu A$                             |

| Total               | 21.2                                                | 97.6            | $\mu A$                             |

| Noise floor         |                                                     |                 |                                     |

| x-axis              | 1080                                                | 340             | $\mu g/\sqrt{Hz} \ \mu g/\sqrt{Hz}$ |

| y-axis              | 1165                                                | 325             | $\mu g/\sqrt{Hz}$                   |

| z-axis              | 930                                                 | 275             | $\mu g/\sqrt{Hz}$                   |

$<sup>^</sup>a$ LDO1, V/IREF, REFBUFs, and  $\Delta\Sigma$  sensor front-end

For the measurements, the chip was encapsulated into a plastic quad flat package (QFP) with 64 pins and soldered onto a printed circuit board (PCB). The chip was combined with an external  $\pm 2\text{-}g$  capacitive 3-axis accelerometer on the PCB. The results presented below were measured for the complete system shown in Fig. 1, while the prior results of the  $\Delta\Sigma$  sensor front-end published in [2] were obtained using both off-chip decimator, and off-chip references and power management.

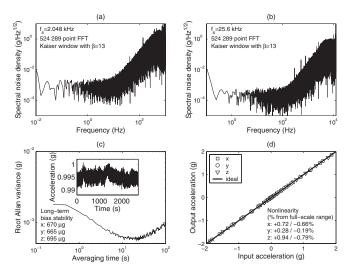

The performance measured for both modes using a  $2.5\,V$  supply voltage and  $0.5\,nF$  load capacitors at the outputs of the LDOs is summarized in Table I. All the results were measured by using both CS and CDS, but without using signal boosting or offset compensation. The core circuit consumes  $21.2\,\mu A$  in  $1\,Hz$  mode and  $97.6\,\mu A$  in  $25\,Hz$  mode. The noise results yield dynamic ranges of 70 and  $67\,dB$  for dc input signals in 1 and  $25\,Hz$  modes, respectively. FFTs measured from the output of the sensor front-end, for the x-directional data in  $1\,Hz$  mode and the z-directional data in  $25\,Hz$  mode, are shown in Figs. 6 (a)-(b). The root Allan variance for the y-directional data and the  $\pm 2$ -g acceleration ramps, both measured from the decimator output in  $1\,Hz$  mode, are shown in Figs. 6 (c)-(d). The ramps were measured using a rotating

Fig. 6. FFTs of measured (a) x-directional data in  $1\,Hz$  mode and (b) z-directional data in  $25\,Hz$  mode, and measured (c) root Allan variance for y-directional data and (d)  $\pm 2$ -g acceleration ramps in  $1\,Hz$  mode.

rate table. The results are expected to improve when the interface IC is bonded directly to the sensor.

#### V. CONCLUSION

In this paper, a micropower  $\Delta\Sigma$ -based interface IC for a capacitive 3-axis micro-accelerometer implemented in a  $0.25\text{-}\mu m$  CMOS process was presented. In  $1\,Hz$  mode, the chip with a  $1.72\,mm^2$  active area draws  $21.2\,\mu A$  from a  $1.2-2.75\,V$  supply while sampling three proof masses, each at  $4.096\,kHz$ . With a  $\pm 2\text{-}g$  capacitive 3-axis accelerometer, the measured noise floors in the x-, y-, and z-directions are 1080, 1165 and  $930\,\mu g/\sqrt{Hz}$ , respectively. Compared to the open-loop sensor interface of [1] which includes separate capacitance-to-voltage and voltage-to-digital conversions, the presented measurement results prove that by using both open-loop configuration and inherent capacitance-to-digital conversion, an alternative low-voltage low-power sensor interface can be implemented.

# [1] M. Paavola, M. Kämäräinen, J. Järvinen, M. Saukoski, M. Laiho, and

- K. Halonen, "A micropower interface ASIC for a capacitive 3-axis micro-accelerometer," *IEEE J. Solid-State Circuits*, vol. 42, no. 12, pp. 2651–2665, Dec. 2007.

- [2] M. Kämäräinen, M. Paavola, E. Laulainen, M. Saukoski, L. Koskinen, M. Kosunen, and K. Halonen, "A 1.5μW 1V 2<sup>nd</sup>-order ΔΣ sensor frontend with signal boosting and offset compensation for a capacitive 3-axis micro-accelerometer," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2008, pp. 578–579.

- [3] E. Laulainen, M. Kosunen, L. Koskinen, M. Paavola, and K. Halonen, "Decimation filter for a low-power sensor-interface system," in *Proc. IEEE Norchip Conf.*, Aalborg, Denmark, Nov. 2007.

- [4] M. Paavola, M. Saukoski, M. Laiho, and K. Halonen, "A nanopower double-mode 1-V frequency reference for an ultra-low-power capacitive sensor interface," in *Proc. IEEE Eur. Conf. Circuit Theory and Design*, Sevilla, Spain, Aug. 2007, pp. 104–107.

- [5] R. Harjani, R. Heineke, and F. Wang, "An integrated low-voltage class AB CMOS OTA," *IEEE J. Solid-State Circuits*, vol. 34, no. 2, pp. 134–142, Feb. 1999.

- [6] K. N. Leung and P. K. T. Mok, "A sub-1-V 15-ppm/°C CMOS bandgap voltage reference without requiring low threshold voltage device," *IEEE J. Solid-State Circuits*, vol. 37, no. 4, pp. 526–530, Apr. 2002.

- [7] S. K. Lau, P. K. T. Mok, and K. N. Leung, "A low-dropout regulator for SoC with Q-reduction," *IEEE J. Solid-State Circuits*, vol. 42, no. 3, pp. 658–664, Mar. 2007.

<sup>&</sup>lt;sup>b</sup>LDO2, FREF, and CLKG

<sup>&</sup>lt;sup>c</sup>LDO3 and decimator