# Reliability assessment of electronic assemblies under multiple interacting loading conditions

**Juha Karppinen**

# Aalto University publication series **DOCTORAL DISSERTATIONS** 19/2013

Reliability assessment of electronic assemblies under multiple interacting loading conditions

Juha Karppinen

A doctoral dissertation completed for the degree of Doctor of Science (Technology) to be defended, with the permission of the Aalto University School of Electrical Engineering, at a public examination held at the lecture hall S1 of the school on 14th of February 2013 at 12 o'clock.

Aalto University

School of Electrical Engineering

Department of Electronics

Unit of Electronics Integration and Reliability

# Supervising professor

Prof. Mervi Paulasto-Kröckel

# Thesis advisors

Prof. Tomi Laurila

Docent Toni Mattila

# **Preliminary examiners**

Dr. Pascal Oberndorff, Philips Lighting, Eindhoven, The Netherlands Dr. Olaf Wittler, Fraunhofer Institut für Zuverlässigkeit und Mikrointegration, Berlin, Germany

# **Opponents**

Dr. Pascal Oberndorff, Philips Lighting, Eindhoven, The Netherlands Dr. Changqing Liu, Loughborough University, The United Kingdom

Aalto University publication series **DOCTORAL DISSERTATIONS** 19/2013

© Juha Karppinen

ISBN 978-952-60-4995-3 (printed)

ISBN 978-952-60-4996-0 (pdf)

ISSN-L 1799-4934

ISSN 1799-4934 (printed)

ISSN 1799-4942 (pdf)

http://urn.fi/URN:ISBN:978-952-60-4996-0

Unigrafia Oy Helsinki 2013

Finland

# Aalto University, P.O. Box 11000, FI-00076 Aalto www.aalto.fi

# Author

# Juha Karppinen

# Name of the doctoral dissertation

Reliability assessment of electronic assemblies under multiple interacting loading conditions

**Publisher** School of Electrical Engineering

Unit Department of Electronics

Series Aalto University publication series DOCTORAL DISSERTATIONS 19/2013

Field of research Electronics integration and reliability

Manuscript submitted 17 September 2012 Date of the defence 14 February 2013

Permission to publish granted (date) 14 December 2012 Language English

□ Article dissertation (summary + original articles) Monograph

### **Abstract**

This dissertation presents the results of multiple experimental and computational reliability assessment methods employed on electronic assemblies. It is demonstrated that the typical standardized test procedures often fail to capture the complex loading conditions of service environment and can lead to artificial results due to excessive damage acceleration. An alternative reliability assessment approach based on the use of combined loading tests derived from product service loading characterization is proposed as a solution to the problem. In this proposed approach special attention is paid to establishing a stronger correlation between the material-scientific reliability analyses and lifetime prediction methods.

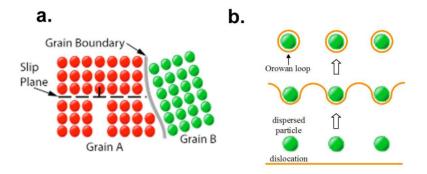

Several methods on how to predict and characterize the reliability of component assemblies under different use cases and field environments are presented. Particular emphasis is placed on the reliability of board-level solder interconnections due to their complex and often unsatisfactory reliability behavior. It is shown that multiple microstructural mechanisms, such as dispersion strengthening, grain growth, strain rate hardening, fatigue and recrystallization, contribute together to the reliability performance of interconnections. The presented relationships between these mechanisms and the affecting loading conditions enable more accurate and comprehensive assessment of electronic product reliability.

Keywords Combined load testing, electronic assembly, solder interconnection, mechanical load, electrical load, thermal load, thermal cycling

| ISBN (printed) 978-952-60- | 1995-3 <b>ISBN (pdf)</b> 978- | 952-60-4996-0             |

|----------------------------|-------------------------------|---------------------------|

| ISSN-L 1799-4934           | ISSN (printed) 1799-4934      | ISSN (pdf) 1799-4942      |

| Location of publisher Espo | Location of printing          | Helsinki <b>Year</b> 2013 |

| Pages 160                  | urn http://urn.fi/U           | RN:ISBN:978-952-60-4996-0 |

| е |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

Juha Karppinen

# Väitöskirjan nimi

Elektronisten kokoonpanojen luotettavuuden arviointi useiden vuorovaikuttavien rasitustilojen alaisuudessa

Julkaisija Sähkötekniikan korkeakoulu

Yksikkö Elektroniikan laitos

Sarja Aalto University publication series DOCTORAL DISSERTATIONS 19/2013

Tutkimusala Elektroniikan integrointi ja luotettavuus

Käsikirjoituksen pvm 17.09.2012 Väitöspäivä 14.02.2013

Julkaisuluvan myöntämispäivä 14.12.2012 Kieli Englanti

### Tiivistelmä

Tässä väitöstyössä esitellään tulokset useiden eri kokeellisten ja laskennallisten luotettavuuden arviointimenetelmien sovellutuksista elektronisiin kokoonpanoihin. Tulokset osoittavat että perinteiset standardisoidut testimenetelmät eivät useinkaan anna oikeaa kuvaa nykyaikaisten tuotteiden monimutkaisien käyttöympäristöjen aiheuttamista kuormituksista, ja ne voivat johtaa karkeisiin arviointivirheisiin testeissä käytettyjen liiallisten kiihdytystekijöiden vuoksi. Ongelman ratkaisemiseksi tässä työssä esitellään vaihtoehtoinen yhdistelmätestaukseen perustuva luotettavuuden arviointimenetelmä, jossa tuotteiden todelliset käytönaikaiset rasitukset on huomioitu aiempaa todenmukaisemmin. Ehdotetussa menetelmässä kiinnitetään erityistä huomiota vahvempien riippuvuussiteiden luomiseksi materiaaliteknisten luotettavuusanalyysien ja laskennallisten elinikämallinnusten välille.

Esitelty luotettavuuden arviointimenetelmä sisältää useampia koetapoja, joiden avulla voidaan karakterisoida ja ennustaa piirilevykokoonpanojen luotettavuutta erilaisissa käyttöympäristöissä. Uuden menetelmän kehityksessä on kiinnitetty erityisesti huomiota piirilevytason juoteliitoksien luotettavuuteen, sillä näiden liitosten käyttäytyminen erilaisten rasitustilojen alaisuudessa on monimutkaista ja ne muodostavat kokoonpanoissa usein luotettavuusriskin. Työssä havainnollistetaan miten useat mikrorakenteelliset mekanismit, kuten erkautumislujittuminen, rakeenkasvu, muodonmuutosnopeuslujittuminen, väsyminen ja uudelleenkiteytyminen, vaikuttavat yhtäaikaisesti juoteliitosten kykyyn kestää rasituksia. Havaintojen pohjalta esitettyjen mikrorakenteellisten mekanismien ja vaikuttavien kuormitustekijöiden välisten vuorovaikutussuhteiden ymmärtäminen mahdollistaa kokonaisvaltaisemman ja tarkemman luotettavuusanalyysin toteuttamisen elektroniikkatuotteille.

**Avainsanat** Yhdistelmärasitustestaus, juoteliitos, elektroninen kokoonpano, mekaaninen kuormitus, sähköinen kuormitus, lämpökuormitus

| ISBN (painettu) 978-952- | 60-4995-3       | ISBN (pdf) 978-9  | 952-60-4996-0            |

|--------------------------|-----------------|-------------------|--------------------------|

| ISSN-L 1799-4934         | ISSN (painettu) | 1799-4934         | ISSN (pdf) 1799-4942     |

| Julkaisupaikka Espoo     | Painor          | oaikka Helsinki   | Vuosi 2013               |

| Sivumäärä 160            | urn             | http://urn.fi/URN | V:ISBN:978-952-60-4996-0 |

# **Preface**

This work has been conducted in the Electronics Integration and Reliability unit under the Department of Electronics at Aalto University. The work was financially supported by two projects, 'CRT' and 'Electromigration', which were funded by the Finnish Funding Agency for Technology and Innovation (TEKES), Academy of Finland, Nokia, Nokia Siemens Networks, Efore Plc, NXP Semiconductors, Salon Teknopaja Oy and the National Semiconductor Corporation.

I am grateful to my supervisor Professor Mervi Paulasto-Kröckel, and my previous supervisor Professor Jorma Kivilahti. Without their advice, encouragement and support, this dissertation would not have been possible.

I wish to especially thank both my instructors, Dr. Toni Mattila and Dr. Tomi Laurila for their guidance, suggestions and willingness to enter into insightful discussion at any time.

I also wish to thank all my colleagues in the unit of Electronics Integration and Reliability, especially Dr. Vesa Vuorinen, Dr. Markus Turunen, Dr. Jue Li and Mr. Jussi Hokka. The daily discussions with them have helped me conquer numerous obstacles during the past five years. I am also very grateful to Ms. Pia Holmberg, Ms. Pirjo Kontio, Mr. Esa Kurhinen, Ms. Leena Väisänen, and Ms. Iina Nahkuri for their time and kind assistance.

Finally, I would like to present my loving thanks to my family for their endless love and patience. My parents also deserve special thanks for providing unfaltering encouragement and support throughout my life.

Espoo, 2013

Juha Karppinen

# **Contents**

| Pr  | eface   | ••••••     |                                                 | 1      |

|-----|---------|------------|-------------------------------------------------|--------|

| Co  | nten    | ts         |                                                 | 2      |

| Lis | st of ] | Publicati  | ions                                            | 4      |

| Au  | ıthor   | s contri   | bution                                          | 6      |

| Lis | st of A | Abbrevia   | ations and Symbols                              | ·····7 |

| 1   | Intr    | oductio    | n                                               | 9      |

| 2   | Bac     | kground    | on reliability challenges                       | 11     |

|     | 2.1     | Therma     | l loading                                       | 13     |

|     | 2.2     | Mechan     | ical loading                                    | 15     |

|     | 2.3     | Electrica  | al loading                                      | 17     |

|     | 2.4     | Single lo  | oad – multiple stress conditions                | 19     |

| 3   | The     | assemb     | ly-level reliability design process             | 21     |

|     | 3.1     | Critical a | assembly-level assessment of loading conditions | 24     |

|     | 3.2     | Accelera   | ited test design                                | 28     |

|     |         | 3.2.1      | Γhermal- and thermomechanical tests             | 29     |

|     |         | 3.2.2 I    | Mechanical tests                                | 31     |

|     |         | 3.2.3 I    | Electrical tests                                | 32     |

|     | 3.3     | Combin     | ed loading test design                          | 33     |

|     |         | 3.3.1      | Consecutive tests                               | 35     |

|     |         | 3.3.2      | Concurrent tests                                | 37     |

| 4   | Life    | time est   | imation                                         | 40     |

|     | 4.1     | Tempera    | ature-dependent damage processes                | 41     |

|         | 4.2  | Consid   | derations on life prediction accuracy                             | . 45 |

|---------|------|----------|-------------------------------------------------------------------|------|

|         | 4.3  | Comb     | ination of damage models for multiparameter loading               | 46   |

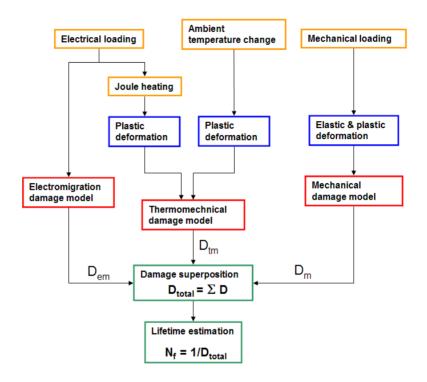

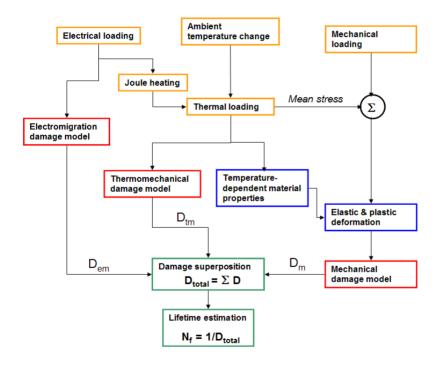

|         |      | 4.3.1    | Linear damage superpositioning (LDSA)                             | 46   |

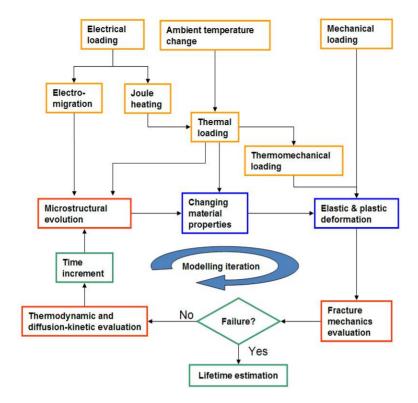

|         |      | 4.3.2    | Incremental damage superpositioning (IDSA)                        | . 47 |

|         | 4.4  | Micro    | mechanical physics of failure approach for lifetime analysis      | 48   |

| 5       | Reli | iability | of lead-free SnAgCu solder interconnections                       | . 52 |

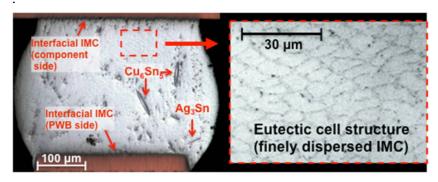

|         | 5.1  | Micro    | structure and its evolution in solder interconnections            | . 53 |

|         |      | 5.1.1    | Solidification structure (after reflow)                           | . 53 |

|         |      | 5.1.2    | Effect of solidification structure on properties of SnAgCu solder | . 54 |

|         |      | 5.1.3    | Evolution of solder microstructure under service                  | . 55 |

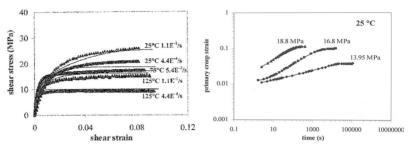

|         | 5.2  | Mecha    | anical properties of SnAgCu solder interconnections               | .58  |

|         |      | 5.2.1    | Plastic deformation                                               | 58   |

|         |      | 5.2.2    | Strain rate hardening                                             | . 59 |

|         |      | 5.2.3    | Fracture                                                          | . 59 |

|         |      | 5.2.4    | Fatigue                                                           | 61   |

|         |      | 5.2.5    | Anisotropy                                                        | .62  |

|         | 5.3  | Summ     | nary of observed SnAgCu solder interconnection behavior un        | ıder |

|         |      | combi    | ned reliability test cases                                        | .62  |

| 6<br>Re |      |          |                                                                   |      |

# **List of Publications**

This thesis consists of an overview of the following publications, which are referred to in the text by their Roman numerals.

- I Laurila, T., Karppinen, J., Vuorinen, V., Li, J., Paul, A. and Paulasto-Kröckel, M.; "Effect of Isothermal Aging and Electromigration on the Microstructural Evolution of Solder Interconnections During Thermomechanical Loading", *Journal of Electronic Materials*, Vol. 41 (11), pp. 3179-3195, Springer, 2012

- II Laurila, T., Karppinen, J., Li, J., Vuorinen, V. and Paulasto-Kröckel, M.; "Effect of isothermal annealing and electromigration pretreatments on the reliability of solder interconnections under vibration loading", Journal of Materials Science: Materials in Electronics, in print, Springer 2012.

- III Karppinen, J., Li, J. and Paulasto-Kröckel, M.; "The effects of concurrent power and vibration loads on the reliability of board-level interconnections in power electronic assemblies", Transactions on Device and Materials Reliability, in print, IEEE, 2012.

- IV Karppinen, J., Laurila, T., Mattila, T.T. and Paulasto-Kröckel, M.; "The Combined Effect of Shock Impacts and Operational Power Cycles on the Reliability of Handheld Device Component Board Interconnections", *Journal of Electronic Materials*, Vol. 41 (11), pp. 3232-3246, Springer, 2012

- V Karppinen, J., Li, J., Mattila, T.T. and Paulasto-Kröckel, M.; "Thermomechanical reliability characterization of a handheld product in accelerated tests and use environment", *Microelectronics Reliability*, Vol. 50 (12), pp.1994-2000, Elsevier 2010.

VI Karppinen, J., Li, J., Pakarinen, J., Mattila, T.T. and Paulasto-Kröckel, M.; "Shock impact reliability characterization of a handheld product in accelerated tests and use environment", *Microelectronics Reliability*, Vol. 52 (1), pp. 190-198, Elsevier, 2012.

# **Author's contribution**

# Publications I & II:

The author participated in the planning of the research, the failure analyses, interpretation of the results and preparation of the manuscripts. The author also conducted all of the experimental work with help from several research assistants. The main part of the manuscripts, and in particular the material scientific discussion, were written by Dr. Tomi Laurila.

# **Publications III-VI:**

The research program was planned and the theoretical aspects were discussed by the author with the co-authors. The experimental work was planned by the author and conducted by the author with help from several research assistants. The author also carried out the statistical analyses, failure analyses and theoretical explanations of the results. The author wrote the manuscripts, which were then discussed in detail with the co-authors. The finite element modeling work in all publications was conducted by co-author Dr. Jue Li.

# **List of Abbreviations and Symbols**

AC alternating current

AF acceleration factor

ATC accelerated thermal cycling

BT bismaleimide triazine

CFD computational fluid dynamics

CTE coefficient of thermal expansion

DC direct current

EU european union

FE finite element

FEA finite element analysis

FEM finite element method

FR-4 fiberglass-reinforced epoxy resin, flame retardant

HALT highly accelerated life test

HCF high cycle fatigue

HTS high temperature storage

IC integrated circuit

IDSA incremental damage superposition

I/O input / output

IEC International Electrotechnical Commission

IMC intermetallic compound

JEDEC Joint Electron Device Engineering Council

LCF low cycle fatigue

LDSA linear damage superposition

min minute or minutes

MTBF mean time between failures

OPC operational power cycling

PBGA plastic ball grid array

PoF physics of failure

PWB printed wiring board

RT room temperature  $(22^{\circ}C / 295.15 \text{ K})$

SnAgCu tin silver copper solder alloy

TDM topography and deformation measurement

UBM underbump metallurgy

Wt-% weight percentage

a crack path length

$\begin{array}{ll} b & \text{fatigue strength exponent} \\ C & \text{life prediction model constant} \\ c & \text{life prediction model constant} \\ c_o & \text{life prediction model constant} \\ c_i & \text{life prediction model constant} \\ c_2 & \text{life prediction model constant} \\ c_3 & \text{life prediction model constant} \\ \end{array}$

D damage

$c_4$

E Young's modulus  $E_a$  activation energy  $\varepsilon_c$  creep strain

$\xi$  fatigue ductility coefficient

$egin{array}{ll} egin{array}{ll} egin{array}{ll} egin{array}{ll} egin{array}{ll} eta_{p} & & & & & \\ egin{array}{ll} eta_{p} & & & & \\ eta_{t} & & & & & \\ \end{array} & & & & & \\ \end{array} & \text{plastic strain} & & & \\ egin{array}{ll} eta_{t} & & & & \\ \hline \end{array} & & & & \\ \end{array}$

G gravitational acceleration constant of earth (9.81 m/s²) k Boltzmann constant (1.3806503 × 10<sup>-23</sup> m² kg/ (s² K))

life prediction model constant

K correlation constant

m life prediction model constant

N<sub>f</sub> cycles to failure

N<sub>o</sub> cycles to crack initiation

R process rate

$oldsymbol{s}_{\!f}'$  fatigue strength coefficient T absolute temperature

t time

W viscoplastic strain energy per cycle

# 1 Introduction

Reliability is an important factor to success in the highly competitive global electronics market. Customer dissatisfaction can have disastrous financial consequences to the manufacturer: While it takes companies a long time to build up a reputation for reliability, a single problematic key product can ruin this reputation almost overnight. Besides financial issues, failure due to insufficient reliability can lead to life threatening situations in critical fields such as medical devices and avionic electronics. It is clear that in these applications reliability should be of highest priority to avoid the catastrophic consequences of failure.

In addition to challenges in maintaining good reliability, the electronic product designers are constantly striving to meet the customer demands for new features and improved performance in a smaller size. Higher operating speeds require shorter interconnection distances to minimize propagation delays and new features require higher integration in component packaging. As a consequence, the assembly sizes, inputs/output (I/O) pitches and line widths in integrated circuits (ICs) as well as printed wiring boards (PWBs) are constantly decreasing. In order to provide assurance that new designs and products fulfill their reliability target, a large number of different reliability tests are employed. However, due to today's tight time-to-market requirements and shortening product cycles, the amount of required tests should be minimized.

The reliability testing of electronics has been traditionally carried out with accelerated reliability tests, where the tested units encounter loads more frequently than in service or are subjected to higher levels of accelerating variables like temperature or voltage. These tests can currently be grouped under two categories: traditional reliability tests, in which only one loading type is used, and combined tests, in which two or more different loading types are combined. Today, the vast majority of accelerated tests are still conducted as single load tests, because the interaction effects of various combined loads are not understood well enough. [Lau12, Upa01] Multiple load tests, however, offer many potential advantages when employed

properly. As modern products are required to withstand numerous loads without failure for many years, it is increasingly difficult to obtain sufficient amount of reliability data within a reasonable amount of time. Multiparameter tests have the potential to provide the means for overcoming this difficulty. In addition to expediting the whole product testing process by replacing multiple tests, it is shown that a single multiparameter test can also create a substantially more accurate representation of the loading conditions in actual use-environment [Upao1].

The focus of this dissertation is on the development of a realistic and efficient multiparameter reliability approach for different electronic product applications. This approach is demonstrated with studies of different loading condition combinations on the damage evolution in solder interconnections in Publications I, II, III and IV. The studied loading conditions include various combinations of mechanical, thermal, thermomechanical and electrical loads. In addition to simplified boardlevel tests, the true loading conditions encountered in one challenging product application, the consumer handheld device, are studied in detail with product-level test characterizations in Publications IV, V and VI. These characterizations are used to assess the limits of test acceleration under board level testing. Finally, suggestions on improvements to contemporary reliability assessment methods are given based on the results obtained from the dissertation publications. Although the results of the conducted research are primarily centered on interconnection reliability, the general methodology can be applied on any electronic structure.

The dissertation is organized as follows. A brief introduction to reliability challenges in electronic products is given in Section 2. An efficient reliability design process and evaluation methods are presented in Section 3. Lifetime estimation methods for electronic assemblies are addressed in Section 4 and special considerations as well as the key material properties for reliability assessment of lead-free solder interconnections are discussed in Section 5. Finally, Section 6 gives the summary of the work including the main results and conclusions of the included publications.

# 2 Background on reliability challenges

The typical reliability trend of an electronic product population through its intended lifetime is generally divided to three consecutive time periods:

- 1. Infant mortality period is characterized by an initial high failure rate, which is generally caused by poor quality control in manufacturing. These initial failures are especially harmful to manufacturer reputation, which may lead to loss of sales in addition to costs associated with product warranty work.

- 2. Once the part of population containing early design and manufacturing has failed, the remaining population typically enters a time period of relatively constant and low failure rate. This period is described as the useful life of the product, which should meet the expectations of the market for service life of such product type. The failures during useful life are random cases of environmental or operational stresses exceeding the product strength.

- 3. After the useful life period the product enters the wear-out period. The wear-out period is characterized by an increasing failure rate due to the fatigue or depletion of the structures and used materials. The failure of the product should be "graceful". This means that the failure should preferably be predictable (e.g. early warning of wear-out from internal self-diagnostics) and that the failure should not cause injury or damage to other attached or adjacent devices.

The failures in electronic assemblies are caused by electrical, thermal, mechanical and chemical stresses occurring during service. These stresses may originate from the external environment (for example, electrostatic discharges, ambient temperature changes and accidental product drop impacts) or be produced internally by the device itself (for example high current densities, electric power dissipation and mismatches in material thermal expansion). A brief overview of typical thermal, mechanical and electrical loads and their reliability effects are given in this section. Chemical stresses, however, are not within the scope of this dissertation.

Failures in electronic products can be classified to hard or soft failures, depending on whether the product regains its functionality after the failure-inducing stresses are removed. Soft failures are typically caused by operating the product outside the manufacturer specified environmental conditions (temperature, humidity, etc.) range. In these cases the product has usually not sustained permanent damage and becomes operational once the environmental conditions have returned to within the manufacturer's specifications. Hard failures, on the other hand, are caused by irreversible physical damage to the product. In these cases the product remains faulty until the damaged parts have been replaced or reworked. The emphasis of the research conducted in this dissertation is on hard product failures.

Hard product failures can be further categorized into two types based on severity of the imposed loading conditions:

- Overstress failure: In the simplest case the failure occurs when the stress level exceeds the strength of the product. Examples of threshold strengths are the tensile strength of a material or the temperature level at which an electronic component begins to malfunction. Overstress failures are generally caused by either too harsh product use environmental (user error) or latent manufacturing and design defects in the product.

- 2. Fatigue failure: Some failures occur under cumulative effects of repeated low-level stressing. Each stress cycle causes irreversible changes in the product, which ultimately cumulate to result in product failure. An example of phenomenon leading to cumulative stress failure is the fatigue failure of interconnections under mechanical bending or vibration loading. Cumulative stresses

generally define the useful life of the product in the specified use environment.

The failure type induced under true field conditions, however, is usually a combination of cumulative and overstress failure. A high peak-stress may initiate an incipient failure that later results in a hard failure due to lower cumulative stressing. Also, low cumulative stresses may substantially reduce the strength of the product to withstand subsequent overstress conditions.

# 2.1 Thermal loading

The vast majority of electronic components can easily meet their reliability targets when operating at or near room temperature. In practice, many integrated circuits operate at substantially higher temperatures and undergo various thermal excursions depending on the operating profile of their use conditions. Temperature can be considered the most fundamental factor affecting the reliability of all electronics. Typical operating temperature ranges for several electronic device categories reported in [IPC92, Viso4, Hat99, Edd98] are given in Table 1.

Table 1 – Typical operational temperature ranges for different electronic product types (excludes specialized sensors, which may encounter substantially

higher temperatures).

| Application                          | Electronics internal operating temperature range | Ambient<br>environment<br>temperature range |

|--------------------------------------|--------------------------------------------------|---------------------------------------------|

| Military                             | -55 °C to 125 °C [Vis04]                         | -55 to 95 °C [Viso4]                        |

| Automotive                           | -40 °C to 150 °C [Hat99, Edd98]                  | -40 °C to 125 °C<br>[Hat99, Edd98]          |

| Industrial &<br>telecom<br>equipment | -40 °C to 125 °C [IPC92]                         | -40 °C to 85 °C<br>[IPC92]                  |

| Consumer                             | 0 to 100 °C [IPC92]                              | o to 60 °C [IPC92]                          |

Temperature influences device reliability both directly and indirectly via other failure mechanisms. Temperature directly affects both the mechanical properties (such as elastic modulus, ultimate tensile strength, yield strength, and ductility) as well as electrical properties (such as resistivity and capacitance) of materials. The changes in electrical properties typically

cause soft product failures as the operational parameters of individual components or circuits drift beyond specifications. The changes in mechanical properties, on the other hand, may lead to hard product failures. For example, high temperature can lead to softening, weakening or melting of materials and device malfunctioning, while low temperatures can result in embrittlement of plastics, condensation and freezing of condensation or coolants. Furthermore, solid-state diffusion and chemical reactions are accelerated by increasing temperature. These physical processes may permanently change the mechanical properties of the materials used in electronic assemblies. This is particularly true with low melting temperature materials, which may undergo significant time-dependent microstructural changes when exposed to high temperatures [Dom11, Jeoo4, Peno7]. The reliability effects of microstructural changes in solder interconnections due to thermal loads are explored in Publications I-V.

In addition to the direct effects of temperature discussed above, major reliability concerns arise from indirect mechanical stresses caused by changing temperature. Due to geometric constraints and mismatches in the coefficient of thermal expansion (CTE) between materials, so-called thermomechanical stresses are concentrated in various parts of electronic assemblies. With repeated thermal excursions these parts experience cyclic mechanical loading, which may ultimately lead to fatigue failure. Interconnection areas in particular are vulnerable to thermomechanical damage. [Lauo7, Hamoo, Mato4, Zhao5]. The lifetime and failure mode of as-manufactured and preconditioned solder interconnections under thermomechanical loading are addressed in publications I, III, IV and V.

Some reliability effects of high temperatures on electronic assemblies encountered within the research of this dissertation [Publications I- VI] are given in Table 2.

Table 2 - Some effects of high temperature ( < 125 °C) on parts of electronic

assemblies [Publications I-VI].

| Structure / material      | Effect on material(s)                                                     | Effect on reliability                                                                                              |

|---------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| PWB / fiberglass          | Notable thermal expansion                                                 | Internal thermomechanical stress between materials                                                                 |

| reinforced epoxy resin    | Change of tensile<br>properties                                           | Loss of mechanical support                                                                                         |

| Interconnections / solder | Increased material diffusion and microstructural change Change of tensile | Increased electro- and thermomigration, reduction of strength and load-carrying ability  Reduction of strength and |

|                           | properties                                                                | load-carrying ability                                                                                              |

| Component packages        | Notable thermal expansion                                                 | Internal thermomechanical<br>stress, warpage and<br>delamination                                                   |

|                           | Change of tensile<br>properties                                           | Loss of mechanical support                                                                                         |

| Functional parts of       | Changes in electrical properties                                          | Unreliable operation                                                                                               |

| components                | Increased material<br>diffusion                                           | Increased electro- and<br>thermomigration                                                                          |

# 2.2 Mechanical loading

Mechanical loads are becoming an ever more important part of electronics reliability engineering due to the increasing amount of integrated circuitry employed in mobile applications. Mechanical loadings typically cause damage to board-level interconnections, component leads and connectors within component assemblies due to the straining of printed wiring boards, inertial forces and knocking of adjacent parts [Wono5, Seao6, Varo7, Maro7]. High strains may cause instantaneous overstress failures as the mechanical strength of a component or subassembly is locally exceeded, whereas repeated low amplitude bending can lead to fatigue failure. Different mechanical loads are typically divided into the three basic categories: (1) static or quasi-static mechanical bending, (2) vibration and (3) shock impact loads. These load types, the typical applications they affect, their main failure drivers and typical failure modes are given in Table 3.

Table 3 – Common mechanical loads encountered by electronic products.

| Load<br>type                             | Applications affected                                                            | Typical failure<br>drivers in<br>component assembly                                                                                                           | Failure modes in component assemblies                                                    |

|------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Shock<br>impact                          | - Portable devices<br>- Automotive<br>- Some devices<br>during transit           | <ul> <li>Inertial loads caused<br/>by high acceleration</li> <li>Overstress caused by<br/>assembly bending</li> <li>Knocking of adjacent<br/>parts</li> </ul> | - Interconnection /<br>component lead<br>overstress failure<br>- Connector<br>detachment |

| Vibration                                | - Automotive - Aerospace - Marine - Work machinery - Most devices during transit | - Fatigue damage caused<br>by cyclic bending of<br>assembly - Knocking of adjacent<br>parts                                                                   | - Interconnection /<br>component lead<br>fatigue failure<br>- Connector<br>detachment    |

| Static or<br>quasi-<br>static<br>bending | - Portable devices                                                               | - Overstress caused by assembly bending                                                                                                                       | - Interconnection /<br>component lead<br>overstress failure<br>- Connector<br>detachment |

Static or quasi-static mechanical stresses can be imposed on the printed wiring board when the whole product is bent, or for example in a situation when connector or keypad pressings directly load the device PWB. The most common destructive mechanical loads for electronic products, however, are dynamic vibration and shock impact loads.

Vibration loading can, for example, be readily found in mission-critical applications within the automotive, aerospace, marine, and heavy work machine industries. Furthermore, many products intended for stationary use endure vibrations during the logistic chain from the manufacturing line to the end user. Portable electronics, on the other hand, are susceptible to be dropped during service, which creates substantial high-strain shock loads on the product assembly [Publication VI]. Both shock and vibration loads can also excite the natural vibration modes of product PWBs [Publication VI, Wono5, Seao6, Varo7, Maro7,], which lead to overstress and/or fatigue failure (depending on the duration and amplitude of PWB vibration) of electrical interconnects and detaching of connectors.

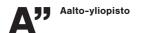

The reliability effects of mechanical shock loads on the interconnections of a handheld device component boards are studied in publications IV and VI. The left part of the Figure 1 demonstrates the acceleration and strain

histories of a mobile phone PWB after a product-level drop impact from 1.2m height (see publication II for details). The effects of mechanical vibration loads on board-level interconnections are presented in publications II and III. The right part of Figure 1 shows an example of a printed wiring board excited to its first natural vibration mode by an electrodynamic shaker.

Figure 1 – Left: Acceleration and strain histories measured from a handheld device PWB under product-level drop (see Publication II for details). Right: Bending of the device PWB under vibration loading.

# 2.3 Electrical loading

Miniaturization of electronics has led to rapid increase of current densities in conductors and interconnections, exposing these structures to electromigration. Electromigration is a process in which the conductor material is transported due to two driving forces: (1) the momentum transfer between conducting electrons and diffusing metal ions and (2) the direct force exerted to the metal ions by the electric field. The typical current density at which electromigration effects become notable is about 10<sup>6</sup> A/cm² in aluminium and copper conductors. [Ho89,Tuo3] As electromigration depends on material diffusion, the temperature of the stressed conductor has a large effect on the rate of the process. Typical current densities encountered in different parts of electronic assemblies are given in Table 4 along with their known reliability effects.

Table 4 - Typical current densities required for onset of electromigration.

| Structure            | Material             | Current density                                                                 | Effect of electro-<br>migration                                                                                           | Effect on reliability                                |

|----------------------|----------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| IC                   | Copper               | > 10 <sup>6</sup> A/cm <sup>2</sup>                                             |                                                                                                                           |                                                      |

| metallization        | Aluminium<br>/ Al-Cu | [Ho89, Tu03]                                                                    | Hillock and void formation                                                                                                | Formation of<br>short or open<br>circuits            |

|                      |                      | > 10 <sup>4</sup> A/cm <sup>2</sup><br>[Tuo3]                                   |                                                                                                                           | circuits                                             |

| Intercon-<br>nection | Tin-based<br>solder  | > 10 <sup>3</sup> A/cm <sup>2</sup><br>[Tuo3, Lau11,<br>Publications I &<br>II] | <ul> <li>Biasing of<br/>interfacial<br/>intermetallic<br/>growth</li> <li>Changes in solder<br/>microstructure</li> </ul> | Embrittlement<br>of<br>interconnection<br>interfaces |

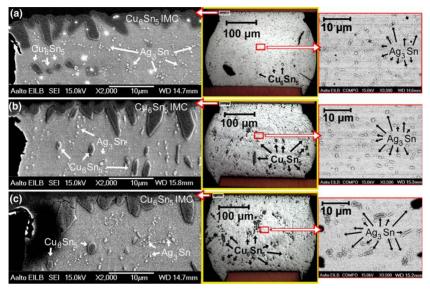

Electromigration has been successfully reduced in the aluminium conductors of integrated circuits by employing bamboo structures and Cualloying [Ho89, Tuo3]. However, new concerns are rising on the effects of electromigration within low melting temperature solder alloys. As is shown in publications I and II, electromigration becomes detectable in solder interconnections already at a current density of only about 10<sup>3</sup> A/cm<sup>2</sup>. Above this value electromigration causes nonuniform formation of intermetallic compounds between anode and cathode side of the interconnection. When the current density is increased to about 10<sup>4</sup> A/cm<sup>2</sup> the effect of the electron flux becomes powerful enough to cause substantial material transport in interconnections [Tuo3, Che10]. Unlike thin film conductors inside integrated circuits, the microstructure of solder interconnections cannot be controlled by manufacturing processes to combat the electromigration problem.

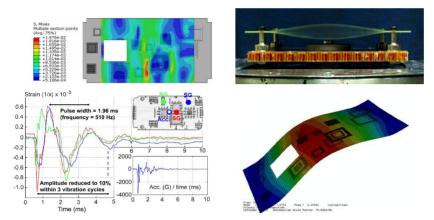

Most problematic areas for electromigration are abrupt changes in conductor geometry and interfaces of dissimilar conductor materials. Sharp changes in conductor geometry and resistivity lead to current crowding, in which the local current density may become orders of magnitude higher than the estimated average current density [Tuo3,Che10]. Due to current crowding problems electromigration is rapidly becoming a reliability concern in contemporary electronic assemblies. Figure 2 shows the effects of electromigration on a solder interconnection and illustrates the problem of current crowding.

Figure 2 – Left: SEM image of a solder interconnection exposed to 3x10<sup>4</sup> A/cm<sup>2</sup> current density for 26 days. Right: Illustration of current crowding in a flip-chip solder interconnection due to geometry and interfaces of dissimilar materials.

# 2.4 Single load - multiple stress conditions

Electronic products are seldom exposed only to a single type of stress, even if only a single loading condition is imposed on the product. A ubiquitous example of a single load causing multiple stresses is electrical power loading. When electrical current is driven through the circuitry, not only are conductors and components exposed to electromigration stress, but also to increased temperature due to resistive losses. This not only increases the local temperature of the assembly, but the resulting thermal gradients cause thermomechanical stresses between dissimilar materials. Thus, applying electrical power load to an electronic assembly generates simultaneously electrical, thermal and mechanical stresses.

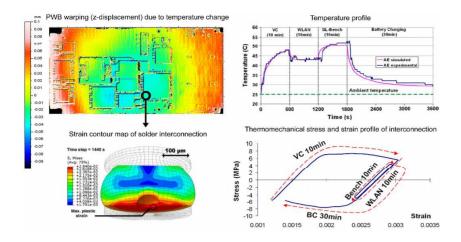

Since all electronic devices dissipate heat due to electrical losses to some extent, the above-mentioned combination of electrical, thermal and mechanical stresses is unavoidable. However, the severity of these stresses depends on the design of the product. In a well-designed product these stresses are kept at a low enough level to not cause reliability concerns during the designed service life. Therefore, it is of paramount importance to consider and aim to mitigate these loads as early in the product design as possible. The formation and effect of thermomechanical stresses on a commercial handheld electronic product and power electronic test assemblies are investigated in Publications I, III, IV and V of the dissertation. Figure 3 below shows the thermomechanical stress and strain induced in a solder interconnection inside a mobile phone under power loading (see [Karo8] and Publication V for details of the experiment).

Figure 3 - Thermomechanical stress in an interconnection due to operational power dissipation (see [Karo8] and publication I for details).

# 3 The assembly-level reliability design process

Due to the wide range of modern electronic products, it is impossible to define a universal test method that would prove the reliability of each product in their own use environment. Therefore, the reliability design process should begin with investigations on the reliability requirements of the specific product application. The product application will typically define the service environment, lifetime, and design requirements [Mil338, Chao1].

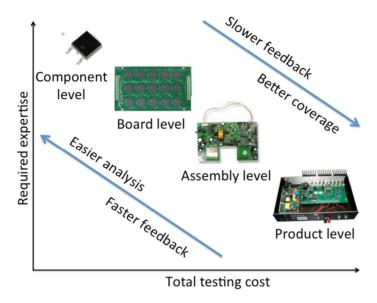

While it is compulsory to test an electronic product in its final form to verify the fulfillment of reliability and safety requirements, it is also highly desirable to conduct reliability evaluations throughout the design cycle. Early evaluations on prototype designs can substantially expedite the detection of potential reliability problems and allow cost-effective solutions to improve the design [Mil338, Chao1]. In general, it is preferable to start reliability evaluations with the smallest testable units of a product and then progressively proceed to testing of larger systems. The early reliability evaluations can be conducted with statistical block diagram analyses, simplified prototype experiments or by employing computational methods, such as the finite element method (FEM).

The challenge in reliability assessment of smaller subassemblies is in the definition of realistic loading conditions: as the final product enclosure and fixtures may not be available, estimations on their effects to the tested unit's reliability will have to be made [Chao1, Mil338]. Conducting mechanical and thermal characterizations on similar product designs or dummy structures can refine these estimations. As an example, mechanical and thermal characterizations of a mobile phone have been conducted in [Karo8] and [Karo]. The results of these characterizations are

subsequently utilized in Publications V and VI to estimate the reliability of the device. Figure 4 illustrates the advantages and challenges in performing reliability assessments between smaller and more complete test vehicles [Chao1].

Figure 4 –Advantages and challenges of focused and more comprehensive test vehicles (adapted from [Chao1]).

Once the suitable loading conditions and fixturing have been determined, the response of the tested assembly to the defined loading conditions are investigated. The typical responses to be investigated are (1) detection of potential stress- and strain concentrations on the assembly, (2) detection of temperature levels and possible temperature gradients under operating conditions, (3) detection of high current densities and voltage levels and (4) assessment of materials and structures vulnerable to humidity or corrosion. These investigations help to pinpoint the most critical locations in the assembly, which may limit the reliability of the final product.

The preliminary evaluation of the assembly response to loading conditions can be followed by a more in-depth study focusing on the found critical design points. In this stage a more detailed FE-analysis (FEA) or experimental reliability test on a representative test structure is conducted to investigate whether the found critical loads form a reliability threat to the final product. For best results, this focused reliability evaluation should be

based on good understanding of the underlying physical failure mechanisms acting on the critical parts of the assembly [Lau12]. Examples of such studies on component-level test vehicles are presented in Publications I-IV of this dissertation. If the design fails the reliability evaluation, improvements need to be made to rectify the problem. Afterwards the reliability evaluation should be redone to verify that the reliability problem has been solved [Chao1, Mil338].

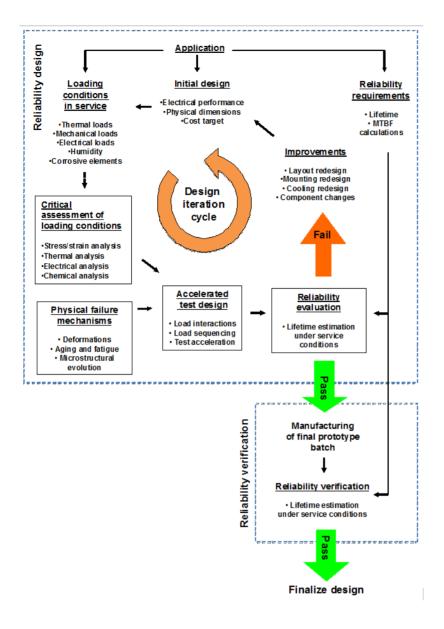

Once the initially weak design features in the individual subassemblies have been corrected, the first production-grade prototype batch of the complete product can be manufactured. This prototype batch is used to verify the fulfillment of the set reliability goals by employing product-level accelerated reliability tests. A flow chart of the presented reliability design process is shown in Figure 5. The process steps to which the research done in this dissertation offers new insight are marked with black rectangular borders. The critical assessment of loading conditions and accelerated test design are discussed in this section. Analytical lifetime estimations and physical failure mechanisms are discussed in the following sections.

Figure 5 – The reliability design process suggested for best efficiency.

# 3.1 Critical assembly-level assessment of loading conditions

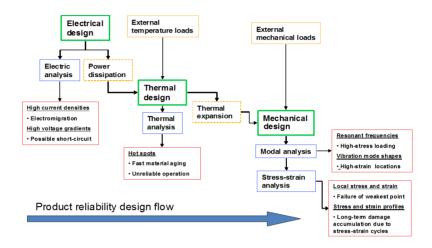

As was discussed previously, reliability engineering should begin early in the product development cycle to achieve the best time and cost efficiency. An efficient workflow for conducting the critical assessment of loading conditions during product design is shown schematically in Figure 6 and described below in more detail. The workflow is based on findings from the studies within this work and aims to provide a comprehensive reliability evaluation of an electronic product in the design stage. The use of computational methods early in the product design can help avoid possible design flaws without the added costs of physical prototyping. However, the simulation results should always be verified with some control experiments.

Figure 6 - A workflow for efficient assembly-level reliability design process.

# Electrical analysis

The first opportunity to start reliability assessment is already in the electrical design stage of the component assembly. In addition to functional design, electrical analysis should be used in conjunction with component board layout drafts to determine possible reliability problems with local high power- and current densities. Also large voltage differences between adjacent parts should be avoided in order to reduce the possibility of short circuits due to breakdown of insulating layers.

# Thermal analysis

After the initial electrical design and layout of a product or subassembly has been completed, a preliminary thermal analysis with computational fluid dynamic (CFD) or FE modelling methods can be conducted using the calculated power dissipation values and ambient temperature as input parameters. CFD and FE programs employ iterative heat transfer calculations on simplified 3D models derived from the component layout files. The thermal analysis is conducted to investigate the temperature gradients and possible hot spots caused by the combination of external thermal loads and internal power dissipation loads. Thermal analysis can be conducted experimentally by employing thermocouples, thermistors or non-contact infra-red imaging on the test assembly under thermal and power loading. Experimental thermal analysis has been employed in Publications I-V of this dissertation to characterize thermal loads induced by power cycling and thermal cycling tests on board-level solder interconnections.

# Thermomechanical analysis

Once both electrical and thermal analyses show positive results on the designed assembly, the thermomechanical stresses are assessed either experimentally (if a mechanical prototype is available) or with FE simulations. If computational methods are used, the thermal profile from thermal analysis is loaded to the employed FE-tool in order to assess the thermomechanical stresses. FE-modelling results are highly sensitive to the accuracy of the employed material models and the applied boundary conditions. Therefore, the results should be verified experimentally

whenever possible. Thermomechanical stress and strain analysis have been successfully employed in Publication V of this dissertation to estimate the lifetime of a BGA component inside a mobile phone. Thermomechanical strains can also be measured experimentally by with strain gages or by employing precise non-contact imaging techniques, such as the Topography and Deformation Measurement (TDM) system [Fay04] used in Publication V and [Karo8] or Moiré interferometry [Zhaoo].

# Modal analysis

The analysis of mechanical vibration and shock impact loads is usually started by conducting a modal analysis of the sample assembly. In modal analysis the dynamic response of the assembly is measured or calculated under vibration or impulse excitation. If mechanical properties (mass and modulus) of the used materials are known, FE analysis can be used to efficiently calculate the resonant mode shapes and frequencies of the structure. Experimental modal analysis can be conducted with transducers (typically accelerometers, strain gages and load cells), or non-contact via laser vibrometry. Typical excitation methods include mechanical vibration, impulse or acoustic signals exerted on the studied sample. The analysis of the signals usually relies on Fourier analysis. The resulting transfer function will show one or more resonances, whose characteristic mass, frequency and damping can be estimated from the measurements. Both experimental and FE modal analyses have been employed in Publications IV and VI of this dissertation to determine critical resonant frequencies of a mobile phone component board.

# Mechanical analysis

After the critical natural frequencies of the assembly are found using modal analysis, stress and strain analyses under these worst-case loading conditions can provide insight into possible mechanical reliability problems in the PWB, component packages and interconnections. The most efficient method for stress and strain analysis is to employ computational FE-analysis verified by several experimental strain measurements. The strains can be measured experimentally by employing strain gage sensors on mechanical prototypes. Detailed information on the stress-strain conditions of the studied assembly is often a necessary prerequisite for the use of

subsequent damage models and lifetime estimations [Leeoo]. Stress-strain analyses of critical electronic structures, in this case solder interconnections, have been conducted by employing FE modelling in Publications II and III.

# 3.2 Accelerated test design

The objective of accelerated reliability tests is to generate similar failure modes that would occur under normal product operating conditions in a considerably shorter timescale. This is accomplished by subjecting the test units to higher than usual levels of accelerating variables like temperature, voltage or mechanical stress. Caution should be exercised when selecting an accelerated test condition, since the accelerated loading may exceed the capabilities of the device and materials, inducing failures (overstress) failures that would not occur under normal use conditions.

Numerous testing methods have been standardized for the different needs of a wide spectrum of products and components. The test subjects can be exposed to loadings that are chemical, mechanical, thermal or electrical in nature or to a combination of the aforementioned loads, all depending on the presumed operation conditions of the subjects. Expected service life figures and expected loading conditions for several different electronic product types are given in Table 5.

Table 5 - Service life and loading condition expectations of electronic product

types [IPC92].

| Product type        | Expected     | Expected loads                               |

|---------------------|--------------|----------------------------------------------|

|                     | service life |                                              |

| Automotive          | >10 years    |                                              |

| Avionics            | >20 years    | - Mechanical shock, vibration - Power cycles |

| Military            | >10 years    | - Thermal cycles                             |

| Space               | 5-20 years   |                                              |

| Telecommunications  | 7-20 years   | - Power cycles                               |

|                     |              | - Thermal cycles                             |

| Computers           | >5 years     | - Power cycles                               |

| Consumer / portable | 1-3 years    | - Power cycles                               |

| consumer / portable | 1 5 years    | - Mechanical shock, vibration and            |

|                     |              | - bending                                    |

In order to reduce uncertainty and simplify the assessment of imposed loading conditions, most accelerated reliability studies are conducted on component board level. Furthermore, in many cases component-level testing is undertaken to begin characterizing product's reliability when full system level test units are unavailable or prohibitively expensive. In the following subsections the most common accelerated board level tests for thermal, mechanical and electrical loads as well as their combinations are introduced and discussed.

# 3.2.1 Thermal- and thermomechanical tests

High temperature storage (HTS) tests are typically used to determine the effect of time and temperature, under storage conditions, on thermally activated failure mechanisms of electronic devices. During the test the samples are placed in elevated temperature test chambers without applied electrical stress.

The reliability effects of thermomechanical stresses on electronic assemblies are typically evaluated using Accelerated Thermal Cycling (ATC) tests. In ATC tests the samples are placed inside thermal cycling chambers, which allow the ambient temperature to be changed according to a preset thermal cycle profile. The thermal profile is defined by the maximum and minimum temperatures, temperature ramp rates and dwell times. The

accelerated thermal cycling test methods correspond well with true loading (i.e. the worst case scenario) experienced by electronics moved from one ambient temperature to another. However, due to negligible thermal gradients present in ATC testing, it cannot properly capture the thermomechanical stresses induced by internal heat dissipation of electronic devices. For this reason the thermomechanical stresses caused by operational power dissipation are best assessed with power cycling tests [Publication V, Lauo7]. Accelerated thermal shock test is otherwise similar to the ATC test, except the temperature ramp rates are significantly faster. The faster ramp rates enable higher time compression during the test. Table 6 shows the most common test standards, loading conditions, expected failure types and typical test durations of the presented three tests.

Table 6 - Test standards, loading conditions and expected failure types of common thermal tests.

| Test type | Standards      | Loading                                 | Expected          | Typical    |

|-----------|----------------|-----------------------------------------|-------------------|------------|

| • •       |                | conditions                              | failure           | test       |

|           |                |                                         |                   | duration   |

| High      | JESD22-A103C   | Damp                                    | Component         | From       |

| tempera-  | IEC 60068-2-2  | isothermal heat                         | package           | several    |

| ture      |                | in an oven or                           | damage due to     | hours to   |

| storage   |                | thermal                                 | aging,            | several    |

|           |                | chamber. T <sub>max</sub>               | embrittlement     | months per |

|           |                | = 85°C -                                | of plastic parts. | batch.     |

|           |                | 300°C.                                  |                   |            |

|           |                |                                         |                   | (10 hours  |

| Thermal   | JESD22-A104C   | Isothermal                              | Fatigue failure   | - 2000     |

| cycling   | IEC 60068-2-14 | temperature                             | of board-level    | hours)     |

|           |                | cycling T <sub>min</sub> = -            | interconnection   |            |

|           |                | 60°C - 0°C,                             | s, IC wire        |            |

|           |                | $T_{\text{max}} = 60^{\circ}\text{C}$ - | bonds and         |            |

|           |                | 200°C, Ramp                             | internal failure  |            |

|           |                | rate < 15°C /                           | of component      |            |

|           |                | min, 0.5 to 4                           | packages.         |            |

|           |                | cycles per hour.                        |                   |            |

|           |                |                                         |                   |            |

| Thermal   | JESD22-A106B   | Same as above,                          |                   |            |

| shock     | JESD22-AIOOD   | _                                       |                   |            |

| SHOCK     |                | except ramp                             |                   |            |

|           |                | rate > 15°C /                           |                   |            |

|           |                | min.                                    |                   |            |

|           |                |                                         |                   |            |

#### 3.2.2 Mechanical tests

Shock impact tests are typically conducted by attaching the component boards into a test apparatus, where the drop test table moves vertically on guide rods to hit a strike surface. After the impact the test board vibrates according to its natural bending modes. The most damaging bending modes are typically the first and the second mode [Maro7, Publication IV & VI], which generate the most of the total displacement and strain. In general, the higher the frequency of the mode, the smaller the bending amplitude becomes.

Vibration tests have been conventionally conducted with either pneumatic or electromagnetic shaker systems. In both cases the test specimen is attached to an excitation table, which moves according to a predetermined signal. Depending on the system, the shaker may be able to excite the sample over all three or just one axis. Standardized vibration tests rely on frequency sweeps and random vibration to excite all the natural modes of the sample. However, if the natural vibration modes of the tested structure are known, the test time can be greatly reduced by concentrating the vibration load on these frequencies.

Bending tests are typically conducted on tensile pull machines, which are fitted with jigs to enable controlled curvature 3- or 4-point bending of the sample. Bending tests are typically overstress tests, in which the destructive limit of the assembly is investigated.

Table 7 shows the most common testing standards, loading conditions, expected failure types and typical durations of the discussed three tests.

Table 7 - Test standards, loading conditions and expected failure types of

| common thermal tests. |            |                    |                      |               |

|-----------------------|------------|--------------------|----------------------|---------------|

| Test                  | Standards  | Loading            | Expected             | Typical       |

| type                  |            | conditions         | failure              | test          |

|                       |            |                    |                      | duration      |

| Shock                 | JESD22-    | Half-sine shock    | Board-level          | Several       |

| impact                | B104C      | impact, 0.2-30ms   | interconnection      | minutes to    |

|                       | JESD22-    | duration, 5 -      | overstress or        | hours per     |

|                       | B110A      | 10,000 G           | fatigue failure.     | single        |

|                       | JESD22-    | acceleration.      |                      | sample.       |

|                       | B111       |                    |                      |               |

|                       | IEC 60068- |                    |                      |               |

|                       | 2-77       |                    |                      |               |

|                       |            |                    |                      |               |

| Vibration             | JESD22-    | Frequency sweep    | Board-level          | Several hours |

|                       | B103B      | from 1-20Hz to     | interconnection      | to several    |

|                       | IEC 60068- | 500-5000Hz at      | fatigue or           | weeks per     |

|                       | 2-6        | 0.001 - 500 G      | overstress failure.  | single        |

|                       |            | acceleration or    | Component lead       | sample.       |

|                       |            | 0.0127 - 1.5mm     | failure.             |               |

|                       |            | displacement.      |                      |               |

|                       |            |                    |                      |               |

| Bending               | JESD22-    | 1-3 Hz frequency   | Board-level          | Several       |

| (3- or 4-             | B113       | 4-point bending of | interconnection      | minutes per   |

| point)                | o .        | PWB, 2-4 mm        | overstress failure.  | single        |

| Polit,                | 2-21       | displacement at    | 5. Sibiloss familios | sample.       |

|                       |            | _                  |                      | sample.       |

|                       |            | center.            |                      |               |

|                       |            |                    |                      |               |

#### **Electrical tests** 3.2.3

Electromigration testing is conducted by driving a predetermined amount of electrical current through the test sample. The tests are usually executed with much higher current densities than specified in service conditions to accelerate the test. Due to the high current densities involved, Joule heating must be taken into account when designing the test [Publications I and II]. The increased temperature will further accelerate failure due to faster diffusion and chemical reactions.

Power cycling tests are primarily conducted to investigate the thermomechanical loading induced by internal power dissipation of the tested assembly. Unlike accelerated thermal cycling, the thermal loading induced by power cycling is highly nonuniform and corresponds well with the internal thermal loading under true service conditions. Although power cycling induces thermal, mechanical and electric stresses, the tests are typically defined by temperature profiles similar to accelerated thermal cycling. The limitations for power cycling load amplitude and frequency are generally dependent on the tested circuitry, although additional test acceleration may be achieved by using external heating elements. Power cycling test may also be conducted on non-functional assemblies by using solely external heating elements. In this case possible design problems with Joule heating and electromigration of the circuitry are not captured. Table 8 shows the common testing standards, loading conditions, expected failure types and typical durations of electromigration and power cycling tests.

Table 8 - Test standards, loading conditions and expected failure types of common thermal tests.

| common thermal tests. |              |                              |                  |            |

|-----------------------|--------------|------------------------------|------------------|------------|

| Test type             | Standards    | Loading                      | Expected         | Typical    |

|                       |              | conditions                   | failure          | test       |

|                       |              |                              |                  | duration   |

| Electro-              | JESD61A.01   | Constant DC or               | Conductor        | Several    |

| migration             | JESD202      | AC current at                | failure or short | hours to   |

| (constant             |              | specified current            | due to voiding   | several    |

| bias)                 |              | density.                     | and hillocking.  | months     |

|                       |              |                              |                  | per test   |

| Power                 | JESD22-A122  | Thermal                      | Board-level      | batch (10- |

| cycling               | JESD22-A105C | response of                  | interconnection  | 2000       |

|                       |              | power cycle                  | fatigue failure  | hours).    |

|                       |              | (measured from               | due to thermo-   |            |

|                       |              | surface)                     | mechanical       |            |

|                       |              | T <sub>min</sub> =10 - 40°C, | loading,         |            |

|                       |              | $T_{max} = 100 -$            | assisted by      |            |

|                       |              | 125°C,                       | electro-         |            |

|                       |              | 2-6 cycles per               | migration.       |            |

|                       |              | hour.                        |                  |            |

|                       |              |                              |                  |            |

|                       |              |                              |                  |            |

### 3.3 Combined loading test design

Electronic products are seldom exposed only to a single type of stress or strain. For example portable products might be dropped during their operation (i.e. when their components are running hot) while automotive, avionic and military products can be constantly exposed to concurrent vibrations and thermal excursions. Multiple loading tests have, therefore, been developed to simulate the real operational loadings as realistically as possible and to address all relevant failure mechanisms as in the use environment. The combining of several loadings is also expected to increase the rate of damage accumulation and thus decreasing the associated testing time and costs.

The most popular multiple load test method employed is the Highly Accelerated Life Test (HALT) originally presented by Hobbs [Hoboo]. In HALT procedure electronic products or subassemblies are subjected to thermal shocks or increasing temperature and random multiaxial vibration. The objective of the HALT test is to cause failure by subjecting the sample to simultaneous, progressively increasing mechanical and thermal loads. Despite its name, the HALT method focuses on finding latent flaws and design errors in electronic assemblies through overstress failures. Thus, the method cannot be used for true lifetime or reliability assessments, as the stress conditions and failure mechanisms can differ substantially from those found in the service environment [Suho7, Mil338].

Despite the potential advantages associated with multiple loading tests, the methods are still seldom utilized for lifetime and long-term reliability evaluations. Although extensive research results have been documented for lifetime evaluations under to single load tests, limited research has been conducted on predicting failures caused by combined loads. Disagreement still surrounds the complex interactions between combined loadings and it is often unclear how to choose and set up test parameters in the most effective way or how to extrapolate the test results to actual use environments [Upao1, Mat11]. Different load frequencies (such as the low frequency loading in thermal cycling and the high frequencies in vibration testing) and amplitudes between the loading conditions confuse the matters even more. In this section some of these issues are discussed based on the current knowledge and findings of this dissertation.

In combined load testing the different load components may be combined consecutively, concurrently or in a mixture of consecutive and concurrent stresses. The choice of load sequencing has a profound impact on the achieved test results, and the decision should be made according to the estimated true service environment.

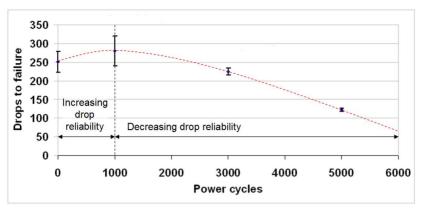

#### 3.3.1 Consecutive tests

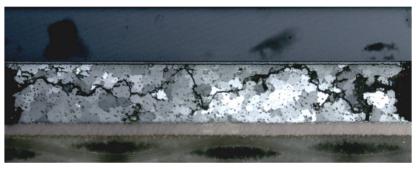

Consecutive tests are generally easier to employ than concurrent test, as standardized single load test conditions may be applied directly. In most studies employing consecutive electrical, thermal and mechanical loads, the thermal and electrical loadings are conducted first. The sequence is based on the idea that the thermal end electrical loads cause irreversible material degradation due to accelerated aging processes, which has a marked impact on its mechanical reliability. However, it is important to realize that the impact of the preconditioning may not be monotonous. As is shown in Publication IV, conducting 1000 power cycles prior to shock impact loading actually improved the reliability of solder interconnections. A larger amount of power cycles, on the other hand, resulted in sharply declining shock impact reliability. This reliability trend is shown in the Figure 7. Others have reported similar results on the application of thermal loads as preconditioning for mechanical shock loads [Peno7]. Furthermore, the typical sequence may not always offer an accurate representation of the true loading case. For example, some products may experience harsh mechanical loads during transportation prior to becoming operational. Sitaraman and Perkins have studied the sequencing of consecutive vibration and thermal cycling tests [Pero8]. They concluded that the combined loading was substantially more destructive when thermal cycling was applied prior to vibration loading.

Figure 7 – The reliability of component interconnections under consecutive power cycling and drop tests.

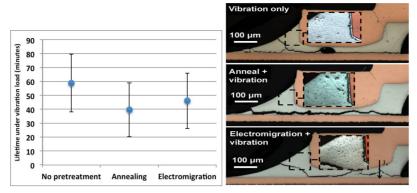

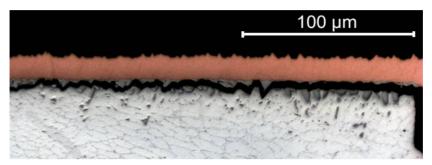

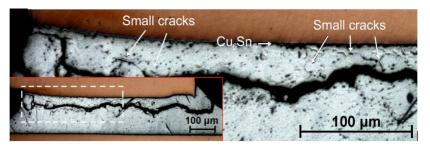

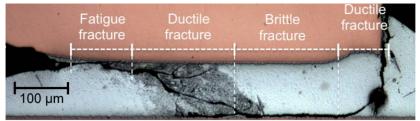

It is worth noting that consecutive tests generally take a longer time to conduct than concurrent load tests or individual load tests (which may be executed simultaneously). Therefore, the value of consecutive tests is in improving the understanding of relevant damage mechanisms and determining the contribution of each loading condition to the failure. Once the primary failure mechanisms under the consecutive loads have been determined, the subsequent tests can be optimized to give faster results by focusing only on the relevant mechanisms. An example of such case is the consecutive electromigration, isothermal annealing and vibration test conducted in Publication II. The lifetime results and cross-sectional images of failed specimen from the study are shown in Figure 8. Although the annealing and electromigration pretreatments did not markedly affect the reliability of board-level interconnections under the subsequent vibration test, the cross-sectional analyses of the failed specimen provided new insight to the interacting of the different failure mechanisms. Based on the attained information on failure mechanisms, future studies with similar specimen and loading conditions can be expedited.

Figure 8 – Left: The lifetime of pre-aged component interconnections under vibration tests. Pre-aging methods were isothermal annealing (750h at 125 °C) and electromigration stressing (750h at 1960 A/cm²). Right: cross-sectional images of the failed interconnections.

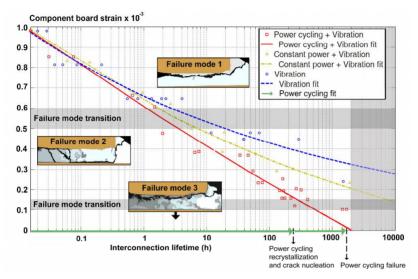

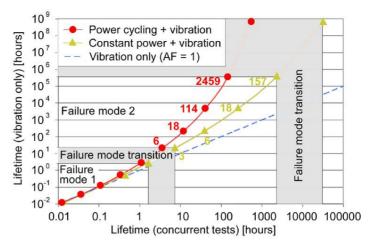

### 3.3.2 Concurrent tests