# Design and characterization of monolithic millimeterwave integrated circuits for receiver front-ends

## Mikko Kärkkäinen

# Aalto University publication series **DOCTORAL DISSERTATIONS** 118/2014

Design and characterization of monolithic millimeter-wave integrated circuits for receiver front-ends

Mikko Kärkkäinen

A doctoral dissertation completed for the degree of Doctor of Science (Technology) to be defended, with the permission of the Aalto University School of Electrical Engineering, at a public examination held at the lecture hall TU1, TUAS house, Otaniementie 17, Espoo, 18 September 2014 at 12.

Aalto University School of Electrical Engineering Department of Micro- and Nanosciences Electronic Circuit Design

#### Supervising professor

Prof. Kari Halonen

#### **Preliminary examiners**

Dr.-Ing. Michael Schlechtweg, Fraunhofer Institute for Applied Solid State Physics (IAF), Germany Prof. Markus Törmänen, Lund University, Sweden

## Opponent

HDR Didier Belot, STMicroelectronics, France

Aalto University publication series **DOCTORAL DISSERTATIONS** 118/2014

#### © Mikko Kärkkäinen

ISBN 978-952-60-5804-7 ISBN 978-952-60-5805-4 (pdf) ISSN-L 1799-4934 ISSN 1799-4934 (printed) ISSN 1799-4942 (pdf) http://urn.fi/URN:ISBN:978-952-60-5805-4

Unigrafia Oy Helsinki 2014

Finland

#### Author

Mikko Kärkkäinen

#### Name of the doctoral dissertation

Design and characterization of monolithic millimeter-wave integrated circuits for receiver front-ends

**Publisher** School of Electrical Engineering

**Unit** Department of Micro- and Nanosciences

Series Aalto University publication series DOCTORAL DISSERTATIONS 118/2014

Field of research Micro- and Nanoelectronic Circuit Design

Manuscript submitted 31 March 2014 Date of the defence 18 September 2014

Permission to publish granted (date) 4 June 2014

Language English

Monograph

□ Article dissertation (summary + original articles)

#### **Abstract**

This dissertation focuses on millimeter-wave front-ends and technologies and, especially, on integrated circuits operating at millimeter-wave frequencies. Several issues concerning millimeter-wave circuits are discussed, such as transmission lines and transistor models for small-signal simulations and noise characterization. The applications for these circuits vary from 60-GHz high-speed radio links to atmospheric precipitation measurement systems operating up to the water molecule resonance frequency of 183 GHz.

In chapter 3, the transistor model is calculated from measured data using saturation measurements only. The de-embedding is obtained using open and short coplanar waveguide structures. By calculating the extrinsic parasitics using linear regression, the small-signal parameters of the transistor model can be calculated and then simulated up to 110 GHz. The noise model is calculated based on the measured V-band ( $50-75~\rm GHz$ ) noise parameters and the corresponding noise matrices related to the open and short structures as well as the extrinsic parasitics. The values obtained for the noise sources and their correlation make wideband simulations of the transistor noise characteristics possible. The small-signal model, including the noise sources, can be used to simulate three different realized amplifiers and the results are compared to the measured data. These simulations show a very good agreement between the measured data and the simulated values.

Certain select design principles related to millimeter-wave, low-noise amplifiers and mixers are presented as well. This includes front-end system aspects as well as transistor selection issues. Chapter 5 discusses the issues related to millimeter-wave measurements in detail. The losses of different parts of the measurement setup, such as the back-to-back probe loss from two separate measurements and harmonic mixer, are shown. The noise measurements at these frequencies require special attention since the setup requires downconversion of the noise signal either within the device under test or externally with a separate measurement mixer. Empirical results are presented for both compound semiconductor and silicon-based circuits, namely GaAs HEMT and CMOS technologies. The measured results for the low-noise amplifiers are presented at operating frequencies of 94, 155, and 183 GHz. The 183 GHz amplifier achieved a gain of 16 dB and a 7.4-dB noise figure. In addition, two receiver front-ends are presented. One is realized with 150-nm GaAs PHEMT and the other with 65-nm CMOS technology. The GaAs receiver front-end consists of a three-stage, low-noise amplifier and an image-rejecting resistive mixer, while the silicon-based circuit has a balanced active mixer integrated with a five-stage amplifier.

Keywords low-noise amplifier, millimeter-wave receiver, transmission lines

| ISBN (printed) 978-952-60-5804 | -7 <b>ISBN (pdf)</b> 978-952- | 60-5805-4            |

|--------------------------------|-------------------------------|----------------------|

| ISSN-L 1799-4934               | ISSN (printed) 1799-4934      | ISSN (pdf) 1799-4942 |

| Location of publisher Helsinki | Location of printing Helsinki | Year 2014            |

| Pages 216                      | urn http://urn.fi/URN:ISBN:97 | 8-952-60-5805-4      |

Kieli Englanti

#### Tekijä

Mikko Kärkkäinen

#### Väitöskirjan nimi

Mikropiirien suunnittelu ja karakterisointi millimetriaaltoalueen radiovastaanottimiin

Julkaisija Sähkötekniikan korkeakoulu

Yksikkö Mikro- ja nanotekniikan laitos

Sarja Aalto University publication series DOCTORAL DISSERTATIONS 118/2014

Tutkimusala Mikro- ja nanoelektroniikkasuunnittelu

Käsikirjoituksen pvm 31.03.2014 Väitöspäivä 18.09.2014

Julkaisuluvan myöntämispäivä 04.06.2014

☑ Yhdistelmäväitöskirja (yhteenveto-osa + erillisartikkelit)

#### Tiivistelmä

Monografia

Tämä väitöskirja käsittelee millimetriaaltoalueen radioetupään suunnittelua ja toteutusta erilaisilla mikropiirien valmistusteknologioilla. Erityisesti käsitellään millimetriaaltoalueen piireihin liittyviä asioita, kuten siirtojohtoja ja transistorimalleja piensignaalisimuloinneissa sekä kohinan mallintamista. Näille piireille löytyy useita erilaisia sovelluksia, kuten esimerkiksi nopeat 60 GHz:n radiolinkit ja ilmakehän kosteuspitoisuusmittaukset vesimolekyylin resonanssitaajuudelle 183 GHz:iin asti.

Transistorimalli on laskettu mitatusta datasta käyttäen hyväksi ainostaan saturaatiossa saatuja tuloksia. Transistorin ominaisuuksien laskemisessa käytetään myös koplanaariseen siirtojohtoympäristöön suunniteltuja avointa ja oikosuljettua testirakennetta. Ulkoiset parasiittiset ominaisuudet lasketaan lineaarisen regression avulla ja niiden vaikutuksen poistamisen jälkeen lasketulla piensignaalimallilla simuloidaan transistorin ominaisuuksia 110 GHz:iin asti. Kohinamalli perustuu V-alueen (50-75 GHz) kohinaparametrimittauksiin sekä avoimen ja oikosuljetun testirakenteen kohinamatriiseihin. Näin saatujen kohinalähteiden ja niiden korrelaation avulla voidaan simuloida transistorin kohinaominaisuuksia laajalla kaistalla. Lisäksi kohinalähteet sisältävän piensignaalimallin avulla simuloidaan kolmea erilaista vahvistinta ja tuloksia verrataan mitattuihin arvoihin. Nämä simulaatiot vastaavat erittäin hyvin mitattuja tuloksia.

Kirjassa käsitellään myös muutamia millimetriaaltoalueen vähäkohinaisiin vahvistimiin ja sekoittimiin liittyviä suunnitteluperiaatteita. Niitä ovat etupäähän liittyvät järjestelmänäkökohdat sekä transistorin valintaan liittyvät asiat. Mittaustekniikkaa esittelevässä kappaleessa esitellään muutamia millimetriaaltoalueen mittauksiin vaikuttavia erityispiirteitä yksityiskohtaisemmin. Mitttauslaitteiston eri osien, kuten mittakärkien ja harmonisen sekoittimen, aiheuttamia häviöitä tutkitaan. Millimetriaaltoalueen kohinamittaukset vaativat erityistä huomiota, koska mittauslaitteistoon täytyy liittää alassekoitus, joko toteutettuna mitattavalla piirillä itsellään tai ulkoisen harmonisen sekoittimen avulla. Empiirisiä tuloksia esitellään niin yhdistepuolijohde- kuin pii-piireiltä mitattuina tuloksina, erityisesti GaAs-HEMT- ja CMOSteknologioilla toteutetuista piireistä. Tuloksia esitetään vähäkohinaisista vahvistimista 94, 155 ja 183 GHz:n taajuusalueille. 183 GHz:n vahvistin saavuttaa 16 dB vahvistuksen ja 7,4 dB kohinaluvun. Lisäksi kaksi 60 GHz:n radioetupäätä on toteutettu ja mitattu. Toinen on valmistettu 150 nm GaAs PHEMT -teknologialla ja toinen 65 nm CMOS-teknologialla. GaAs-radioetupää sisältää 3-asteisen vahvistimen ja peilitaajuutta vaimentavan sekoittimen, kun taas piillä toteutettu radioetupää koostuu balansoidusta aktiivisekoittimesta ja 5-asteisesta vahvistimesta.

Avainsanat vähäkohinainen vahvistin, millimetriaaltoalueen vastaanotin, siirtojohdot

| ISBN (painettu) 978-952-60 | -5804-7 ISBN (p                                     | <b>df)</b> 978-952-60-5805-4     |  |

|----------------------------|-----------------------------------------------------|----------------------------------|--|

| ISSN-L 1799-4934           | ISSN (painettu) 1799-4                              | 1934 <b>ISSN (pdf)</b> 1799-4942 |  |

| Julkaisupaikka Helsinki    | Painopaikka Helsinki                                | Vuosi 2014                       |  |

| Sivumäärä 216              | <b>urn</b> http://urn.fi/URN:ISBN:978-952-60-5805-4 |                                  |  |

# **Preface**

The work for this dissertation was carried out in the Department of Microand Nanosciences at Aalto University. The work was done in connection with several projects, including the Lalamo, Nastec, Brawe, and Beams projects, funded by the Finnish Funding Agency for Technology and Innovation (Tekes), and several companies, such as Nokia Research Center, Nokia Siemens Networks, Elektrobit, DA-Design, and Elisa. The amplifiers at operating frequencies of 94, 155, and 183 GHz were developed for millimeter-wave projects funded by the European Space Research and Technology Centre (ESTEC). Moreover, the work was supported by the Academy of Finland as a part of the Millimono, Uncmos, and Famos projects as well as by the Centre of excellence SMARAD and SMARAD-2 programs.

I would like to express my gratitude to the Department of Micro- and Nanosciences for giving me the opportunity to work on various projects and also do research in the field of microelectronics. I wish to thank the Jenny and Antti Wihuri Foundation and the Ulla Tuominen Foundation for their financial support.

I also wish to thank the former head of department, Professor Kari Halonen, for acting as supervisor and superior. I warmly thank Dr.-Ing. Michael Schlechtweg and Professor Markus Törmänen for reviewing my thesis. I wish to thank both Professor Kari Halonen and emeritus Professor Veikko Porra for the opportunity to work on this interesting research area.

I am also grateful to several colleagues, Dr. Mikko Varonen, Dan Sandström, Jan Riska, and Dr. Pekka Kangaslahti, for their co-operation, support, and stimulating discussions. During the project work, I was also able to co-operate with Fraunhofer IAF as a part of the ESTEC funded projects and, thus, I am thankful to Dr. Matthias Seelmann-Eggebert and Axel Tessmann for this opportunity. I had lively and fruitful discussions with Tapani Närhi from ESTEC during many project meetings. I want to thank Petri Jukkala and Ari Alanne from DA-Design Oy for discussions and support. In addition, I want to thank Jan Riska, Tero Tikka, Dr. Ville Saari,

Preface

Pasi Juurakko, Ali Vahdati, and Dristy Parveg for sharing the office with me.

Furthermore, I wish to thank my friends for pleasant leisure time as well as refreshing badminton games, which gave me an excellent break from work. I wish to thank my mother Päivi, in 2010 passed away father Matti and my sister Matilda for encouragement and support during the entire time it took to complete this dissertation. I am also grateful to Miia for support during the writing of this dissertation.

Espoo, August 2014

Mikko Kärkkäinen

# **Contents**

| Pre | eface .    | vii                                            |

|-----|------------|------------------------------------------------|

| Co  | ntent      | six                                            |

| Lis | t of p     | ublicationsxi                                  |

| Au  | thor's     | contributionxv                                 |

| Lis | t of al    | bbreviationsxix                                |

| Lis | t of sy    | ymbolsxxiii                                    |

| 1.  | Intr       | oduction1                                      |

| 1   | .1         | Objectives and contents of this thesis2        |

| 2.  | Pass       | sive components5                               |

| 2   | 2.1        | Transmission lines                             |

| 2   | 2.2        | Capacitors in CMOS                             |

| 3.  | Tra        | nsistor9                                       |

| 3   | 3.1        | Transistor model                               |

| 3   | 3.2        | Noise characteristics                          |

| 3   | 3.3        | Comparison to experimental amplifier results22 |

| 4.  | Rec        | eiver system27                                 |

| 2   | <b>1.1</b> | Receiver front-end performance measures27      |

| 2   | 1.2        | Low-noise amplifier circuit design             |

| 2   | 1.3        | Mixer circuit design31                         |

|     | 4.3.       | 1 Active and passive mixers                    |

| 5.  | Mea        | surement techniques35                          |

| 6.  | Inte       | egrated millimeter-wave amplifiers             |

| 6   | <b>5.1</b> | 94-GHz amplifier41                             |

# Contents

| 6.2      | 155-GHz amplifier                                 | .45 |

|----------|---------------------------------------------------|-----|

| 6.3      | 183-GHz amplifiers                                | .49 |

| 7. Rec   | eeiver front-ends for 60-GHz applications         | .53 |

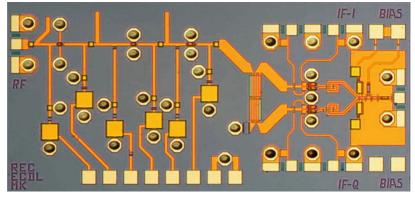

| 7.1      | Realized receiver front-ends                      | .53 |

| 7.2      | Receiver front-end in 150-nm PHEMT GaAs tehnology | .54 |

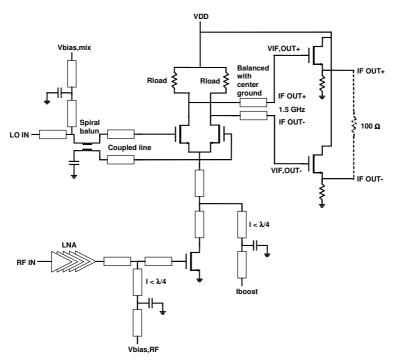

| 7.3      | Receiver front-end in 65-nm CMOS technology       | .55 |

| 8. Cor   | nclusions                                         | •57 |

| Bibliogr | aphy                                              | .59 |

| Publicat | tions                                             | .69 |

# List of publications

This dissertation consists of an overview and of the following publications.

- I M. Kärkkäinen, D. Sandström, M. Varonen, and K. A. I. Halonen, "Transmission Line and Lange Coupler Implementations in CMOS," in *Proc. of the European Microwave Integrated Circuits Conference*, Paris, France, Sept. 2010, pp. 357-360.

- II M. Kärkkäinen, M. Varonen, D. Sandström, T. Tikka, S. Lindfors, and K. A. I. Halonen, "Design Aspects of 65-nm CMOS MMICs," in *Proc. of the European Microwave Integrated Circuits Conference*, Amsterdam, the Netherlands, Oct. 2008, pp. 115-118.

- III D. Sandström, M. Varonen, M. Kärkkäinen, and K. A. I. Halonen, "W-Band CMOS Amplifiers Achieving +10 dBm Saturated Output Power and 7.5 dB NF," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 12, pp. 3403-3409, Dec. 2009.

- **IV** M. Kärkkäinen, M. Varonen, P. Kangaslahti, and K. Halonen, "Integrated Amplifier Circuits for 60 GHz Broadband Telecommunication," *Analog Integrated Circuits and Signal Processing*, vol. 42, no. 1, pp. 37-46, Jan. 2005.

- V M. Varonen, M. Kärkkäinen, M. Kantanen, and K. A. I. Halonen, "Millimeter-Wave Integrated Circuits in 65-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 9, pp. 1991-2002, Sept. 2008.

- **VI** D. Sandström, M. Varonen, M. Kärkkäinen, and K. A. I. Halonen, "60 GHz amplifier employing slow-wave transmission lines in 65-nm CMOS," *Analog Integrated Circuits and Signal Processing*, vol. 64, no. 3, pp. 223-231, Sept. 2010.

List of publications

VII M. Varonen, M. Kärkkäinen, J. Riska, P. Kangaslahti, and K. Halonen, "Resistive HEMT Mixers for 60-GHz Broad-Band Telecommunication," *IEEE Transactions on Microwave Theory and Techniques*, vol. 53, no. 4, pp. 1322-1330, Apr. 2005.

VIII M. Kärkkäinen, M. Varonen, M. Kantanen, T. Karttaavi, R. Weber, A Leuther, M. Seelmann-Eggebert, T. Närhi, and K. A. I. Halonen, "Coplanar 94 GHz Metamorphic HEMT Low Noise Amplifiers," in *IEEE Compound Semiconductor IC Symposium Technical Digest*, San Antonio, TX, Nov. 2006, pp. 29-32.

IX M. Varonen, M. Kärkkäinen, M. Kantanen, M. Laaninen, T. Karttaavi, R. Weber, A. Leuther, M. Seelmann-Eggebert, T. Närhi, J. Lahtinen, and K. A. I. Halonen, "W-band low-noise amplifiers," *Proceedings of the European Microwave Association*, vol. 3, no. 4., pp. 358-366, Dec. 2007.

X M. Kantanen, M. Kärkkäinen, M. Varonen, M. Laaninen, T. Karttaavi, R. Weber, A Leuther, M. Seelmann-Eggebert, T. Närhi, J. Lahtinen, and K. Halonen, "Low noise amplifiers for D-band," *Proceedings of the European Microwave Association*, vol. 4, no. 4., pp. 268-275, Dec. 2008.

XI M. Kärkkäinen, M. Kantanen, S. Caujolle-Bert, M. Varonen, R. Weber, A. Leuther, M. Seelmann-Eggebert, A. Alanne, P. Jukkala, T. Närhi, and K. A. I. Halonen, "MHEMT G-Band Low-Noise Amplifiers," *IEEE Transactions on Terahertz Science and Technology*, vol. 4, no. 4, pp. 459-468, Jul. 2014.

XII M. Varonen, M. Kärkkäinen, J. Riska, P. Kangaslahti, and K. Halonen, "Up- and Downconverter MMICs for 60-GHz Broad-Band Telecommunication," in *IEEE MTT-S International Microwave Symposium Dig.*, San Francisco, CA, Jun. 2006, pp. 1501-1504.

XIII M. Kärkkäinen, M. Varonen, D. Sandström, and K. A. I. Halonen, "60-GHz Receiver and Transmitter Front-Ends in 65-nm CMOS," in *IEEE MTT-S International Microwave Symposium Dig.*, Boston, MA, Jun. 2009, pp. 577-580.

List of publications

# **Author's contribution**

# Publication I: "Transmission Line and Lange Coupler Implementations in CMOS"

This publication was the result of a collaborative effort. The author designed various transmission line structures in 65-nm CMOS technology. The author also measured and analyzed the results. The Lange coupler presented in the study was designed and implemented by Dan Sandström and Mikko Varonen.

### Publication II: "Design Aspects of 65-nm CMOS MMICs"

This publication was the result of a collaborative effort. The author was responsible for writing most of the paper. The author contributed to the design and analysis of the transmission line structures and also designed and analyzed the transistor's test structure. The transistor's layout was designed by Tero Tikka.

# Publication III: "W-Band CMOS Amplifiers Achieving +10 dBm Saturated Output Power and 7.5 dB NF"

This publication was the result of a collaborative effort. The author was mainly responsible for the de-embedding of the transistor data model and the custom capacitor design for the 100 GHz amplifier. The slow-wave shield was designed by Mikko Varonen.

# Publication IV: "Integrated Amplifier Circuits for 60 GHz Broadband Telecommunication"

This publication was mainly contributed by the author. The author was responsible for writing the manuscript. The author designed the low-noise amplifier and fitted the transistor noise model to the measured noise data. The measurements of the amplifier and transistor's test structure were

#### Author's contribution

carried out at the Millimetre Wave Laboratory of Finland. The sections concerning the transistor's characterization and the low-noise amplifier were written by the author.

# Publication V: "Millimeter-Wave Integrated Circuits in 65-nm CMOS"

This publication was the result of a collaborative effort. The author has contributed to the analysis of the transistor and capacitor measurement data and de-embedding. The author has also contributed to the development of the coplanar waveguide structure on silicon. The measurements were carried out at the Millimetre Wave Laboratory of Finland. The section concerning the transistor's characterization was written by the author.

# Publication VI: "60 GHz amplifier employing slow-wave transmission lines in 65-nm CMOS"

This publication was the result of a collaborative effort. The author was mainly responsible for the de-embedding of the transistor data model.

# Publication VII: "Resistive HEMT Mixers for 60-GHz Broad-Band Telecommunication"

This publication was the result of a collaborative effort. The author has been involved in the image rejection mixer measurements in co-operation with M. Varonen, designed and analyzed one of hybrids and contributed to the writing of this article.

# Publication VIII: "Coplanar 94 GHz Metamorphic HEMT Low Noise Amplifiers"

This publication was the result of a collaborative effort. The author designed one of the amplifiers and contributed to the writing of the paper. The measurements were carried out at the Millimetre Wave Laboratory of Finland.

## Publication IX: "W-band low-noise amplifiers"

This publication was the result of a collaborative effort. The author designed one of the amplifiers and contributed to the writing of the paper.

The measurements were carried out at the Millimetre Wave Laboratory of Finland.

#### Publication X: "Low noise amplifiers for D-band"

This publication was the result of a collaborative effort. The author designed one of the amplifiers and contributed to the writing of the paper. The measurements were carried out at the Millimetre Wave Laboratory of Finland.

#### **Publication XI: "MHEMT G-Band Low-Noise Amplifiers"**

This publication was the result of a collaborative effort. The author designed one of the amplifiers and wrote the paper. The author was also involved in designing the second-run, 183-GHz amplifier and drew the layout for it. The circuit simulations for the second-run amplifier were carried out by Sylvain Caujolle-Bert. The different variations of the second-run simulations were suggested by Matthias Seelmann-Eggebert. The transistor simulations and analysis presented at the beginning of the paper were the work of the author. DA-Design Oy developed the split block package and handled the chip assembly. The measurements were carried out at the Millimetre Wave Laboratory of Finland.

# Publication XII: "Up- and Downconverter MMICs for 60-GHz Broad-Band Telecommunication"

This publication was the result of a collaborative effort. The author designed the three-stage low-noise amplifier for the receiver front-end and helped develop the measurement setup and do the measurements. The resistive mixer was designed by Jan Riska. The section concerning the receiver front-end was written by the author.

# Publication XIII: "60-GHz Receiver and Transmitter Front-Ends in 65-nm CMOS"

This publication was the result of a collaborative effort. The author designed the active downconversion mixer for the receiver front-end. The five-stage amplifier and spiral balun were designed by Mikko Varonen. The measurements were carried out partly by the Millimetre Wave Laboratory of Finland and partly by the author. The section concerning the receiver front-end was written by the author.

Author's contribution

# List of abbreviations

AC alternating current

AD analog-to-digital converter

ADS Advanced Design System (simulation software from Agilent)

BB baseband

BB<sub>I</sub> in-phase baseband signal BB<sub>O</sub> quadrature baseband signal

CE common emitter

CG common gate

CMOS complementary metal-oxide semiconductor

CPU central processing unit CPW coplanar waveguide

CPWCS cut shield coplanar waveguide CPWSW slow-wave coplanar waveguide

CS common source

dB decibel

D-band frequency band from 110 to 170 GHz dBm decibels relative to one milliwatt

DC direct current double sideband

E-band frequency band from 60 to 90 GHz

F noise factor

FET field-effect transistor GaAs gallium arsenide

G-band frequency band from 140 to 220 GHz

GCPW grounded coplanar waveguide

GHz gigahertz GND ground

GSG ground-signal-ground probe configuration

HBT heterojunction bipolar transistor HEMT high electron mobility transistor

Hz Hertz

IC integrated circuit

# List of abbreviations

ICP intercept point

IF intermediate frequency

IN input

InP indium phosphide

IQ, I/Q in-phase/quadrature-phase signal

IRR image rejection ratio

IRR<sub>dB</sub> image rejection ratio in decibels

J<sub>d</sub> drain current density

l length (also electrical length)

LNA low-noise amplifier LO local oscillator

LRRM line-reflect-reflect-match calibration method

LSB lower sideband mA milliampere

MAG maximum available gain

MHEMT metamorphic high electron mobility transistor

MilliLab Millimetre Wave Laboratory of Finland

MIM metal-insulator-metal

mm millimeter

mm<sup>2</sup> square millimeter

MMIC monolithic microwave integrated circuit

MOSFET metal oxide semiconductor field effect transistor

MS microstrip line

MSG maximum stable gain

mW milliwatt

NF noise figure

nm nanometer

NMOS n-type metal-oxide semiconductor

OUT output

PGA programmable gain amplifier

pH picohenry

PHEMT pseudomorphic high-electron-mobility-transistor

PLL phase locked loop PS phase shifter

QVCO quadrature voltage-controlled oscillator

RF radio frequency

RX receiver

s, (s) simulated value SiGe silicon germanium

SiGe:C silicon germanium carbon

SOI silicon-on-insulator

# List of abbreviations

TRL thru-reflect-line calibration method

USB upper sideband

V, v voltage

V-band frequency band from 50 to 75 GHz

$V_{bias} \hspace{1.5cm} bias \hspace{0.1cm} voltage$

VCO voltage-controlled oscillator

VDD supply voltage

VGA variable-gain amplifier

W watt

W-band frequency band from 75 to 110 GHz

WG waveguide

W-HDMI wireless high definition multimedia interface

WLAN wireless local area network

X-band frequency band from 8 to 12 GHz

# List of symbols

$\begin{array}{ll} A_{IM} & \text{amplitude of the signal at the image frequency} \\ A_{LO} & \text{amplitude of the signal at the local frequency} \\ A_{mix,x} & \text{signal coming from a mixer (amplitude), branch x} \\ A_{RF} & \text{amplitude of the signal at the radio frequency} \end{array}$

B bandwidth

$\begin{array}{lll} C_A & & \text{noise correlation matrix} \\ C_{db} & & \text{drain-bulk capacitance} \\ C_{ds} & & \text{drain-source capacitance} \\ C_{gs} & & \text{gate-source capacitance} \end{array}$

C<sub>si</sub> drain-bulk network capacitance

F<sub>cas,min</sub> noise factor (or figure) of infinite number of cascaded

transistors matched to optimum noise measure

$f_{MAX}$  maximum frequency of oscillation  $F_X$  noise factor of block number x

$\begin{array}{lll} g_m & transconductance \\ G_X & gain of block number x \\ i_d & drain noise current \\ i_g & gate noise current \\ Im & imaginary part \\ j & imaginary unit \end{array}$

J<sub>d</sub> drain current density

k Boltzmann's constant, also Rollett's stability factor

L length of transistor gate

$\begin{array}{ll} L_d & drain \, inductance \\ L_g & gate \, inductance \\ L_s & source \, inductance \end{array}$

$M_{OPT}$  optimum noise measure matching  $N_f$  number of transistor fingers

$N_{IN}$  input noise power  $N_{OUT}$  output noise power

$P_{o}$  phase of the o-phase signal branch  $P_{90}$  phase of the 90-phase signal branch

# List of symbols

$\begin{array}{ll} P_{180} & phase \ of \ the \ 180\mbox{-phase signal branch} \\ P_{270} & phase \ of \ the \ 270\mbox{-phase signal branch} \\ P_{IM} & signal \ power \ on \ the \ image \ frequency} \\ P_{RF} & signal \ power \ on \ the \ radio \ frequency \end{array}$

R<sub>d</sub> drain resistance

R<sub>ds</sub> drain-source resistance

Re real part

R<sub>g</sub> gate resistance

R<sub>gs</sub> gate-source resistance

$R_n$  noise resistance  $R_s$  source resistance

S gap width of a coplanar waveguide, also scattering

parameter(s)

$s_{xx}$ ,  $S_{xx}$  s-parameter

T noise temperature

$\begin{array}{ll} T_d & & \text{noise temperature of the drain resistance} \\ T_g & & \text{noise temperate of the gate resistance} \end{array}$

T<sub>a</sub> ambient temperature

$\begin{array}{ll} V_g & & \text{gate voltage} \\ V_d & & \text{drain voltage} \end{array}$

W center conductor width of a coplanar waveguide, also width

of transistor gate

w angular frequency (also ω)

WR-NN waveguide band, waveguide package with NN-band size

connectors

W<sub>f</sub> finger width of a transistor gate

$Z_0$  characteristic impedance  $z_{00}$  z-axis crossing point

$y_{xx}, Y_{xx}$  y-parameter  $z_{xx}, Z_{xx}$  z-parameter

$\Gamma_{\text{opt}}$  optimum reflection coefficient

$\Delta A$  amplitude difference  $\theta$  phase difference  $\lambda$  wavelength

ω angular frequency, also w

$\Omega$  ohm(s)

# 1. Introduction

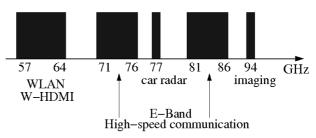

The demand for high-speed, short-range wireless data transfer has increased as high definition video and other digital multimedia content have become more widely available. Other prospective millimeter-wave applications include collision avoidance radar for a car, 60-GHz data communication, 71-86 GHz point-to-point networks, and security scanners, as well as medical and industrial sensors. As an example, a high data rate system is needed if one wants to send a high-definition video stream wirelessly from a media server to a flat-screen television hanging on opposite wall of a living room. The 60-GHz range has garnered a great deal of interest as a possible frequency for high data rate systems since a wide bandwidth is available license free worldwide [1][2]. Some possible millimeter-wave applications are presented in figure 1. A millimeter-wave radio system can also be a solution when the use of more crowded lower frequencies is not desired. However, this means that the millimeter-wave transceiver has to be manufactured in a cost-effective manner. Traditional millimeter-wave systems have been constructed from bulky and expensive waveguide parts, which are not suitable for portable and low-cost consumer applications. The millimeter-wave system should not consume much energy and it should not contain multiple parts that have to be manufactured with high levels of precision. The first microwave integrated circuit (MMIC) was introduced in 1976, which presents an integrated X-band amplifier [3].

Fig. 1. Some possible millimeter-wave applications [4].

## Introduction

Previously, millimeter-wave-integrated circuits were manufactured using compound semiconductor technologies, such as gallium arsenide (GaAs) or indium phosphide- (InP) based high electron mobility transistors (HEMT). These technologies are now only rarely used in regular consumer applications and the wafer diameter can be 6 inches or even less. Digital memory, computer central processing units (CPU), digital signal processing, and so forth, are mostly integrated using complementary metaloxide semiconductor (CMOS) technology. This means that there are obvious benefits to integrating millimeter-wave front-ends on the same microchip. The absence of bulky and cost-inefficient off-chip interconnections is one of the advantages of CMOS integration. Despite the fact that it is a promising technology, there may be challenges related to the manufacturing yield of highly integrated, large communication systems and to the low resistivity silicon substrate, which can introduce high noise levels and also be difficult to model accurately. Millimeter-wave CMOS circuits began to be developed between the years 2002 and 2007. One of the first circuits was a 51-GHz CMOS VCO [5]. Active and passive component modeling in particular was an issue; the 60-GHz band was of particular interest in 2004 [6], and in 2007 a 104-GHz CMOS amplifier was first developed [7]. Recently, good results from millimeter-wave amplifiers have been obtained with 45-nm SOI CMOS technology as well [8].

Outside the mass market millimeter-wave applications, there are scientific instruments that require the best possible performance regardless of yield, cost, and size or, sometimes, they require an optimum trade-off between these characteristics. For example, one scientific millimeter-wave application is atmospheric remote sensing of the Earth using radiometric instruments in a satellite. To understand the behavior of the Earth's atmosphere with ever greater precision, temperature and humidity profiling are of great interest. A humidity profile can be obtained from measurements of the water molecule absorption frequencies at 23 and 183 GHz. These results will be compared to radiometric data obtained from the atmospheric window frequencies of 90, 130, and 166 GHz. To improve the sensitivity of these profiling radar receivers, it is possible to use a high-performance, low-noise amplifier as the first component after the antenna, if such an amplifier can be designed and manufactured [9][10].

## 1.1 Objectives and contents of this dissertation

The objective of this dissertation is to present the design, analysis and results of millimeter-wave-integrated circuits. These circuits have been realized in various technologies, such as GaAs pseudomorphic and metamorphic HEMT and CMOS. The operating frequencies range from 60

to 183 GHz. Most of the work concentrates on low-noise amplifiers, although two different 60-GHz radio front-ends are also discussed in the study. The analysis section concentrates on silicon transistor small-signal modeling issues and transmission line structures on silicon and compares them to similar structures on GaAs. The transistor noise is characterized as well. The transistor model is verified by comparing it to the measured results obtained from three different amplifiers operating at 60 and 100 GHz.

The first part of the dissertation discusses the design issues and questions related to transmission lines. Then, small-signal transistor modeling is presented. Some system and design issues as well as the applied measurement techniques are likewise discussed. Subsequently, experimental results from several integrated circuits are presented and compared to previously published results. The conclusions are summarized and issues related to future work are discussed. In the second part of the dissertation, the published papers are presented.

Introduction

# 2. Passive components

In millimeter-wave circuits, passive components, such as transmission lines and capacitors, can be used for matching purposes. Transmission lines are necessary for signal transfer as well. The passive components, which were available in the design kit, were not modeled at millimeter-wave frequencies and they may have large and unpredictable parasitics. In CMOS integrated circuits, it may not be obvious how to create the layout and model the behavior of these components. In the following section, transmission lines and capacitors are discussed in more detail.

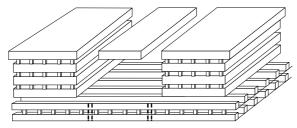

#### 2.1 Transmission lines

For high frequency circuit applications a transmission line structure can be used. Transmission lines are inherently scalable in length and once properly characterized, these lines can be used in many circuit blocks for signal transfer and matching purposes [11][Publication I][Publication II]. The transmission line structures are of particular interest for millimeterwave CMOS circuits, because the losses caused by the substrate, metals, and dielectrics may increase attenuation to infeasible or unpractical levels. Figure 2 shows an example of a transmission line structure. This structure has been designed for CMOS technology and it fulfills the metal density requirements even when no dummy metal fillings are allowed inside the structure. The downward-extended ground planes are drawn with lower metal layers to fulfill the metal density requirements of the manufacturing technology. A floating shield consisting of narrow strips drawn using the lower metal layers can be realized perpendicular to the current flow in the CPW center conductor [12][13]. This type of a line creates a slow-wave CPW (CPWSW) structure, which has a longer electrical length than a conventional CPW with the same geometrical length. Although the slowwave CPW has a higher self-resonance quality factor, it also has a more limited range of feasible characteristic impedances compared to a conventional coplanar waveguide. This is because the capacitance per unit length is increased, whereas the inductance is approximately the same as

# Passive components

for a conventional CPW having the same W and S [14]. For a high-impedance slow-wave CPW line the signal-to-ground spacing can be increased or the width of the signal line can be decreased. However, the signal-to-ground spacing is limited by the design rules while the width of the center conductor is limited by metallic losses [Publication I].

Fig. 2. A simplified CPW structure realized on silicon. (© 2010 EuMA, with permission from [Publication I]).

In this work, a third type of CPW type was developed as a test structure in CMOS. The slow-wave shield grid was cut at the center points of the slots of the CPW. The structure of the cut shield CPW (CPWCS) and the slow-wave CPW (CPWSW) are shown in figure 3. The idea of this third type of CPW is to decrease the capacitance of the line (thus, increase characteristic impedance) and maintain reasonable substrate shielding. With a narrower center conductor (8  $\mu$ m width and 11  $\mu$ m gap) it is possible to increase the line inductance, and, thus, the impedance, even further. Ways to change the line capacitance have also been discussed elsewhere [15]. The substrate shield of the lines is created using the two lowest metal levels [Publication I].

Fig. 3. A simplified CPW structure realized on silicon with a floating shield underneath. The dashed lines show where the cut shield version has been cut. (© 2010 EuMA, with permission from [Publication I]).

To characterize the CPW-lines, the test structures were measured onwafer and the parasitic shunt capacitances of the pads were subtracted from the line measurement result. Figure 4 shows one of the developed test structures. The characteristic impedance, attenuation and propagation factors were calculated using equations found in a prior study [16]. The results have been compiled in table 1.

Fig. 4. A micrograph of the cut shield CPW test structure in 65-nm CMOS. The line length, excluding pads and transitions, is 215  $\mu$ m. (© 2010 EuMA, with permission from [Publication I]).

Table 1. Comparison of the different transmission line realizations in 65-nm CMOS at 60 GHz [Publication I]. The GaAs CPW results have been simulated for purposes of comparison.

|           | W [µm] | S [µm] | Z <sub>0</sub> [Ohm] | A [dB/mm] | $A/\lambda [dB/\lambda]$ |

|-----------|--------|--------|----------------------|-----------|--------------------------|

| CPW       | 12     | 9      | 55                   | 3         | 5                        |

| CPWCS     | 8      | 11     | 67                   | 2         | 3.3                      |

| CPWSW     | 12     | 9      | 40                   | 2         | 2.5                      |

| CPWSW8    | 8      | 11     | 55                   | 1.4       | 2.1                      |

|           |        |        |                      |           |                          |

| GaAs GCPW | 37     | 6.5    | 31 *                 | 0.6 *     | 1.2 *                    |

| GaAs GCPW | 17     | 16.5   | 52 *                 | 0.4 *     | 0.8 *                    |

| GaAs GCPW |        | 21.5   | 69 *                 | 0.5 *     | 1.1 *                    |

<sup>\*</sup> Simulated using design kit models for comparison purposes.

# 2.2 Capacitors in CMOS

Millimeter-wave integrated circuits typically utilize capacitors for RF short-circuiting and DC-decoupling purposes. The capacitors may also be used as part of a matching circuit. In CMOS technology, the metal-insulator-metal (MIM) capacitor is one of the simplest types of capacitors. It is simple to model and the parasitics are easy to predict as opposed to complex, interleaved finger capacitors that use several metal levels and both sidewall and plate capacitances between the fingers. However, the MIM capacitors

# Passive components

may not be available in a chosen technology and library finger capacitors in a design kit may have large and unpredictable parasitics. To overcome this problem, a custom capacitor, which has wide separate fingers drawn with upper metal levels, was designed in this work. This is done to minimize the ground capacitance from the lower levels to the substrate and decrease the parasitic series resistances and inductances by using wide fingers instead of a large number of narrow fingers [Publication III]. Of course, the drawback in the case of wide fingers is the reduced capacitance per unit area. This may not become a problem if the operating frequency is quite high (100 GHz or higher) and, thus, the required capacitances are small.

# 3. Transistor

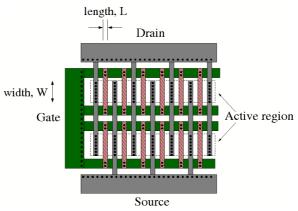

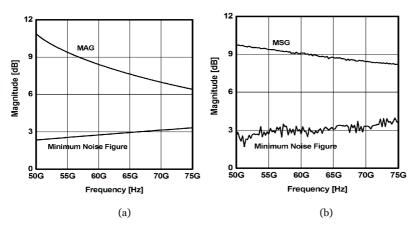

A fast transistor is needed, when trying to improve the amplifier performance to the 60-GHz range and even beyond. One convenient way to measure the transistor speed is the maximum frequency of oscillation, since this is also the frequency of unity power gain. The gain of the transistor can be evaluated as a function of frequency by using the maximum stable gain (MSG), when k < 1, and the maximum available gain, when k > 1. At high enough frequencies, the gain of a transistor is limited by the parasitics and not by its stability. By trying to minimize the gate resistance, it is possible to obtain lower minimum noise figure and high f<sub>MAX</sub>, which results higher available gain. The optimum values for the width of a single finger W<sub>f</sub> and drain current density J<sub>d</sub> are approximately 1 µm and 0.20 mA/µm, respectively [17][18]. These values give the best  $f_{MAX}$  and, thus, the best maximum available gain. For the optimum noise figure a value of 0.15 mA/µm has been proposed [17][18]. The noise performance can be further optimized by selecting the best number of gate fingers n<sub>f</sub> for the transistor. The noise figure is minimized by selecting a large n<sub>f</sub>, because of the reduced total gate resistance. However, the number of gate fingers n<sub>f</sub> cannot be increased arbitrarily, because at some point the increased drain current (assuming constant drain current density scaling) will eventually produce more noise and result in a higher noise figure [19][20]. Figure 5 shows the basic principle behind the transistor layout.

Fig. 5. Transistor layout. (© 2009 IEEE, with permission from [Publication III])

The width of the transistor finger and current density can be selected to maximize the  $f_{MAX}$  and, thus, the maximum available gain at high frequencies (k > 1). The number of fingers in each transistor and, eventually, the number of transistors in parallel can be selected by looking at the minimum noise figure, gain, power consumption, and linearity. The impedances required for matching can also be one of the limiting factors. The maximum stable gain and the minimum noise figure are approximately the same for different numbers of transistors and fingers, when considering a constant drain current density [21][22]. The  $f_{MAX}$ , the related maximum available gain (MAG) at high frequencies (k > 1), dc current consumption, and noise figure will be affected and they are important parameters when considering the low-noise amplifier design.

As an example, figure 6 compares a 2x25  $\mu$ m GaAs-PHEMT and a 90- $\mu$ m, 65-nm CMOS transistor in terms of their gain and noise. Their performance is quite similar and shows the potential of CMOS technology for millimeterwave applications. Both transistors have approximately 7–9 dB of gain and a 3–dB minimum noise figure from 55 to 60 GHz.

Fig. 6. The maximum stable and available gain (MSG/MAG) and minimum noise figure (NF<sub>min</sub>) are simulated for a 0.15- $\mu$ m GaAs pseudomorphic HEMT having a gate width of 2x25  $\mu$ m (a) and measured for an NMOS having a total width of 90  $\mu$ m in 65-nm CMOS (b) [Publication IV] [Publication V].

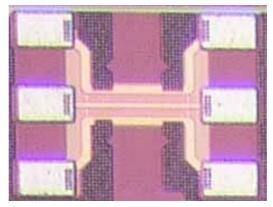

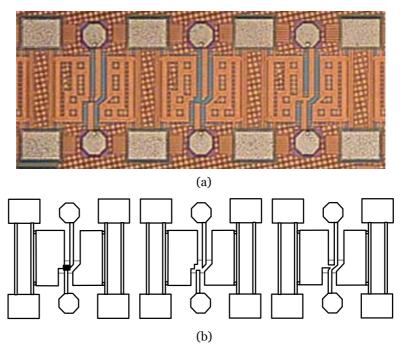

#### 3.1 Transistor model

When CMOS design first began, there was no small-signal model or noise model available for the 90/0.07- $\mu m$  NMOS transistor chosen as a suitable size for the V-band designs. This size was also the smallest of the originally available test set of transistors. In this work the transistor is de-embedded using open-short de-embedding [23] and a test structure is used that has a well-defined impedance and reasonable loss at the millimeter-wave

frequencies. The coplanar waveguide interconnections to the input and output pads were seen as a viable choice for the test structure. Figure 7 shows a micrograph of the realized test structure. The accuracy of the deembedding is degraded after 80 GHz [Publication V]. Recently, there has been a study indicating that it is possible to simulate transistors with SOI CMOS design kit models and RC-parasitics extraction up to 75 GHz accurately [8].

Fig. 7. Coplanar test structures for characterizing the transistor. The chip area is  $0.7 \times 0.3$  mm<sup>2</sup>. From left to right: transistor, open, and short test structure. Both a micrograph of the test structure (a) and a simplified layout drawing principle (b) are depicted.

In order to remove the effect of the connecting lines from the transistor measurement, the measured data has to be de-embedded first. The de-embedding is performed by using the open-short method [23]. There are issues related to characterizing the transistor at high frequencies when using scattering parameter measurements and test structures. These are the parasitics of the test structure, which have a pronounced effect and, the gain of the transistor, which is low above 110 GHz [24].

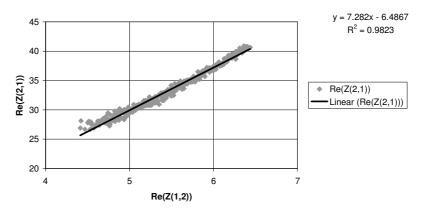

There are different ways to create a small-signal model, but some of them require several measurements and optimizations [25][26]. The goal in this work was to obtain an acceptable small-signal model for V-band circuit design in CMOS technology based on a single measured frequency sweep of a saturated transistor and the s-parameters of the corresponding open and short structures. To do this, the extrinsic parasitics are evaluated [25]. The values for  $R_{\rm g}$ ,  $R_{\rm d}$ ,  $R_{\rm s}$ , and  $L_{\rm d}$  were evaluated by fitting a line to the measured

#### Transistor

data as shown in figures 10, 11, 12, and 13, respectively. The gate inductance,  $L_{\rm g}$ , calculation requires two linear fitted lines and an additional fitted plane in three-dimensional space as in figures 14, 15, and 16, respectively. The resistances are evaluated using measured data from 34 to 60 GHz, whereas the data range for the inductances is from 70 to 110 GHz. These frequency ranges were selected to obtain a good linear fit and, thus, to reduce the effect of other frequency-dependent terms on the transistor's z-parameters.

The source parasitic inductance was evaluated separately from the short test structure [27] and later adjusted to minimize the frequency dependence of the transconductance in an iterative way since the  $L_g$  and  $L_d$  depend on the  $L_s$ . The transconductance can be plotted as a function of frequency for three different source inductance values (fig. 8) for the W/L = 90/0.07- $\mu$ m NMOS test transistor.

Fig. 8. The frequency dependence of the transconductance. The value for the source inductance is chosen to obtain as flat a transconductance as possible. In this case the nominal source inductance is 1.7 pH.

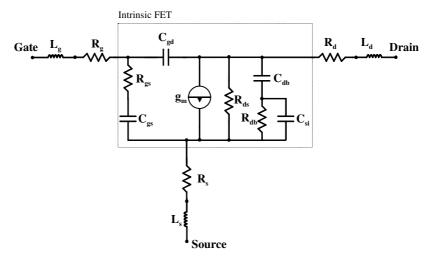

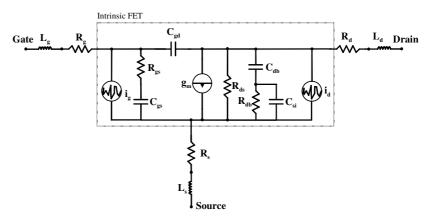

The series and shunt parasitics can then be subtracted from the deembedded transistor data [28]. The configuration of the extrinsic parasitics can be varied according to the test structure [29]. However, here it was discovered that the residual shunt capacitances are practically negligible. Finally, the intrinsic transistor component values can be calculated in a straightforward manner if the extrinsic parasitics are subtracted correctly [30]. However, the drain substrate network formed with the source and bulk connections needs special attention, because the conventional smallsignal model does not model its frequency dependence correctly [31]. The transistor model is presented in figure 9.

Fig. 9. The transistor model.

The source resistance can be evaluated using a parametric plot using deembedded transistor's z-parameters as follows

$$[x_1, x_2] = [\text{Re}\{Z_{12}\}, \text{Re}\{Z_{21}\}],$$

(1)

which is plotted in figure 10. Then, using a fitted line, the value of the source resistance can be simply calculated as

$$R_s = \frac{ICP}{1 - \frac{dx_2}{dx_1}},\tag{2}$$

where ICP is the x-axis intercept point and  $dx_2/dx_1$  is the slope of the line.

Fig. 10. A parametric plot for calculating the source resistance.

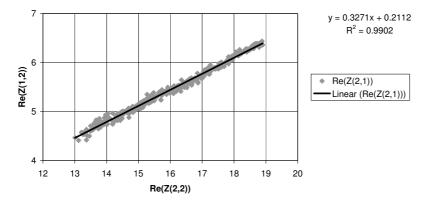

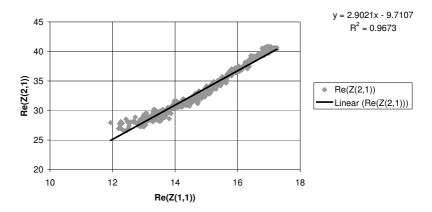

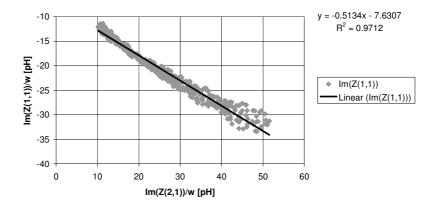

The values of the drain and gate resistances can be found in the same manner by plotting

$$[x_1, x_2] = [\text{Re}\{Z_{22}\}, \text{Re}\{Z_{12}\}],$$

(3)

and

$$[x_1, x_2] = [\text{Re}\{Z_{11}\}, \text{Re}\{Z_{21}\}],$$

(4)

respectively. These plots are presented in figures 11 and 12. The values are calculated as

$$R_d = \frac{ICP - R_s}{-\frac{dx_2}{dx_1}} - R_s \,, \tag{5}$$

and

$$R_{g} = \frac{ICP - R_{s}}{-\frac{dx_{2}}{dx_{1}}} - R_{s}, \tag{6}$$

where ICP is the x-axis intercept point and  $dx_2/dx_1$  is the slope of the corresponding line.

Fig. 11. A parametric plot for calculating the drain resistance.

Fig. 12. A parametric plot for calculating the gate resistance.

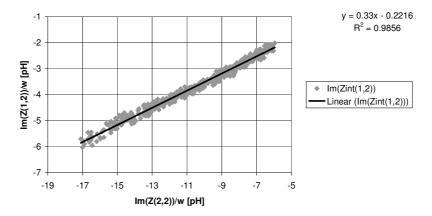

The drain inductance can be found by plotting

$$[x_1, x_2] = \left\lceil \frac{\operatorname{Im}\{Z_{22}\}}{\omega}, \frac{\operatorname{Im}\{Z_{12}\}}{\omega} \right\rceil \tag{7}$$

as in figure 13. From the fitted line, the value can then be calculated as follows:

$$L_d = \frac{ICP - L_s}{-\frac{dx_2}{dx_1}} - L_s, \tag{8}$$

where ICP is the intercept point,  $dx_2/dx_1$  is the slope of the line, and  $L_s$  is the source inductance.

Fig. 13. A parametric plot for calculating the drain inductance.

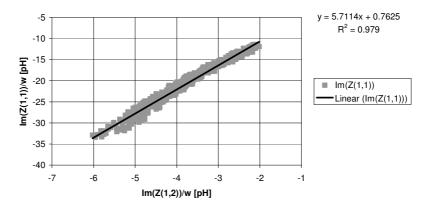

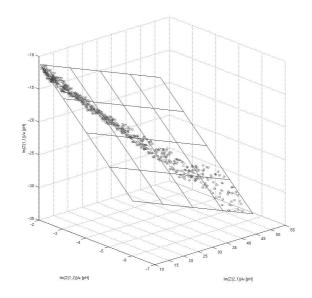

Calculating the gate inductance requires three plots: Two 2-dimensional plots and an additional three-dimensional plot. A line must be fitted to the first and second plot and then a plane must be fitted to the third plot as in figures 14–16. The three-dimensional parametric plot can be created using the following equation:

$$[x_{1}, x_{2}, x_{3}] = \left[\frac{\text{Im}\{Z_{21}\}}{\omega}, \frac{\text{Im}\{Z_{12}\}}{\omega}, \frac{\text{Im}\{Z_{11}\}}{\omega}\right], \tag{9}$$

which represents a plane of form ax+by+cz+d=0. It crosses the z-axis at point

$$z_{00} = -\frac{d}{c} \,. \tag{10}$$

The gate inductance value can then be found as follows:

$$L_{g} = z_{00} - L_{s} \cdot \left( 1 - \frac{dx_{3}}{dx_{1}} - \frac{dx_{3}}{dx_{2}} \right) \tag{11}$$

where  $dx_3/dx_1$  and  $dx_3/dx_2$  are slopes of the corresponding two dimensional parametric plots:

$$[x_1, x_2] = \left[\frac{\operatorname{Im}\{Z_{21}\}}{\omega}, \frac{\operatorname{Im}\{Z_{11}\}}{\omega}\right]$$

(12)

and

$$[x_1, x_2] = \left\lceil \frac{\operatorname{Im}\{Z_{12}\}}{\omega}, \frac{\operatorname{Im}\{Z_{11}\}}{\omega} \right\rceil, \tag{13}$$

respectively.

Fig. 14. A parametric plot for calculating the gate inductance.

Fig. 15. A parametric plot for calculating the gate inductance.

Fig. 16. A 3-dimensional parametric plot for calculating the gate inductance.

## Transistor

Finally, the extrinsic parasitics are shown in table 2. The source inductance is the only iterated value and all of the other values are calculated based on the properties of the parametric plots presented above.

Table 2. The extrinsic parasitics of the measured transistor.

| Rs | 1.00 | [Ohm] |

|----|------|-------|

| Rd | 1.50 | [Ohm] |

| Rg | 2.67 | [Ohm] |

| Ls | 1.70 | [pH]  |

| Ld | 4.10 | [pH]  |

| Lg | 5.40 | [pH]  |

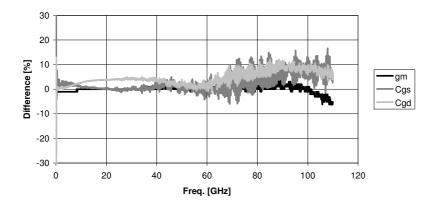

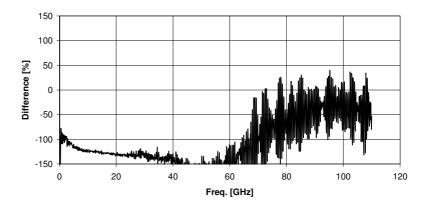

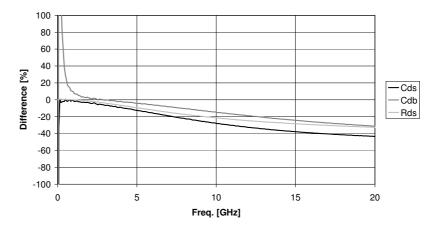

After removing the effect of the extrinsic parasitics, the intrinsic transistor elements can be calculated. The variation over frequency of the intrinsic elements is presented in figures 17–20.

Fig. 17. The variation in transconductance, gate-to-source capacitance, and gate-to-drain capacitance of the measured transistor.

Fig. 18. The variation in gate-to-source resistance of the measured transistor.

Fig. 19. The variation in drain-to-source capacitance, drain-to-bulk capacitance and drain-to-source resistance of the measured transistor. The values were obtained from low frequencies.

Fig. 20. The variation in bulk resistance and capacitance-to-silicon of the measured transistor. The values were obtained at a frequency of approximately 30 GHz.

#### 3.2 Noise characteristics

There has been a need to model the transistor noise characteristics, particularly at the V-band, to enable a low-noise amplifier design and accurate noise simulations. The pseudomorphic HEMT 2x25-µm transistor was measured in a test structure configuration and the scattering parameters were de-embedded using negative length transmission lines [32]. The geometry of the transmission line was approximated in ADS simulations using a coplanar waveguide model with average values for the center conductor and ground gaps. In the case of the noise parameters, the coplanar lines were added to the input and output of the small-signal transistor model (provided by the foundry). Then, the temperature of the resistors inside the small-signal model was set to 295 kelvins and the temperature of the drain resistor was adjusted until the simulation results resembled the measured noise parameters. Finally, the connecting lines could be removed and the model could be used for designing low-noise amplifiers [Publication IV]. There was no need for the gate resistor temperature to be higher than the ambient value. This type of a temperature noise model was originally presented in [33]. The effect of correlating noise sources can also be included [34].

Because it was assumed that the losses of the connecting lines would be significantly larger than in the case of the HEMT, a precise noise deembedding is necessary for the MOSFET. The loss and other characteristics are discussed in detail in chapter 2. By measuring the scattering parameters of the corresponding open and short structures it is possible to calculate the noise correlation matrices for the series and shunt impedances and remove their effect from the noise parameters of the entire transistor test structure [35]. The noise parameters of the transistor's test structure were measured using methods described in [36]. The noise correlation matrices  $C_{A,OPEN}$  and  $C_{A,SHORT}$  for the open and short test structures can be computed simply based on the measured y-parameters as

$$C_A = 2kT_a \operatorname{Re}(Y), \tag{14}$$

where k is Bolzmann's constant,  $T_a$  the ambient temperature and Y is the admittance matrix of the structure. The results are shown in figure 21. The de-embedded result shows a minimum noise figure of 3.0 dB for the W/L = 90/0.07  $\mu$ m –sized NMOS transistor biased to 200  $\mu$ A/ $\mu$ m current density at 60 GHz. The small-signal model, including the gate and drain

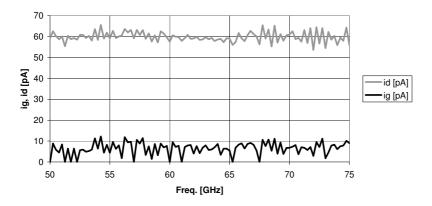

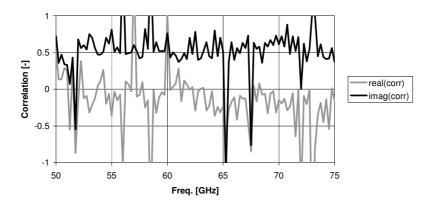

noise sources, is presented in figure 22. After removing the effect of the test structures and the extrinsic parasitics, the values for the noise sources and their correlation are presented in figures 23 and 24, respectively.

Fig. 21. The minimum noise figure (a), maximum stable gain (b) and optimum noise input match with available gain circles (c) are plotted for a 90  $\mu m$  NMOS transistor in 65-nm CMOS at V-band. The transistor drain current density is 0.2 mA/ $\mu m$ . (© 2008 IEEE, with permission from [Publication V]).

Fig. 22. The transistor model with the noise sources.

Fig. 23. The calculated gate and drain noise sources.

Fig. 24. The calculated correlation between the gate and drain noise sources.

#### 3.3 Comparison to experimental amplifier results

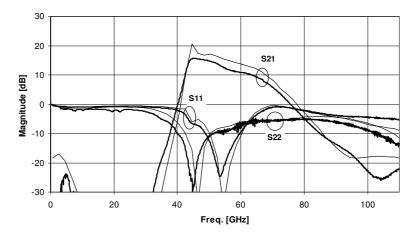

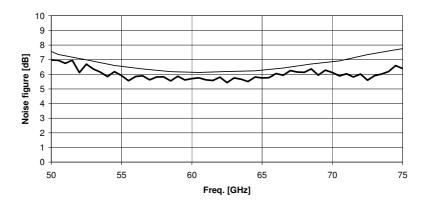

As an example, simulations from three different amplifier designs are presented in this section. The results were simulated using the transistor small-signal model that was described in the previous section. The first version of the 60-GHz amplifier was manufactured in the same process run as the transistor test structures that were used for the transistor modeling [Publication V]. The second version of the 60-GHz amplifier and a 100-GHz amplifier were manufactured in a later process run [Publication III][Publication VI]. These circuits were designed by Mikko Varonen and Dan Sandström and the author re-simulated them using the presented transistor model. From figures 25-30 it is possible to see, how the modeled values match quite well with the measured results in the case of versions 1 and 2 of the 60-GHz amplifier as well as that of the 100-GHz amplifier. Version 1 of the 60-GHz amplifier experienced an unexpected gain spike,

which vanishes with a lower transconductance. However, the amplifiers from the later process run (version 2 of the 60-GHz amplifier and the 100-GHz amplifier) can have transistors that have a higher transconductance. This result can be explained with run-to-run variations.

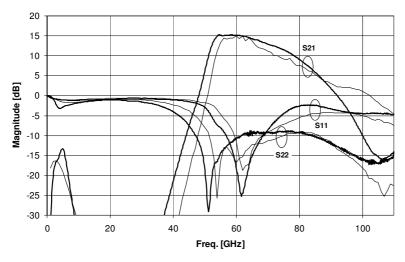

Fig. 25. Simulated (thin) and measured (thick) S11, S22, and S21 are plotted from 10 MHz to 110 GHz for the version 1 of the 60-GHz amplifier.

Fig. 26. Simulated (thin) and measured (thick) noise figures are plotted from 50 to 75 GHz for the version 1 of the 60-GHz amplifier.

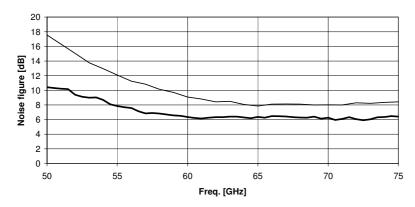

Fig. 27. Simulated (thin) and measured (thick) S11, S22, and S21 are plotted from 10 MHz to 110 GHz for the version 2 of the 60-GHz amplifier.

Fig. 28. Simulated (thin) and measured (thick) noise figures are plotted from 50 to 75 GHz for the version 2 of the 60-GHz amplifier.

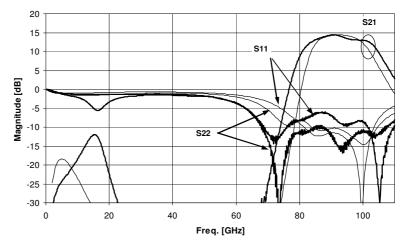

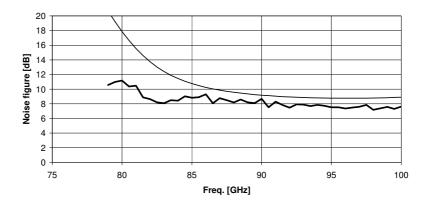

Fig. 29. Simulated (thin) and measured (thick) S11, S22, and S21 are plotted from 10 MHz to 110 GHz for the 100-GHz amplifier.

Fig. 30. Simulated (thin) and measured (thick) noise figures are plotted from 75 to 100 GHz for the 100-GHz amplifier.

# 4. Receiver system

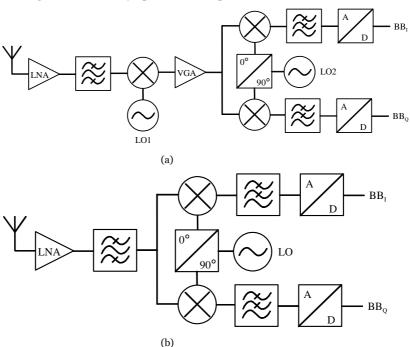

Two types of receiver front-ends are presented in figure 31. The superheterodyne and direct conversion techniques were developed approximately 100 years ago [37]-[41]. There are many ways to assess the performance of the receiver front-end, including the sensitivity and dynamic range that the receiver is capable of coping with and the level of interference that the receiver can tolerate. Power consumption can also be a limiting factor, if battery operation is required.

Fig. 31. Block diagrams of a receiver superheterodyne (a) and direct conversion (b) frontends.

# 4.1 Receiver front-end performance measures

The direct conversion architecture has certain benefits compared to the superheterodyne front-end. These include a single local oscillator, no IF

#### Receiver system

blocks, and DSB reception when both sidebands are in use. However, typically a direct conversion receiver requires an I/Q division for the local oscillator signal. This is particularly challenging at millimeter-wave frequencies [42]. Thus, it may be more practical to resort to a superheterodyne architecture with one intermediate frequency.

At millimeter-wave frequencies, there are difficulties in obtaining a low noise figure. This is further complicated by a mixer, in which additional noise originates from the image frequency; this can increase the overall noise figure and degrade the sensitivity in the case of the superheterodyne receiver. Even a reasonable level of image rejection can be difficult to achieve with on-chip millimeter-wave filters, since the integrated low quality passive components lead to poor performance. Thus, an image rejecting mixer may provide a solution to the image problem.

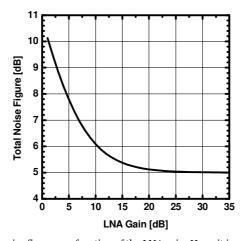

The analysis of receiver noise figures is well known [43]. An example of how LNA gain affects the system noise figure is presented in figure 32. The low gain from a single amplifier stage can easily lead to complex optimization problem. Figure 32 shows that a gain of 20 dB or more is required to make the contribution of the following receiver blocks insignificant in practice.

Fig. 32. The total noise figure as a function of the LNA gain. Here, it is assumed that the mixer following the LNA has a 10-dB conversion loss (and a 10-dB noise figure) and that the LNA noise figure is 5 dB.

### 4.2 Low-noise amplifier circuit design

When considering a suitable transistor for LNA design, the unit gate finger size is selected to maximize the gain ( $f_{max}$ , MSG) and minimize the noise figure [2]. NF<sub>min</sub> and MSG do not directly depend on the number of

transistor fingers and the number of transistors [44][45]. The drain current density for obtaining the optimum NF<sub>min</sub> or  $f_{max}$  [46] and related MAG [2] is the same irrespective of the technology node if constant field scaling is assumed. The total number of gate fingers and transistors in parallel are chosen so that the linearity requirements are fulfilled; additionally, they can be chosen if low  $R_n$  is required for insensitivity to source impedances and wideband noise matching are of importance.  $R_n$  and the  $|\Gamma|_{opt}$  are inversely proportional to the total gate width [44], which means that there will be a trade-off between noise insensitivity to source impedances (low  $R_n$ ), wideband noise matching (low  $|\Gamma|_{opt}$ ) and dc power consumption, while assuming a fixed unit finger width and a constant current density [47].

Because the lossless feedback network does not affect the minimum noise measure, power match and stability can typically be achieved by using inductive series feedback [48][49][50]. Of course, there should not be too much feedback, such that the system noise figure and the sensitivity would be affected or the number of stages required would be unpractical in terms of the circuit area and dc power consumption. Finally, the transistor is matched to the optimum noise measure  $M_{\rm opt}$  and the output is matched to the corresponding conjugate impedance [51][52]. A suitable number of stages can then be cascaded to obtain the specified total required LNA gain.

The feedback amplifiers and the inductive series feedback realized with a transmission line have been presented elsewhere ([53] and [54], respectively). Stability considerations are important when choosing the amount of feedback needed and the stability can be analyzed by using the stability factor and s-probe methods [55][56].

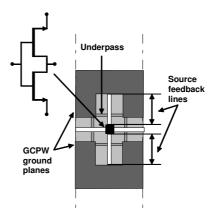

By using the methods described above, the transistor performance as a function of feedback is plotted in this work. The effect of the feedback line length is simulated from a structure that is presented in figure 33.

Fig. 33. The simulated transistor structure with transmission line feedback. Both lines have the same length. (© 2014 IEEE, with permission from [Publication XI]).

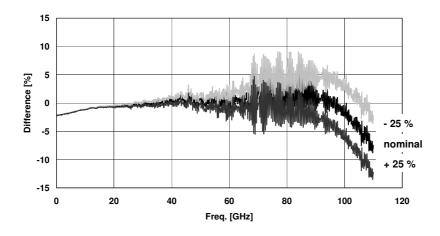

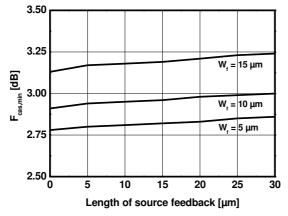

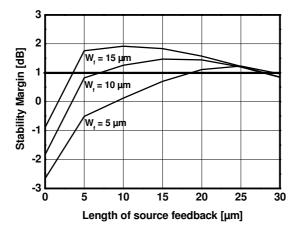

The results from simulations are shown in figures 34 and 35. The noise and gain performance of the transistor are in best balance for the 10  $\mu$ m unit finger width MHEMT and source feedback line lengths varying from 7 to 27  $\mu$ m at 183 GHz [Publication XI].

Fig. 34. The simulated  $F_{cas,min}$  of three different size two finger MHEMTs at 183 GHz and a drain current density of 400 mA/mm. (© 2014 IEEE, with permission from [Publication XI]).

Fig. 35. The simulated stability margin of three different size two finger MHEMTs at 183 GHz and a drain current density of 400 mA/mm. The margin is calculated as a difference between the gain of a transistor matched to the optimum noise measure and maximum stable gain (MSG). (© 2014 IEEE, with permission from [Publication XI]).

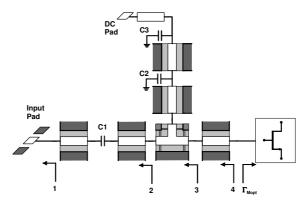

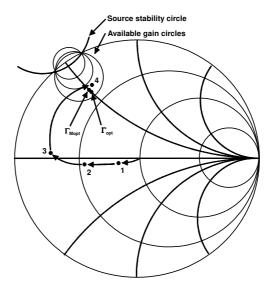

The input matching consists of several parts as shown in figure 36 and the corresponding reflection coefficients are shown in figure 37. A wide center conductor GCPW with a characteristic impedance of 30 ohms helps to bring the impedance closer to the optimum and it has lower loss compared to the other 50- and 70-ohm lines available in the design kit. The capacitors C1 and C2 have a small capacitance in order to provide a good short at the

center frequency, while the C3 capacitor is used for stabilizing the amplifier and decoupling the DC bias network from the rest of the amplifier [Publication XI].

Fig. 36. Low-noise amplifier input matching. ( $\circledcirc$  2014 IEEE, with permission from [Publication XI]).

Fig. 37. Low-noise amplifier input matching showing the impedances at different points of the network.  $\Gamma_{opt}$  shows the reflection coefficient for the minimum noise figure, while  $\Gamma_{Mopt}$  shows the corresponding reflection coefficient for the minimum noise measure. (© 2014 IEEE, with permission from [Publication XI]).

# 4.3 Mixer circuit design

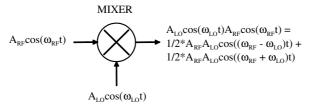

A mixer circuit is needed to convert information from one frequency to another. An active mixer may provide gain while a passive mixer has loss, which must to be compensated for with amplifiers to achieve the required gain. The basic mixing principle is presented in figure 38.

Fig. 38. The mixing principle.

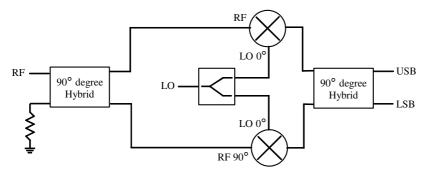

An image rejecting mixer can be used for image suppression [57]. A basic image rejection mixer is shown in figure 39.

Fig. 39. An image rejecting mixer.

The image rejection can then be calculated as follows:

$$IRR = \frac{1 + \Delta A^2 - 2\Delta A\cos(\theta)}{1 + \Delta A^2 + 2\Delta A\cos(\theta)},$$

(15)

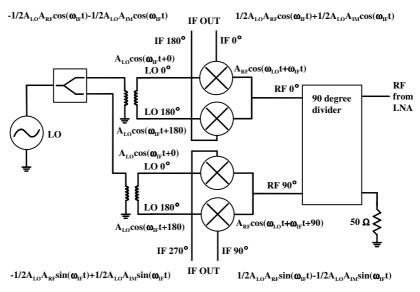

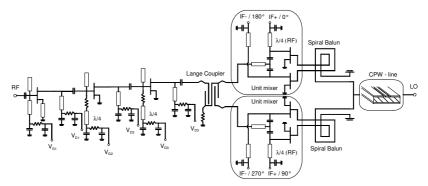

where  $\Delta A$  is the amplitude difference and  $\theta$  is the phase difference of the signals [58]. The LO-to-RF leakage can be reduced by using a balanced topology. If both the balanced LO input and image rejection are needed, then another mixer topology (fig. 40.) can be used. A similar configuration has been presented in a previous study [59] except that the LO balancing is different. Four unit mixers are needed: One pair of unit mixer provides the balancing and the other pair produces the image rejection. The IF output has four branches and the signal has four different phases. The 5.3-GHz IF signal combination can be performed with an external circuitry consisting of 180- and 90-degree hybrids. The image rejection depends mostly on the external connections and hybrids having narrow operating bandwidth because of the fact that the errors caused by the on-chip components to should be small and the relative bandwidth of the wanted signal is narrow. The effect of the hybrid network is presented in detail in chapter 5.

Fig. 40. Balanced image rejection mixer and signals in different branches.

#### 4.3.1 Active and passive mixers

One commonly used type of an active mixer is the Gilbert cell mixer and its variants [60][61]. The performance of the Gilbert mixer can be improved by providing a boost current to the transconductance stage. The current is fed through a short-circuited stub, which can be used to tune out the parasitic capacitance of the transistors [62]. The Gilbert cell mixer has drawbacks though, such as the non-grounded transistor bulk connection and voltage headroom. These issues can lead to increased threshold voltage and linearity problems. Typically the dynamic range of an active mixer is smaller than that of a passive mixer. As an example, there were two early attempts to realize active Gilbert type mixers operating at approximately 50–60 GHz both in GaAs PHEMT and CMOS technology [63][64].

Passive mixers can be created with diodes or resistive FETs as mixing components. A resistive FET mixer uses the characteristics related to the resistive channel of a transistor for frequency conversion. A resistive FET mixer can be realized by applying the LO to the gate, the RF to the drain and filtering the IF from the drain. Because there is no dc voltage at the drain, this type of a mixer is called a resistive mixer. The transistor gate is biased with a proper dc voltage. Usually a voltage near the threshold of the transistor is suitable for the gate bias. This type of a mixer has various advantages: Distortion is quite low due to the linear channel of the resistive FET, there is no shot noise and the 1/f-noise level is low [65][66].

# Receiver system

In this study, a passive FET mixer is used in the case of the 0.15-µm GaAs PHEMT receiver front-end, while the 65-nm CMOS receiver front-end has an active mixer [Publication VII][Publication XII][Publication XIII].

# 5. Measurement techniques

Most of the scattering parameter measurements were carried out using a HP8510C vector network analyzer with extension modules for the W-band. The measurements in the range of 140-200 GHz were measured using a HP8510B network analyzer with extension modules for the G-band (140-220 GHz). Picoprobe model 220 probes in a GSG configuration with a pitch of 75-µm were used for the RF input and output pads. These measurements were carried out at the MilliLab using a Cascade model 42 probe station. Sometimes, an external attenuator was needed to reduce the input power of the analyzer and to ensure the linear operation of the amplifiers. Unfortunately, this leads to a higher measurement uncertainty for the input port return loss.

The noise figure and insertion gain in the range of 141-212 GHz were measured using a noise figure analyzer and a noise diode. The V-band and W-band noise parameter measurement systems have been described elsewhere ([36] and [67], respectively). An analysis of the uncertainty of the noise measurement system shows a 0.37-dB variation for the minimum noise figure of a test transistor at the V-band, when using a 95 % confidence level [68].

In this work the noise figure of the CMOS radio front-end was measured in two separate ways. The first measurement was done at MilliLab using a noise figure analyzer and it produced the values for the double sideband noise figure. The second measurement was done by the author using a spectrum analyzer and by integrating the noise power level over the IF bandwidth. This requires information on the gain of the front-end. By using the gain values for the selected sideband, the corresponding single sideband noise figure can be calculated as follows:

$$F = \frac{S_{IN}/N_{IN}}{S_{OUT}/N_{OUT}} = \frac{N_{OUT}}{GkTB},$$

(16)

## Measurement techniques

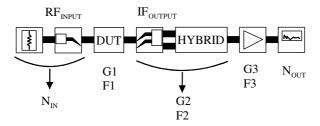

where  $S_{\rm IN}$  and  $S_{\rm OUT}$  are the input and output signals,  $N_{\rm IN}$  and  $N_{\rm OUT}$  are the corresponding noise powers, G is power gain, T is the temperature of the input termination and B is bandwidth. The noise measurement setup is presented in figure 41. The obtained noise figure is the total value while the effect of the IF hybrid has to be subtracted to calculate the noise figure of the front-end, as in equation 17.

Fig. 41. The receiver front-end measurement setup.

$$F_{1} = \frac{N_{OUT}}{G_{1}G_{2}G_{3}kTB} - \frac{F_{2} - 1}{G_{1}} - \frac{F_{3} - 1}{G_{1}G_{2}},$$

(17)

where  $G_X$ ,  $F_X$ ,  $N_{OUT}$  and  $N_{IN}$  = kTB refer to the measurement setup in figure 41.

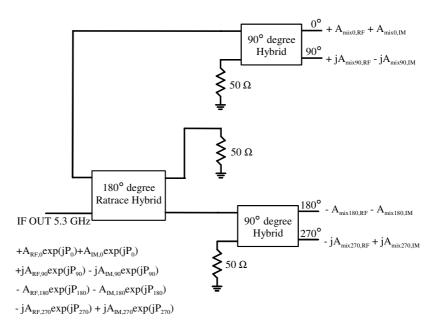

In the case of the passive mixer and GaAs front-end, the designed IF hybrids significantly affect the image rejection ratio [Publication VII][Publication XII]. The IF hybrids have been designed for a frequency of 5.3 GHz and they only have a narrow bandwidth where they operate accurately. The configuration of the hybrids in presented in figure 42.

Fig. 42. The hybrid configuration for combining the four phase IF signal.

The effect of the hybrid network on image rejection can be calculated as follows:

$$IRR = \frac{P_{IM}}{P_{RF}} = \frac{\left( |IF_{OUT,IM,TOTAL}| / \sqrt{2} \right)^2 / Z_0}{\left( |IF_{OUT,RF,TOTAL}| / \sqrt{2} \right)^2 / Z_0} = \frac{\left| |IF_{OUT,IM,TOTAL}| \right|^2}{\left| |IF_{OUT,RF,TOTAL}| \right|^2};$$

(18)

then, the image and RF signals can be calculated as

$|IF_{OUT,IM,TOTAL}|^2 =$

$$(A_0 \cos(P_0) + A_{90} \sin(P_{90}) - A_{180} \cos(P_{180}) - A_{270} \sin(P_{270}))^2 + (A_0 \sin(P_0) - A_{90} \cos(P_{90}) - A_{180} \sin(P_{180}) + A_{270} \cos(P_{270}))^2,$$

(19)

and

$|IF_{OUT,RF,TOTAL}|^2 =$

$$(A_0 \cos(P_0) - A_{90} \sin(P_{90}) - A_{180} \cos(P_{180}) + A_{270} \sin(P_{270}))^2 + (A_0 \sin(P_0) + A_{90} \cos(P_{90}) - A_{180} \sin(P_{180}) - A_{270} \cos(P_{270}))^2,$$

(20)

where  $A_x$  is the amplitude and  $P_x$  is the phase of the corresponding branch of the hybrid network. The final IRR is then

$$IRR_{dB} = 10 \cdot \log_{10} \left( \frac{\left| IF_{OUT,IM,TOTAL} \right|^2}{\left| IF_{OUT,RF,TOTAL} \right|^2} \right). \tag{21}$$

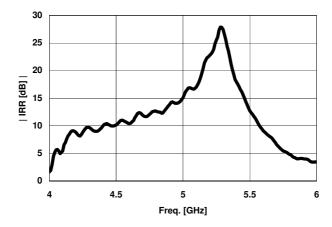

Finally, the calculated image rejection ratio can be plotted as in figure 43.

Fig. 43. The calculated image rejection ratio.

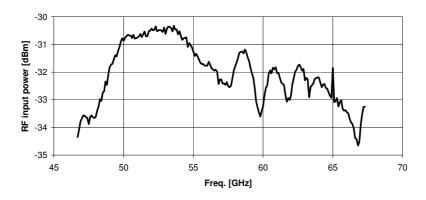

A suitable signal source was needed for the downconversion measurements. Typically, a frequency multiplier is used and the power level can be adjusted with an attenuator. However, the multiplier and attenuator system has a significant frequency response that needs to be characterized accurately. The measured input power is shown in figure 44.

Fig. 44. The measured input power from a frequency quadrubler and an attenuator connected together. The range of the measurement is from 46.7 to 67.3 GHz.

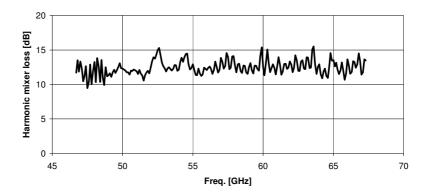

The spectrum measurements at around the V-band require a harmonic mixer to convert the signal into a suitable IF frequency for the analyzer. The harmonic mixer has a significant loss that needs to be characterized over the desired frequency range. The measured result from the harmonic mixer measurement is presented in figure 45.

Fig. 45. The measured loss of the harmonic mixer from 46.7 to 67.3 GHz.

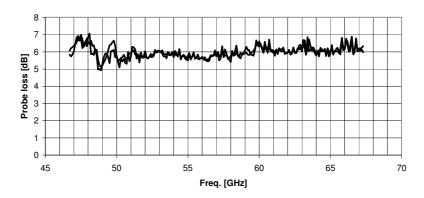

The probes have to be characterized as well at the selected frequency range. The results from two back-to-back probe measurements are presented in figure 46.

Fig. 46. Two separate back-to-back probe loss measurements. The two measurements were performed to check the consistency of the probe contact.

Measurement techniques

# 6. Integrated millimeter-wave amplifiers

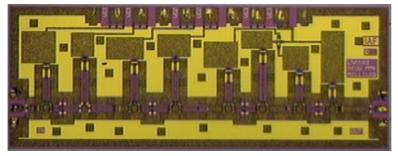

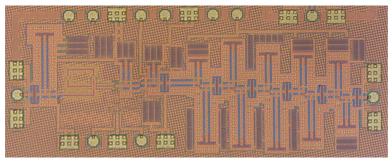

This chapter describes experimental results from several integrated millimeter-wave amplifiers designed in this work. The operating frequencies vary from 94 to 183 GHz and the circuits have been realized both in 100-nm and 50-nm technologies. The circuits are aimed at a cloud profiling radar application, in which sensitivity is a major performance limiting factor. All circuit models for the active and passive components were provided by the Fraunhofer IAF. The circuit topology is based on grounded coplanar waveguides.

## 6.1 94-GHz amplifier

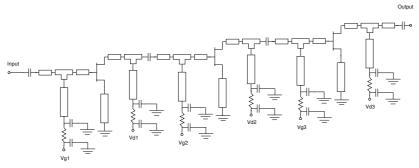

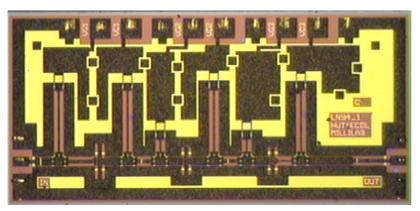

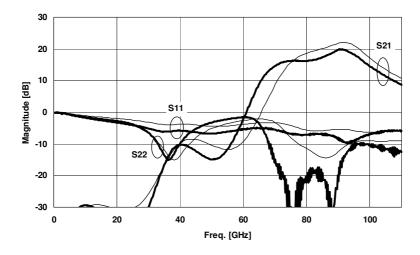

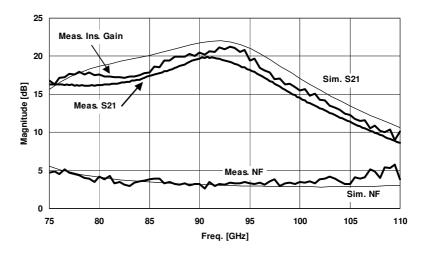

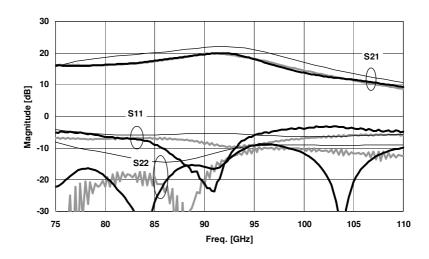

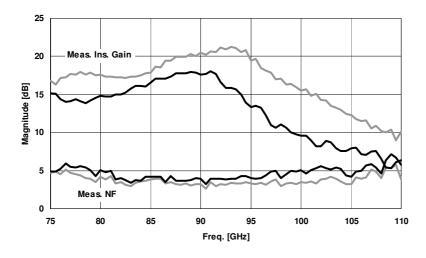

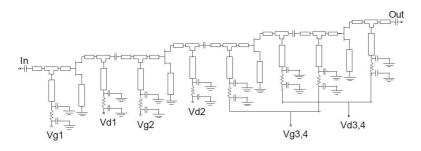

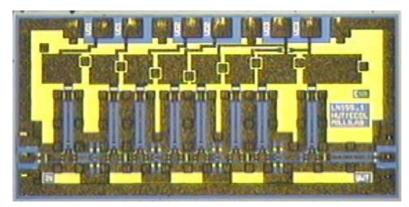

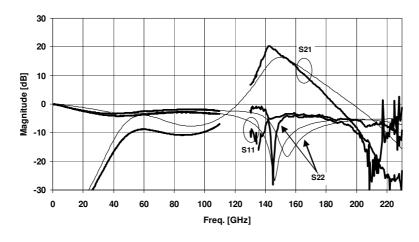

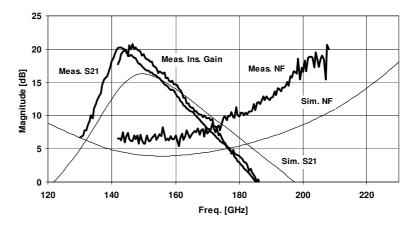

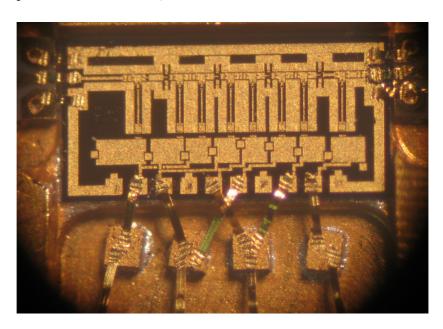

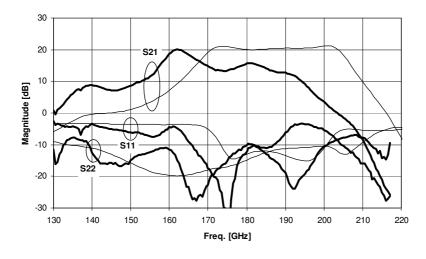

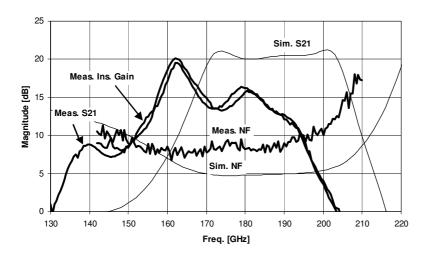

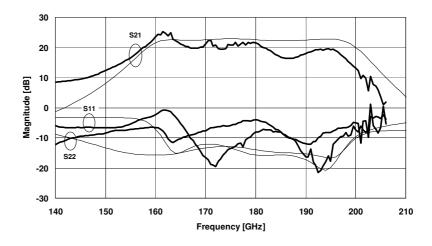

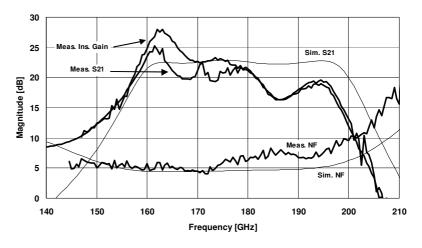

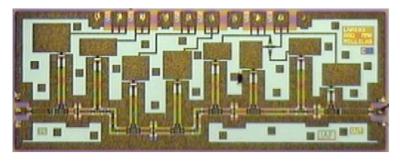

A 94 GHz amplifier was designed in 100-nm GaAs metamorphic HEMT technology from Fraunhofer IAF [Publication VIII][Publication IX]. A simplified schematic of the amplifier is presented in figure 47. The design is based on grounded coplanar transmission lines. The source feedback was primarily used for transistor stabilization. This four-stage design achieved an 18-dB gain and a 3.1-dB noise figure at 94 GHz. The micrograph and measured results are presented in figures 48, 49, and 50. The measured values were in good agreement with the simulated s-parameters. The S<sub>22</sub> experienced the largest difference and the gain shifted slightly downward in frequency. The simulated noise figure was quite close to the measured value up to 100 GHz.

Fig. 47. A simplified schematic of the low-noise amplifier. (© 2007 EuMA, with permission from [Publication IX]).

Fig. 48. A micrograph of the 94-GHz amplifier. The chip size is 2.0 x 1.5 mm². (© 2006 EuMA, with permission from [Publication VIII]).

Fig. 49. The measured and simulated s-parameters of the 94-GHz amplifier.

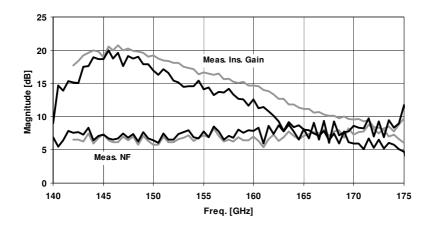

Fig. 50. The measured and simulated noise figure of the 94-GHz amplifier. The measured insertion gain is also plotted.

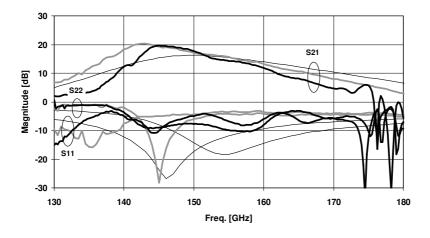

The 94-GHz amplifier was assembled in a split block package and the measured results are presented in figures 51 and 52. The packaged chip has almost the same  $S_{21}$  results as it had on-wafer, but the  $S_{11}$  and  $S_{22}$  showed more variations. The insertion gain showed more differences, as was to be expected. This was caused by the relatively poor input matching and the source impedance of the noise source. The on-wafer result is compared to other published results in table 3.

Fig. 51. Measured s-parameters of the packaged 94-GHz amplifier. The on-wafer results are drawn with thick gray lines and while the simulated values are drawn with thin lines.

Fig. 52. Measured noise figure of the packaged 94-GHz amplifier. The on-wafer results are drawn with thick gray lines.

Table 3. A comparison of some published amplifiers at 94 GHz.

| Freq.<br>[GHz] | Stages | Gain<br>[dB] | NF<br>[dB] | Topology    | Technology         | Chip size [mm²] | Ref. |

|----------------|--------|--------------|------------|-------------|--------------------|-----------------|------|

| 94             | 2      | 16.2         | 10.6       | Cascode     | 0.25 μm SiGe       | 0.28            | [69] |

| 85-99          | 3      | 33           | 3.2-3.5    | Cascode     | 0.13 μm InP HEMT   | 2.75            | [70] |

| 94             | 1      | 12           | 2.3        | Cascode     | 0.07 μm GaAs MHEMT | 1.00            | [71] |

| 94             | 5      | 6.4          | -          | Distributed | 0.1 μm InP HEMT    | 0.34            | [72] |

| 94             | 2      | 11           | 4.7        | -           | 0.1 μm GaAs PHEMT  | 2.64            | [73] |

| 80-100         | 4      | 27           | 5          | CS          | 0.1 μm InP HEMT    | 4.20            | [74] |

| 77-101         | 4      | 45           | 6-8.3      | Cascode     | 0.13 μm SiGe       | 0.77            | [75] |

| 82-101         | 2      | 10.8         | -          | CS          | 0.1 μm GaAs MHEMT  | 4.08            | [76] |